(完整word版)跨导运算放大器的设计

- 格式:doc

- 大小:308.00 KB

- 文档页数:19

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

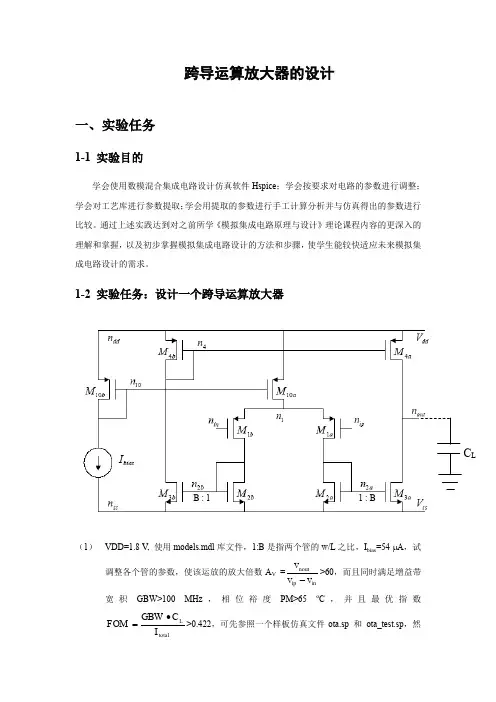

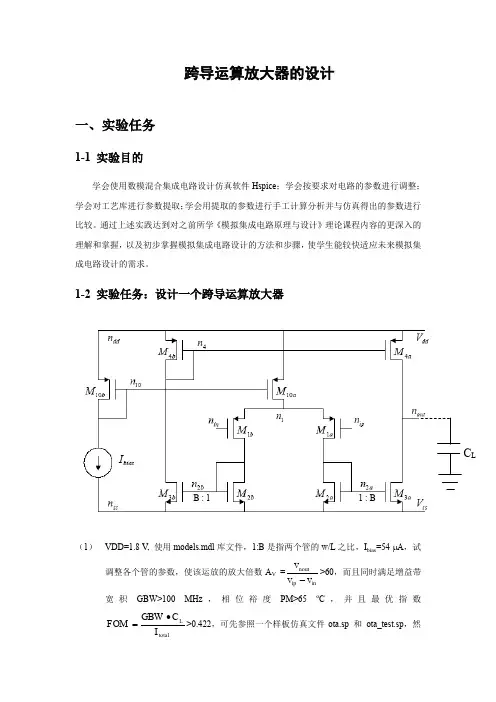

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V , 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54 μA ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 oC ,并且最优指数totalLI C GBW FOM ∙=>0.422,可先参照一个样板仿真文件ota.sp 和 ota_test.sp,然C LB : 1 1 : B后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较; (3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少? 最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

跨导放大器的设计考虑

采用电压反馈放大器(VFA) 来设计一个优质的电流到电压(跨导放大器) 转换器是一项重大的挑战。

本文将会探讨一个用345 MHz 的轨到轨输出,电压反馈放大器(例如是美国国家半导体的LMH6611)来实现的简单TIA 设计,并提供TIA 设计所必需的信息,讨论TIA 的补偿和性能结果,以及分析TIA 输出端的噪声。

由于LMH6611 工作在较大增益(RF) 时,其输入偏置电流便较低,故可容许电路工作在低光强度的条件下。

运算放大器反向端上的总电容(Cr) 包括光二极管的电容(CPD) 和输入电容(CIN),Cr 在电路稳定性方面扮演着很重要的角色,而稳定性则取决于这个电路的噪声增益(NG),其定义为:

为了保持稳定性,需要加入一个反馈电容(CF) 与RF 并联以便在噪声增益函数中的fP 处构建一个极点。

通过选用合适容值的CF,便可使噪声增益的斜坡变平从而获取最佳的性能,这样使得频率fP 点的噪声增益等于运算放大器的开环增益。

这个在AOL 和噪声增益交点以上的噪声增益斜率平坦化会得到一个45 度的相位余量(PM)。

这是因为在交点处,fP 点的噪声增益极点会贡献一个45 度的相位超前,因此给出了一个45 度的相位余量(假设fP 和fZ 之间最少有10 MHz 的距离)。

公式3 和4 理论上可计算出CF 的最优值和期望的-3 dB 带宽:。

模拟集成电路实验——跨导放大器设计实验报告学院:电信学院班级:微电子23班姓名:游晓东学号:2120503069一、设计指标二、电路结构确定电路结构的原因: ① 根据设计指标② 电路结构对称,匹配度高,,Offset CMRR 性能指标好③ 电路稳定性好,只有一个主极点④ 该电路为差分输入,单端输出,共模抑制比大,输出共模点较稳定三、电路原理概述该电路主要由三部分组成:带隙基准电流源、偏置电路、跨导放大器9~21M M 构成一个跨导放大器,其中13M 为尾电流源,向输入的差动对管提供电流偏置。

11,12M M 为输入差分对管,将小信号电压转换成小信号电流。

9,14M M 和10,17M M 为两个对称的电流镜,比例复制小信号电流。

14,15M M 与16,17M M 为共源共栅结构,可以提高输出阻抗和开环增益。

18,19,20,21M M M M 为低压共源共栅电流镜,可以作为单端输出并且提高输出摆幅。

0~8M M 构成偏置电路部分,为跨导放大器提供偏置电流。

22~34,0~2,0~2M M Q Q R R 构成带隙基准电流源部分,为电路提供基准电流源。

四、设计过程1. 分配电流根据静态电流250A μ限制,分配带隙基准电流源部分20A μ,偏置电路部分10A μ(其中每一路2A μ),跨导放大器部分210A μ。

分配14,17M M 的偏置电流14M I 时主要考虑三个指标:,,GBW SR GMGM 要求900~1100/A V μ,因此GM 取1000/A V μ。

由于11GM B gm =⋅,B为14,9M M 的偏置电流之比,因此111000/B gm A V μ⋅= (1)GBW 要求大于3MHZ 。

112LB gm GBWC π⋅=⋅,因此11566/B gm A V μ⋅> (2)SR 要求大于3/V S μ。

92M LB I SRC ⋅=,因此9290M B I A μ⋅> (3)由于9112M ODI gm V =,若OD V 取0.2V ,则由(1)得9100M B I A μ⋅=,由(2)得956.6M B I A μ⋅>,由(3)得945M B I A μ⋅>。

课程设计报告设计课题:CMOS二级密勒补偿运算放大器的设计姓名:XXX专业:集成电路设计与集成系统学号:1115103004日期2015年1月17日指导教XXX师:国立华侨大学信息科学与工程学院一:CMOS二级密勒补偿运算放大器的设计1:电路结构最基本的CMOS二级密勒补偿运算跨导放大器的结构如下图,主要包括四部分:第一级PMOS输入对管差分放大电路,第二级共源放大电路,偏置电路和相位补偿电路.2:电路描述:输入级放大电路由M1~M5组成。

M1和M2组成PMOS差分输入对管,差分输入与单端输入相比可以有效抑制共模信号干扰;M3和M4为电流镜有源负载;M5为第一级放大电路提供恒定偏置电流.输出级放大电路由M6和M7组成,M6为共源放大器,M7为其提供恒定偏置电流同时作为第二级输出负载。

偏置电路由M8~M13和Rb组成,这是一个共源共栅电流源,M8和M9宽长比相同.M12和M13相比,源级加入了电阻Rb,组成微电流源,产生电流Ib。

对称的M11和M12构成共源共栅结构,减少了沟道长度调制效应造成的电流误差。

在提供偏置电流的同时,还为M14栅极提供偏置电压。

相位补偿电路由M14和Cc组成,M14工作在线性区,可等效为一个电阻,与电容Cc一起跨接在第二级输入输出之间,构成RC密勒补偿。

3:两级运放主体电路设计由于第一级差分输入对管M1与M2相同,有R1表示第一级输出电阻,其值为则第一级的电压增益对第二级,有第二级的电压增益故总的直流开环电压增益为所以4:偏置电路设计偏置电路由M8~M13 构成,其中包括两个故意失配的晶体管M12 和M13,电阻RB 串联在M12 的源极,它决定着偏置电流和gm12,所以一般为片外电阻以保证其精确稳定。

为了最大程度的降低M12 的沟道长度调制效应,采用了Cascode 连接的M10以及用与其匹配的二极管连接的M11 来提供M10 的偏置电压。

最后,由匹配的PMOS器件M8 和M9 构成的镜像电流源将电流IB 复制到M11 和M13,同时也为M5 和M7提供偏置。

目录1 引言 (1)2 软件介绍 (3)3 运算放大器设计基础 (5)3.1运放的主要性能指标 (5)3.2运算放大器的基本结构 (6)3.2.1全差分运放 (6)3.2.2套筒式结构 (7)3.2.3折叠式结构 (8)4 系统总体设计 (10)4.1电路设计的整体结构 (10)4.2 主放大电路设计 (11)4.3 偏置电路的设计 (13)4.4 输出级的设计 (13)4.5 共模反馈的设计 (14)4.6 总体布局 (15)5 仿真与分析 (17)5.1运放直流与交流特性 (17)5.2噪声特性分析 (19)5.3电源抑制比 (19)5.4设计指标 (20)5.5放大器参数 (21)6 版图设计与分析 (22)6.1 L-Edit介绍 (22)6.2版图设计规则 (22)6.3基本器件版图设计 (23)6.3.1 NMOS版图设计 (23)6.3.2 电容电阻版图设计 (24)6.4版图的总体设计 (26)6.4.1主电路模块版图 (26)6.4.2偏置模块版图 (27)6.4.3输出模块版图 (27)6.4.4整体模块版图 (28)6.5 LVS版图比对 (29)7 结论 (31)谢辞 ................................................................................................... 错误!未定义书签。

参考文献 .. (32)附录1 (33)附录2 (35)1 引言集成运算放大器(Integrated Operational Amplifier)简称集成运放,是由多个CMOS管与电容电阻通过耦合方式实现提高增益的模拟集成电路[1]。

集成运放具有增益高、输入阻抗大、输出阻抗低、共模抑制比高和失调与漂移性小等优点,而且当输入电压值为零时,输出值也为零。

集成运放是构成常用集成电路系统的通用模块[2] [3]。

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V , 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54 μA ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 oC ,并且最优指数totalLI C GBW FOM ∙=>0.422,可先参照一个样板仿真文件ota.sp 和 ota_test.sp,然C LB : 1 1 : B后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较; (3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少? 最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

CMOS 级运算放大器设计(东南大学集成电路学院)一.运算放大器概述运算放大器是一个能将两个输入电压之差放大并输出的集成电路。

运算放大器是模拟电子技术中最常见的电路,在某种程度上,可以把它看成一个类似于BJT或FET的电子器件。

它是许多模拟系统和混合信号系统中的重要组成部分。

它的主要参数包括:开环增益、单位增益带宽、相位阈度、输入阻抗、输入偏流、失调电压、漂移、噪声、输入共模与差模范围、输出驱动能力、建立时间与压摆率、CMRR、PSRR以及功耗等。

二.设计目标1.电路结构最基本的COMS二级密勒补偿运算跨导放大器的结构如图 1.1所示。

主要包括四部分:第一级输入级放大电路、第二级放大电路、偏置电路和相位补偿电路。

图1.1两级运放电路图2.电路描述电路由两级放大器组成,M1~M4构成有源负载的差分放大器,M5提供该放大器的工作电流。

M6、M7管构成共源放大电路,作为运放的输出级。

M6提供给M7的工作电流。

M8~M13组成的偏置电路,提供整个放大器的工作电流。

相位补偿电路由M14和Cc构成。

M14工作在线性区,可等效为一个电阻,与电容Cc 一起跨接在第二级输入输出之间,构成 RC密勒补偿。

3■设计指标两级运放的相关设计指标如表1。

三.电路设计第一级的电压增益:A l =G mi R, = g m2 (r o2 11 r o4) (3.1)第二级电压增益:A2 = -G m2R^ - g m6 (r o6 H r o7) (3.2) 所以直流开环电压增益:A o — Al A2 ~ —g m2 g m6 (r o2 || r o4 )( r o6 || r o7) (3.3)单位增益带宽:G B WA O f^-gm122 c (3.4)表1两级运放设计指标偏置电流:、2R C g m6 = (W/L)14Y (W 儿)131.2g m1以上公式推导过程简略,具体过程可参考相关专业书籍。

根据这些公式关系,2根据系统失调电压:转换速率:相位补偿:■KP n (W/L)i2R ; J (W/L) (W/L)12 1(3.5)(W/L)3 (W/L)4 1(W/L)5 (W/L)6(W/L)62(W/L)7SR = min *1DS5 1DS7 — 1DS5C cC L(3.6)(3.7)(W/L)6 ((W/L)11 _ g m6 +[(3.8)四.HSPICE 仿真.title test.lib E:\h05mixddst02v231.lib tt vdd vdd 0 5 vss vss 0 0.subckt opamp vn vp out vdd vss m1 2 vn 1 1 mp w=120u l=1u m2 3 vp 1 1 mp w=120u l=1u m3 2 2 vss vss mn w=40u l=1u m4 3 2 VSS vss mn w=40u l=1u m5 1 6 vdd vdd mp w=16u l=1u m6 out 3 vss vss mn w=160u l=1u m7 out 6 vdd vdd mp w=32u l=1u * bias circuit m8 6 6 vdd vdd mp w=3.2u l=1u m9 7 6 vdd vdd mp w=3.2u l=1u m10 6 7 8 vss mn w=6u l=1u m11 7 7 9 vss mn w=6u l=1u m12 8 9 10 vss mn w=24u l=1u m13 9 9 vss vss mn w=6u l=1u rb 10 vss 6k* miller cc 4 out 1.5 p cl out vss 3pm14 4 7 3 vss mn w=20u l=1u .en dsx1 vn vp out vdd vss opamp x2 vp vpout1 vdd vss opamp x3 out2 vi out2 vdd vss opamp x4 vn vn out3 vdc vss opampx5 vn vn out4 vdd vsc opamp vp vp 0 dc 2.5 ac 1 vn vn 0 dc 2.5 vi vi 0 p ulse(2 3 20ns 0.1 ns 0.1 ns 200ns 400ns)根据已经计算好的器件参数,写成电路网表。

2.1 CMOS模拟集成电路基本单元2.1.1 MOS场效应管的基本结构绝缘栅场效应管又叫作MOS场效应管,意为金属-氧化物-半导体场效应管。

图2.1为MOS场效应管的结构和电路符号。

图中的N型硅衬底是杂质浓度低的N型硅薄片。

在它上面再制作两个相距很近的P区,分别引为漏极和源极,而由金属铝构成的栅极则是通过二氧化硅绝缘层与N型衬底及P型区隔离。

这也是绝缘栅MOS场效应管名称的由来。

因为栅极与其它电极隔离,所以栅极是利用感应电荷的多少来改变导电沟道去控制漏源电流的。

MOS场效应管的导电沟道由半导体表面场效应形成。

栅极加有负电压,而N型衬底加有正电压。

由于铝栅极和N型衬底间电场的作用,使绝缘层下面的N型衬底表面的电子被排斥,而带正电的空穴被吸引到表面上来。

于是在N型衬底的表面薄层形成空穴型号的P型层,称为反型层,它把漏源两极的P区连接起来,构成漏源间的导电沟道。

沟道的宽窄由电场强弱控制。

MOS场效应管的栅极与源极绝缘,基本不存在栅极电流,输入电阻非常高。

[20,21]图2.1MOS场效应管的结构和电路符号Fig.2.1 Structure and circuit symbol that MOS Field-Effect Transistor 场效应管有P型和N型之分。

这里的P型或N型,指的是导电沟道是P型还是N 型,即导电沟道中是空穴导电还是电子导电。

因为场效应管中只有一种载流子参加导电,所以又常称为“单极型晶体管”。

P型沟道和N型沟道的MOS场效应管又各分为“耗尽型”和“增强型”两种。

耗尽型指栅极电压为零时,就存在导电沟道,漏源中间有一定电流。

增强型MOS场效应管,则只有在栅极电压大于零的情况下,才存在导电沟道。

2.1.2 MOS场效应管的模型化MOS管的大信号(直流)特性可以用它的电流方程来描述。

以N沟道增强型MOS管为例,特性曲线和电流方程如图2.2所示。

图2.2 特性曲线和电流方程Fig.2.2 Characteristic property curve and electric current equation如果栅源偏置电压GS V 大于MOS 管的阈值电压T V ,则在P 型衬底的表面由于静电感应会产生大量的电子,形成导电沟道。

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V , 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54 μA ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 o C,并且最优指数totalLI C GBW FOM •=>0.422,可先参照一个样板仿真文件ota.sp 和 ota_test.sp ,然C LB : 1 1 : B后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较; (3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少? 最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

模拟集成电路课程设计跨导放大器学院:电信学院班级:微电子92组长:曾云霖(09053057)组员:黄雄(09053042)蒋仪(09053043)跨导放大器设计设计题目:基于所给的CMOS工艺设计一款跨导放大器.跨导放大器的特点是具有非常大的输出阻抗,将输入电压转换成电流输出,相当于压控电流源。

该电路的设计同样需要包括偏置电压电流产生电路。

设计指标:设计指标:(供参考)性能参数测试条件参数指标负载电容30pF电源电压范围 2.5~5.5V静态电流VDD=3。

6V,Temp=27℃〈250μA输出摆幅输入共模电压VDD =3。

6V,Temp=27℃VDD =3。

6V,Temp=27℃0.6~1。

2V0。

1~1V开环增益(低频)VDD =3。

6V,Temp=27℃1800~2200单位增益带宽VDD =3。

6V,Temp=27℃>3MHz相位裕度VDD =3。

6V,Temp=27℃〉60°PSRR(低频)VDD =3。

6V,Temp=27℃>65dB跨导(低频)VDD =3.6V,Temp=27℃(900~1100)μA /V 转换速率VDD =3。

6V,Temp=27℃>3V/μs设计要求:1.确定设计指标(以上指标供参考,可以进行适当修改,但需说明原因); 2.根据设计指标,可以在参考电路结构基础上确定参数和改进设计,也可以查找文献采用其它结构的电路或创造新的电路结构进行设计;3.阅读模型文件,了解可以选用的器件类型与尺寸范围;4.手工设计:根据拟定的设计指标,初步确定满足指标的各元件的模型与参数:MOS:沟道长度与宽度,并联个数;电阻:宽度、长度、串并联个数;电容:宽度、长度、并联个数;三极管:并联个数.5.采用全典型模型,27℃,验证电路是否满足设计指标;6.设计偏置电路:a)选定电路结构;b) 手工设计:确定各元件的模型与尺寸;c)采用全典型模型,仿真验证偏置电流源的性能;7.将偏置电路和主体电路合在一起仿真,采用全典型模型,27℃,VDD=3.6V,要求电路达到“设计指标"要求,否则应对电路结构和参数进行修改与优化,直至满足要求(可能需要多次调整),并应包括以下内容:a)一输入端固定为0。

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V, 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54A ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 o C ,并且最优指数totalLI C GBW FOM •=>0.422,可先参照一个样板仿真文件ota.sp 和C LB : 1 1 : Bota_test.sp ,然后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较;(3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少?最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

•增益带宽积GBW由12d out L f R C π=out m V BR g A 10=102m V d L g B GBW A f C π==因为C L 的值不变,所以理论上提高M3和M2的沟道宽长比之比B 、增大M1的跨导即增大M1的宽长比可以增大GBW ,且满足增益的要求。

• 相位裕度PM该电路中,nout 为主极点,CL 不变,所以输出电阻Rout 变化会使主极点发生变化。

M2和M3之间的点N2a 为第一非主极点,所以通过改变M2M3的W/L 之比,通过使第一非主极点的位置外移,进而可以改变相位裕度。

但是,改变管子参数的同时,总会伴随增益或带宽的下降,所以,合理取值才是最重要的。

• 最优指数FOM由/L totalFOM GBW C I =⋅GBW 满足要求时,减小I total 值可以增大FOM因为I bias 为定值,所以若减少I total ,则需减小管子的尺寸但I total 跟GBW 具有一定的矛盾关系,且电流太小管子可能会进入截止状态。

即使能令MOS 管处于饱和状态,考虑实际情况,过驱动电压也不能太小。

2-1-2仿真结果2-1-3相关参数2-1-4计算参数C L=1.0386pI bias=54uAI total =254.4705uA V0 =62.111f d=1.1952MHzPM =70.629>65GBW=A V0 f d=62.111*1.7832=110.76>60total LI CGBW FOM •==0.45>0.422从输出文件中查得各管都工作在饱和区,符合要求。

由计算,可以证明实验参数符合指标要求。

2-2 问题22.2.1对NMOS管进行电路仿真测试并提取参数:NMOS管测试电路原理图漏端电压从0到1.8V以步进0.01进行扫描,同时,栅极电压从0到1V以步进0.05V进行扫描。

•源代码:(见附录1)•Nmos 取点:如下图,于各条曲线取斜率并选取点进行标记记下其横纵坐标及斜率,计算出VenL,如下表Vds/V Ids/uA Slope/u VenL0.9202.5922.232-8.21250.95236.7627.735-7.58651.0272.5634.357-6.9332 Avg-7.5774VenL=-7.57743.2.2对PMOS管进行电路仿真测试并提取参数:PMOS管测试电路原理图•源代码:(见附录二)•Pmos 取点:方法同NmosVds/V Ids/uA Slope/u VepL-0.9-23.130.9073124.5929-0.95-28.5560.6895840.4607-1.0-34.4910.5156865.8845 Avg-28.72643.6460VepL=43.64602-2-3 手算分析用实验1的管子参数,由手算分析等到理论值,与实验1的仿真值相比较。

Vgs=-1V仿真后显示其阈值电压Vth=-0.481V 忽略沟道调制效应 此时Ids=-34.9058uA由得pmos 的μCox 为51.835u带入m g其中I d1=27uA W 1/L 1=5.0 / 0.18 得g m1=278.841u A/VM3和M2的沟道宽长比之比B=(W3/L3)/(W2/L2)= (5.5/1.0)/(2.0/1.0)=2.75 输出电阻R o3=VenL3/(B*I d1)=92.92K Ω R o4=VepL4/(B*I d1)=587.81K Ω Rout=Ro3//Ro4=80.24K Ω已知C L =1.0386p2))(/(21th gs ox d V V L W C I -=μ得到f d =1/(2π*R out *C L )=1.9098MHz由out m V BR g A 10得到Av =61.5292-2-4 误差分析1. 1m g 的误差较大,原因是沟道调制效应等二阶效应导致的。

计算的过程中只考虑了一阶模型,忽略了很多二阶效应,计算模型简略导致1m g 的计算产生误差。

2.f d 的结果受到电阻值的影响,由于电阻值较小,则f d 的值相对偏大,且具有一定误差。

3.Av 的值受到1m gf d 的误差影响。

4.三个参数的误差大小与计算VENL 和VEPL 时的取点有关。

2-3 问题32-3-1仿真结果2-3-2相关参数2-3-3 计算参数C=1.0386pFLI bias=13uAA V0 =70.009f d=1.4924MHzPM =65.409>65GBW=70.009*65.409=104.4814MHz>100MHzI= 88.3776uAtotalFOM =*LtotalGBW C I =1.2278>0.422从输出文件中查得各管都工作在饱和区,符合要求。

由计算,可以证明实验参数符合指标要求。

且FOM 的值约为1,较符合优化设计要求。

四、附录附录1:NMOS 参数提取电路源代码.subckt ota nd ng ns************** * parameters * ************** .param wmin=0.24u .param lmin=0.18u.param l1=1.0u .param w1=5.5u*********** * circuit * ***********m1 nd ng ns ns n_18_g2 l=l1 w=w1 geo=3 m=1.ends otaA test structure for the ota******************** The model-files ********************.include models.mdl************ Options ************.option method=gear.option reltol=1e-5 abstol=1e-9 .option post********************* Include circuits *********************.include './ota_extract.sp'*************** parameters ***************.param cl=1.0386p.param ibias1=54u************ circuit ************xota nd ng nss otar1 ndd nd 1k* the equivalent load capacitance cl nout nss cl************ sources ************* dc sourcesvdd ndd 0 1.8vss nss 0 0vg ng nss 1**************** simulations ***************** operating point.op.dc vdd 0 1.8 0.01 vg 0 1 0.05*********** output ************.probe dc v(*).end附录二:PMOS参数提取电路源代码.subckt ota nd ng ns*************** parameters ***************.param wmin=0.24u.param lmin=0.18u.param l1=1u.param w1=5u************ circuit ************m1 nd ng ns ns p_18_g2 l=l1 w=w1 geo=3 m=1.ends otaA test structure for the ota******************** The model-files ********************.include models.mdl************ Options ************.option method=gear.option reltol=1e-5 abstol=1e-9 .option post********************* Include circuits *********************.include './ota_extract.sp'*************** parameters ***************.param cl=1.0386p.param ibias1=54u************ circuit ************xota nd ng nss otar1 ndd nd 1k* the equivalent load capacitance cl nout nss cl************ sources ************* dc sourcesvdd ndd 0 -1.8vss nss 0 0vg ng nss -1**************** simulations ***************** operating point.op.dc vdd -1.8 0 0.01 vg -1 0 0.05 ********** * output * ********** *.probe dc v(*) .end附录3: 参数提取及计算所用参考公式)(/(21)1())(/(212gs ox d th gs ox d V L W C I V V L W C I μμ-=-=44433343,||)/(2d EP o d EN o o o out d ox m I LV r I L V r r r R I L W C g ====μV ds-V E L(or -1/λ) dE d ds ds ds ds o E I L V I V I I V r LV ===∂∂=∂∂==λλ1/11Lm d V Lout d out m V C B g f A GBW C R f BR g A ππ2211010====。