数字集成电路设计-组合逻辑电路

- 格式:ppt

- 大小:6.60 MB

- 文档页数:139

数字集成电路设计基础

1. 数字逻辑

•布尔代数

•组合逻辑电路

•时序逻辑电路

•状态机

2. CMOS 技术

•CMOS 器件的结构和特性•MOS 晶体管的开关特性•CMOS 逻辑门

•CMOS 存储器

3. 数字集成电路设计流程

•系统规范

•架构设计

•逻辑设计

•物理设计

•验证和测试

4. 组合逻辑电路设计

•门级优化

•多级逻辑优化

•可编程逻辑器件 (FPGA)

5. 时序逻辑电路设计

•时钟和复位电路

•触发器和锁存器

•同步和异步时序电路

6. 存储器设计

•静态随机存取存储器 (SRAM) •动态随机存取存储器 (DRAM) •只读存储器 (ROM)

•闪存

7. 芯片设计中的布局和布线

•布局约束和规则•布线算法

•时序和功耗优化8. 验证和测试

•功能验证

•时序验证

•制造测试

9. 数字集成电路应用•微处理器和单片机•数字信号处理•通信系统

•嵌入式系统

其他重要概念:

•数制转换

•可靠性和容错性•EDA 工具

•低功耗设计

•可制造性设计。

数字集成电路-电路系统与设计第二版课程设计

一、课程设计介绍

数字集成电路是现代电路设计中的重要组成部分,也是计算机科学与工程的重要分支。

本课程设计旨在通过对数字集成电路的系统与设计进行探究,并结合具体的案例来设计和实现数字集成电路,使学生能够熟悉数字集成电路的基本原理、设计方法和实现技术。

本课程设计主要包含以下内容:

1.数值系统和编码

2.逻辑功能设计:组合逻辑电路和时序逻辑电路

3.集成电路设计方法和流程

4.VHDL和FPGA实现数字逻辑电路

5.数字信号处理器

通过本次课程设计,学生将掌握数字集成电路的系统性设计思路和实现方法,具备数字电路设计的基本能力和实际操作技术,能够针对具体应用场景提出解决方案,实现数字电路的设计、验证和调试。

二、课程设计要求

1. 课程设计题目

本次课程设计的题目为“4位计数器设计”。

2. 软件工具

VHDL编程软件和EDA工具

1。

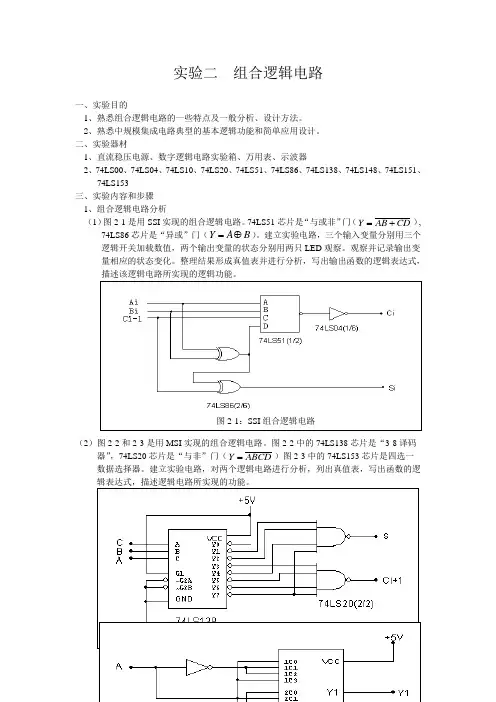

实验二 组合逻辑电路一、实验目的1、熟悉组合逻辑电路的一些特点及一般分析、设计方法。

2、熟悉中规模集成电路典型的基本逻辑功能和简单应用设计。

二、实验器材1、直流稳压电源、数字逻辑电路实验箱、万用表、示波器2、74LS00、74LS04、74LS10、74LS20、74LS51、74LS86、74LS138、74LS148、74LS151、 74LS153三、实验内容和步骤 1、组合逻辑电路分析(1)图2-1是用SSI 实现的组合逻辑电路。

74LS51芯片是“与或非”门(CD AB Y +=), 74LS86芯片是“异或”门(B A Y ⊕=)。

建立实验电路,三个输入变量分别用三个 逻辑开关加载数值,两个输出变量的状态分别用两只LED 观察。

观察并记录输出变 量相应的状态变化。

整理结果形成真值表并进行分析,写出输出函数的逻辑表达式, 描述该逻辑电路所实现的逻辑功能。

(2)图2-2和2-3是用MSI 实现的组合逻辑电路。

图2-2中的74LS138芯片是“3-8译码 器”,74LS20芯片是“与非”门(ABCD Y =)图2-3中的74LS153芯片是四选一 数据选择器。

建立实验电路,对两个逻辑电路进行分析,列出真值表,写出函数的逻 辑表达式,描述逻辑电路所实现的功能。

图2-1:SSI 组合逻辑电路图2-2 :MSI 组合逻辑电路(74LS138)2、组合逻辑电路设计(1)SSI 逻辑门电路设计——裁判表决电路举重比赛有三名裁判:一个主裁判A 、两个副裁判B 和C 。

在杠铃是否完全举起裁 决中,最终结果取决于至少两名裁判的裁决,其中必须要有主裁判。

如果最终的裁决 为杠铃举起成功,则输出“有效”指示灯亮,否则杠铃举起失败。

(2)MSI 逻辑器件设计——路灯控制电路用74LS151芯片和逻辑门,设计一个路灯控制电路,要求能够在四个不同的地方都 能任意的开灯和关灯。

四、实验结果、电路分析及电路设计方案1、组合逻辑电路分析 (1)图2-1: 逻辑表达式:)()(11i i i i i i i i i i B A C S B A C B A C ⊕⊕=⊕+=--逻辑功能:实现A i 、B i 、C i-1三个一位二进制数 的加法运算功能,即全加器。

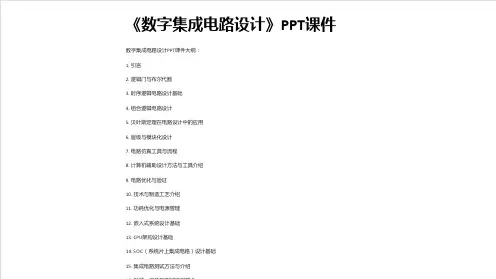

数字集成电路:电路系统与设计(第二版)简介《数字集成电路:电路系统与设计(第二版)》是一本介绍数字集成电路的基本原理和设计方法的教材。

本书的内容覆盖了数字电路的基础知识、逻辑门电路、组合逻辑电路、时序逻辑电路、存储器和程序控制电路等方面。

通过学习本书,读者可以了解数字集成电路的概念、设计方法和实际应用。

目录1.数字电路基础知识 1.1 数字电路的基本概念 1.2 二进制系统与数制转换 1.3 逻辑运算与布尔代数2.逻辑门电路 2.1 与门、或门、非门 2.2 与非门、或非门、异或门 2.3 多输入门电路的设计方法3.组合逻辑电路 3.1 组合逻辑电路的基本原理 3.2 组合逻辑电路的设计方法 3.3 编码器和译码器4.时序逻辑电路 4.1 时序逻辑电路的基本原理 4.2 同步时序电路的设计方法 4.3 异步时序电路的设计方法5.存储器电路 5.1 存储器的基本概念 5.2 可读写存储器的设计方法 5.3 只读存储器的设计方法6.程序控制电路 6.1 程序控制电路的基本概念 6.2 程序控制电路的设计方法 6.3 微程序控制器的设计方法内容概述1. 数字电路基础知识本章主要介绍数字电路的基本概念,包括数字电路与模拟电路的区别、数字信号的表示方法以及数制转换等内容。

此外,还介绍了数字电路中常用的逻辑运算和布尔代数的基本原理。

2. 逻辑门电路逻辑门电路是数字电路中的基本组成单元,本章主要介绍了与门、或门、非门以及与非门、或非门、异或门等逻辑门的基本原理和组成。

此外,还介绍了多输入门电路的设计方法,以及逻辑门电路在数字电路设计中的应用。

3. 组合逻辑电路组合逻辑电路是由逻辑门电路组成的,本章主要介绍了组合逻辑电路的基本原理和设计方法。

此外,还介绍了编码器和译码器的原理和应用,以及在数字电路设计中的实际应用场景。

4. 时序逻辑电路时序逻辑电路是在组合逻辑电路的基础上引入了时序元件并进行时序控制的电路。

本章主要介绍了时序逻辑电路的基本原理和设计方法,包括同步时序电路和异步时序电路的设计。

华中科技大学《电子线路设计、测试与实验》实验报告实验名称:SSI组合逻辑电路设计实验(软件)院(系):自动化学院实验成绩:指导教师:汪小燕2014 年 4 月24 日一.实验目的1.掌握用SSI(小规模数字集成电路)实现简单组合逻辑电路的方法。

2.掌握简单数字电路的安装于调试技术。

3.进一步熟悉数字万用表、示波器等仪器的使用办法。

4.熟悉用Verilog HDL描述组合逻辑电路的方法,以及EDA仿真技术。

二.实验元器件芯片74HC00 2片,74LS04 一片;若干导线,计算机;QuartusⅡ9.1集成开发环境;面包板;可编程器件实验板;专用的在系统编程电缆。

三.实验原理及参考电路组合逻辑电路的设计流程组合逻辑电路的设计步骤如下图,先根据实际的逻辑问题进行逻辑抽象,定义逻辑状态的含义,在按照给定事件因果关系列出逻辑关系真值表。

然后用给定的器件实现简化后的逻辑表达式,画出逻辑电路图。

QuartusⅡ9.1在设计好电路之后,就可以根据设计的电路,就可以在QuartusⅡ9.1集成开发环境下,通过Verilog HDL语言编程,然后生成相应的波形文件执行仿真,最后再把程序下载到老师给的DE0板子上去,从而通过板子上LED灯的亮和不亮来确定输出的高低电平。

插板在做完仿真之后,就可以根据设计的逻辑图选择相应的芯片进行插板,通过给不同输入高低电平组合来测输出电平的高低,从而检测是否符合实验要求。

四.实验内容全加器/全减器 根据给定的器件,设计一个全加器/全减器电路,使之既能实现1位加法运算又能实现1位减法运算。

当控制变量M=0时,电路实现加法运算;当M=1时,电路实现减法运算。

其框图如下所示,图中,00A B 、 分别为被加(减)数和加(减数),0S 为相加(减)的结果,0C 为进(借)位。

一、 首先,按照组合逻辑电路的设计流程,写出其真值表如下:M0A0B1C -0S0C0 0 0 0 0 0 0 0 0 1 1 0 0 0 1 0 1 0 0 0 1 1 0 1 0 1 0 0 1 0 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 1 1 1 1 0 0 0 0 0 1 0 0 1 1 1 1 0 1 0 1 1 1 0 1 1 0 1 1 1 0 0 1 0 1 1 0 1 0 0 1 1 1 0 0 0 111111二、根据真值表,。

组合逻辑电路的设计方法

一、设计步骤

根据给出的实际逻辑问题,求出实现该实际问题的逻辑功能的组合逻辑电路,这就是组合逻辑电路设计的任务。

在使用不同的器件进行设计时,电路的“最简”也有不同的含意。

用小规模数字集成电路进行设计的最简标准是所用的门数目最少,而且门的输出端数目也最少;用中规模数字集成电路进行设计的最简标准是所用集成电路个数最少,品种最少,同时集成电路间的连线也最少。

组合逻辑电路设计的一般步骤如下:

按照设计要求列出真值表;

根据题意设输入变量和输出函数并逻辑赋值,确定它们相互间的关系,然后将输入变量以自然二进制数顺序的各种取值组合排列,列出真值表。

2.根据真值表,写出输出逻辑函数表达式;3.对输出逻辑函数进行化简,可采用代数法或卡诺图法;4.根据最简输出逻辑函数式画出逻辑图。

二、设计举例

【例】设计一个A、B、C三人表决电路。

当表决某个提案时,多数人同意,提案通过,同时A具有否决权。

用与非门实现。

解:设计步骤(1)列出真值表设A、B、C三个人,表决同意用1表示,不同

意时用0表示;Y为表决结果,提案通过用1表示,通不过用0表示;同时还应考虑A具有否决权。

输入

输出

A B C

Y

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

1

1

1

(2)写出输出函数表达式并化简得:Y=AB+AC (3)画逻辑图。

一、页组合逻辑电路分析与设计实验报告二、目录1.页2.目录3.摘要4.背景和现状分析4.1逻辑电路的基础概念4.2组合逻辑电路的应用领域4.3当前组合逻辑电路设计的挑战5.项目目标5.1实验目的和预期成果5.2技术和方法论5.3创新点和实际应用6.章节一:逻辑门和基本组合电路7.章节二:组合逻辑电路的设计方法8.章节三:实验操作和数据分析9.章节四:实验结果和讨论10.结论与建议三、摘要四、背景和现状分析4.1逻辑电路的基础概念逻辑电路是数字电路的基本组成部分,它们执行基本的逻辑运算,如与、或、非等。

组合逻辑电路(CLC)是由多个逻辑门组成的电路,其输出仅取决于当前输入的组合,而与电路以前的状态无关。

这种电路广泛应用于各种电子设备中,从计算机处理器到简单的电子玩具。

4.2组合逻辑电路的应用领域组合逻辑电路在现代技术中扮演着关键角色。

它们是计算机处理器、数字信号处理器、通信设备和其他许多电子系统的基础。

随着技术的进步,组合逻辑电路的设计和应用也在不断扩展,例如在、物联网和高速通信领域。

4.3当前组合逻辑电路设计的挑战尽管组合逻辑电路的设计原理相对简单,但在实际应用中面临着一系列挑战。

这些挑战包括提高电路的速度和效率、减少能耗、以及设计更复杂的逻辑功能。

随着集成电路尺寸的不断缩小,量子效应和热效应也对电路的设计和性能提出了新的挑战。

五、项目目标5.1实验目的和预期成果本实验的主要目的是深入理解和掌握组合逻辑电路的设计原理和实验方法。

预期成果包括成功设计和实现一个具有特定功能的组合逻辑电路,并对其进行性能分析。

5.2技术和方法论实验将采用现代电子设计自动化(EDA)工具进行电路设计和仿真。

实验方法将包括理论分析、电路设计、仿真测试和性能评估。

5.3创新点和实际应用本实验的创新点在于探索新的设计方法和优化技术,以提高组合逻辑电路的性能和效率。

实验成果将有望应用于实际电子产品的设计和开发,特别是在需要高性能和低功耗的场合。