数字逻辑4-3-3组合电路中的险象消除

- 格式:ppt

- 大小:445.50 KB

- 文档页数:12

毕业论文关于数字电路竞争-冒险现象的研究学专关于数字电路竞争-冒险现象的研究摘要:随着科学技术的发展,数字电路在实际应用中起到了举足轻重的作用,例如PLD、FPGA等。

本文介绍了竞争冒险的概念及产生的原因。

就数字电路中出现的竞争冒险问题及解决办法,从理论和实践的角度对其进行了总结归纳,并举例分析了判别竞争冒险的方法和消除方法,提出人们在分析设计数字电路时要根据不同的电路情况采用不同的分析、判别和消除方法。

在数字系统设计和调试中,常产生传输延迟、竞争冒险、毛刺干扰等问题,这是传统仪器和消除方法无法解决的,在这种情况下出现了适用于软、硬件分析的新的测试、消除竞争与冒险现象的方法。

准确的实现系统功能是每一个系统设计者追求的最终目标,面对越来越庞大的系统设计,设计者需要更加完善、准确地检测出竞争与冒险现象,这样才能保证设计的准确性。

本论文在对国内外有关竞争与冒险现象的发展现状的研究上,还进一步对冒险现象新的检测、消除技术和基于FPGA的虚拟逻辑分析仪进行了分析和研究。

关键词:竞争冒险,数字电路,检测技术,逻辑分析仪Research and Analysis on Race and Competition in Digital Circuit DesignAbstract:The digital circuits play a pivotal role in the practical application with the development of science and technology, For example, PLD, FPGA, etc. This paper proposes an experiment analysis on an enhanced algorithm of MVFDS. There are three part s in this paper, the first one is the introduction of features of the system, the second one is the process of experiment s which are conducted to verify the performance of the enhanced system. The third one is the conclusions and possible further improvements are discussed.Many problems are caused during designing or debugging the digital system,which include the transmission delay,the competition risk,the interference of burrs and so on. They can not be resolved by traditional instruments. In this situation,a new type of digital domain testing instrument named logic analyzer is made to analyze hardware and software,which can effectively solve these problems caused in the digital system. System evaluation is very important to a digital system designer. In order to complete a precise system, digital engineer should give the system evaluation as early as possible. This thesis has researched the virtual logic analyzer based on FPGA to let more users use it,which bases on researching virtual instrument technology,FPGA technology and USB interface.Key words:Race and Competition,Digital Circuit,Detection Technique,Logic Analyzer目录1 引言 (1)1.1课题背景 (1)1.2国内外的研究现状及发展趋势 (1)1.3本课题的任务及研究意义 (4)2 相关理论知识介绍 (5)2.1竞争与冒险的现象 (5)2.2竞争与冒险的分类 (5)3 组合逻辑电路竞争与冒险 (6)3.1组合电路中产生竞争冒险的原因和分析 (6)3.2组合逻辑电路中竞争冒险的消除方法 (7)4 时序逻辑电路竞争与冒险 (11)4.1时序逻辑电路中产生竞争冒险的原因和分析 (11)4.2时序逻辑电路中竞争冒险的消除方法 (13)5 可编程逻辑电路的竞争与冒险 (15)5.1可编程逻辑器件概述 (15)5.2FPGA的开发过程 (16)5.3FPGA器件中产生竞争冒险的原因和分析 (17)5.4FPGA中竞争与冒险的消除方法 (18)6 数字电路竞争与冒险的最新成果分析 (21)6.1关于数字电路检测、设计技术 (21)6.1.1 冒险检测技术与无冒险电路设计的研究意义 (21)6.1.2 冒险检测技术与无冒险电路设计的研究现状 (21)6.1.2 主要研究成果 (21)6.2关于竞争与冒险的检测仪器 (25)6.2.1 逻辑检测仪的研究意义 (25)6.2.2 逻辑检测仪的研究现状 (26)6.2.3 主要研究成果 (27)7 结论 (30)参考文献 (31)致谢 (33)1 引言1.1 课题背景随着计算机科学与技术突飞猛进地发展,用数字电路进行信号处理的优势也更加突出。

数字电路中冒险的检测及消除摘要:冒险是数字电路设计中不正确设计导致的。

本文简要介绍了数字电路中冒险的检测及消除的常用方法。

关键词:数字电路,冒险、检测、消除The checkout and elimination of static-hazard in digital circuit Abstract:The hazard is the wrong design of digital design. In this article, we will introduce the way to find static-hazard and the solution to the problem.Key words:digital circuit, hazard, checkout, eliminate由于电路延迟,逻辑电路的瞬态特性(transient behavior)可能与稳态分析得到的不同。

特别是,在稳态分析下的不变输出可能会产生短脉冲,常常称为尖峰或闪烁。

若电路可能存在尖峰,就说它存在冒险(hazard);或者是由于信号在传输和处理过程中经过不同的逻辑门、触发器或逻辑单元时产生时差,造成信号的原变量和反变量状态改变的时刻不一致,产生错误瞬间。

根据电路输出的使用情况,系统的操作可能会受到某些突变的假信号的不利影响,这种假信号竞争就可能造成冒险。

冒险现象可能将直接影响电路工作的稳定性、可靠性,甚至会导致整个数字系统的错误动作和逻辑紊乱。

因此,如何解决竞争冒险问题就成为数字电路设计中非常关键的环节。

冒险分为静态冒险和动态冒险。

本文中我们主要讨论静态冒险。

静态冒险分为静态1型冒险和静态0型冒险。

静态1型冒险是指在对电路功能的稳态分析后,期望输出保持良好的静态1时,电路的输出可能会产生0尖峰的可能性;静态0型冒险是指当预期电路有静态0输出时却存在产生1尖峰的可能性。

一、冒险的检测消除冒险,首先需要检测出冒险。

一、概述组合逻辑电路竞争冒险是数字电路设计中常见的问题之一。

它指的是在时序条件下,由于输入信号的变化导致电路输出出现不确定的转换过程,可能造成电路性能下降甚至失效的情况。

消除组合逻辑电路竞争冒险,对于保证电路的可靠性和稳定性具有重要意义。

本文将探讨消除组合逻辑电路竞争冒险的方法。

二、理解组合逻辑电路竞争冒险1.1 组合逻辑电路组合逻辑电路是由逻辑门组成的电路,其输出仅由输入确定的逻辑方程确定,没有状态存储。

典型的组合逻辑电路包括加法器、比较器、译码器等。

1.2 竞争冒险竞争冒险是指在时序条件下,由于输入信号的变化导致电路输出出现不确定的转换过程。

在组合逻辑电路中,竞争冒险可能导致输出信号的瞬时不稳定,从而影响整个电路的功能和性能。

三、消除组合逻辑电路竞争冒险的方法2.1 时序优化设计通过时序优化设计,可以使电路在特定的时间限制内完成逻辑运算,减少竞争冒险的可能性。

时序优化设计包括信号调整、信号同步和时钟分配等技术手段。

2.2 信号同步技术信号同步技术通过控制信号的传输路径和延迟时间,使得输入信号在逻辑运算之前到达,从而避免竞争冒险。

常见的信号同步技术包括流水线技术、同步触发器技术和反馈路径控制技术。

2.3 逻辑优化设计逻辑优化设计可以通过优化逻辑方程、简化逻辑结构等方式,减少竞争冒险的可能性。

逻辑优化设计常常需要依靠专业的逻辑综合工具进行辅助。

2.4 时钟分配技术时钟分配技术可以根据电路的工作频率和时序要求,合理设计时钟信号的分配和布局,避免时钟冲突和竞争冒险。

时钟分配技术需要考虑时钟的传输延迟、时钟的峰值功耗和时钟的抖动等因素。

2.5 引入冗余逻辑通过引入冗余逻辑,可以在一定程度上提高电路的容错能力,从而减少竞争冒险的可能性。

冗余逻辑可以是备用逻辑单元、冗余逻辑判断器或冗余逻辑运算器等。

2.6 仿真验证通过仿真验证,可以对组合逻辑电路进行全面、深入的测试,发现潜在的竞争冒险问题,并及时进行修正。

数字电路与逻辑设计第三版侯建军答案第四章1.什么是组合逻辑电路? 组合逻辑电路的结构有什么特点?答:如果一个逻辑电路在任何时刻产生的稳定输出仅取决于该时刻各输入取值的组合,而与过去的输入取值无关,则称该电路为组合逻辑电路。

从电路结构看,组合逻辑电路具有如下两个特点:①电路由逻辑门电路组成,不包含任何记忆原件。

②电路中信号是单向传输的,不存在任何反馈回路。

2.组合逻辑电路中的竞争现象是什么原因引起的? 竞争可以分为哪几种类型?答:组合逻辑电路中的竞争现象可以广义的定义为多个信号到达某一点有时差所引起的现象。

把不产生错误输出的竞争称为非临界竞争,而导致错误输出的竞争称为临界竞争。

3.组合逻辑电路中的险象一般以什么形式出现? 有哪些常用的处理方法?答:组合电路中的险象是一种瞬态现象, 它表现为在输出端产生不应有的尖脉冲, 暂时地破坏正常逻辑关系。

处理方法有:①增加冗余项消除险象②增加惯性延时环节滤除险象③引入选通脉冲避开险象4.二进制并行加法器按其进位方式的不同可分为哪两种类型?答:按其进位方式的不同, 可分为串行进位二进制并行加法器和超前进位二进制并行加法器两种类型。

5.二进制并行加法器采用超前进位的目的是什么?答:简化电路结构,提高加法器的运算速度。

6.二进制译码器的基本功能是什么? 74138 的输出与输入构成何种关系?答:二进制译码器的基本功能是将 n个输入变量变换成2n个输出函数,且输出函数与输入变量构成的最小项具有对应关系。

74138是一种3输入8输出译码器,其输出为输入变量构成的最小项之非。

7.多路选择器的基本功能是什么?答:多路选择器(Multiplexer)又称为数据选择器或多路开关, 常用 MUX 表示。

它是一种多路输入、单路输出的组合逻辑电路, 其逻辑功能是从多路输人数据中选中一路送至数据输出端, 输出对输入的选择受选择控制变量控制。

8.判断图4.44所示逻辑电路, 请问当输人变量取何值时 3 个电路输出取值相同?答:由输出函数表达式可知,当输入变量取值相同时,3个电路输出取值相同。

数字电路中冒险的检测及消除摘要:冒险是数字电路设计中不正确设计导致的。

本文简要介绍了数字电路中冒险的检测及消除的常用方法。

关键词:数字电路,冒险、检测、消除The checkout and elimination of static-hazard in digital circuit Abstract:The hazard is the wrong design of digital design. In this article, we will introduce the way to find static-hazard and the solution to the problem.Key words:digital circuit, hazard, checkout, eliminate由于电路延迟,逻辑电路的瞬态特性(transient behavior)可能与稳态分析得到的不同。

特别是,在稳态分析下的不变输出可能会产生短脉冲,常常称为尖峰或闪烁。

若电路可能存在尖峰,就说它存在冒险(hazard);或者是由于信号在传输和处理过程中经过不同的逻辑门、触发器或逻辑单元时产生时差,造成信号的原变量和反变量状态改变的时刻不一致,产生错误瞬间。

根据电路输出的使用情况,系统的操作可能会受到某些突变的假信号的不利影响,这种假信号竞争就可能造成冒险。

冒险现象可能将直接影响电路工作的稳定性、可靠性,甚至会导致整个数字系统的错误动作和逻辑紊乱。

因此,如何解决竞争冒险问题就成为数字电路设计中非常关键的环节。

冒险分为静态冒险和动态冒险。

本文中我们主要讨论静态冒险。

静态冒险分为静态1型冒险和静态0型冒险。

静态1型冒险是指在对电路功能的稳态分析后,期望输出保持良好的静态1时,电路的输出可能会产生0尖峰的可能性;静态0型冒险是指当预期电路有静态0输出时却存在产生1尖峰的可能性。

一、冒险的检测消除冒险,首先需要检测出冒险。

探索组合逻辑电路的竞争冒险现象及消除方法

组合逻辑电路是指一些由多个逻辑门组成的逻辑电路。

它们一般不具有记忆性,不涉及时钟信号,是根据输入信号直接输出结果的电路。

虽然组合逻辑电路看起来非常简单,但是在实际应用中存在着一些竞争冒险,这可能导致电路输出错误的结果。

本文将探讨组合逻辑电路的竞争冒险现象及消除方法。

竞争冒险是指当多个逻辑门的输入信号在不同的时间到达时,电路不能准确地确定输出信号。

这是由于电路中存在着多条不同的信号路径,当这些路径的信号到达的时间不同,就会发生竞争冒险。

这个现象如果不及时解决,就会导致电路输出错误的结果,甚至会使整个系统崩溃。

竞争冒险可以通过添加延迟元件来解决。

这些延迟元件包括反相器和缓冲器。

反相器可以改变输入信号的极性,并将输出信号延迟一定时间后输出。

缓冲器可以加强信号的强度,并将信号的延迟控制在很小的范围内。

通过添加这些延迟元件,可以精确地控制信号的延迟时间,从而避免竞争冒险。

另外,竞争冒险问题也可以通过优化电路结构来解决。

由于冒险问题是由信号路径的不同导致的,我们可以尽可能地减少信号路径的长度和数量。

在优化电路时,需要考虑到电路的性能和延迟时间之间的平衡。

如果性能过于复杂,就会增加信号延迟时间,从而导致冒险问题。

如果性能过于简单,就会降低电路的效率和稳定性。

总之,竞争冒险是组合逻辑电路中常见的问题之一。

通过添加

延迟元件和优化电路结构,可以有效地解决这个问题。

在实际应用中,我们必须注意电路的稳定性和效率,以便顺利地解决竞争冒险问题,保证电路的正确性。

组合逻辑电路竞争冒险现象消除方法仿真分析李烨【摘要】The competition risk phenomenon often appears in the process of working transformation of the combina-tional logic circuit.The competition risk can lead to the bad influence or even the logic chaos to the digital system. This paper takes the Multisim software as the platform for the virtual simulation experiments, and analyzes the basic method of eliminating the phenomenon of the competition risk.%组合逻辑电路在工作状态转换过程中经常会出现竞争冒险现象,竞争冒险会对数字系统产生不良影响甚至使其产生逻辑混乱。

以Multisim软件为平台进行虚拟的仿真实验,分析消除竞争冒险现象的基本方法。

【期刊名称】《镇江高专学报》【年(卷),期】2015(000)003【总页数】4页(P57-60)【关键词】竞争冒险;Multisim仿真;消除【作者】李烨【作者单位】江苏联合职业技术学院镇江分院机电工程系,江苏镇江 212016【正文语种】中文【中图分类】TN79组合逻辑电路的设计都是在输入、输出处于稳定的逻辑电平下进行的。

为了测试电路的抗干扰能力,保证组合逻辑系统的稳定,有必要对电路输入信号的逻辑电平瞬间变化时的工作状态进行分析。

在组合逻辑电路中,门电路两个输入信号同时向相反的逻辑电平跳变(一个从1变为0,另一个从0变为1)的现象称为竞争[1]。

此时,输出波形会出现违反原设计的尖脉冲波形,这种现象称为竞争冒险。

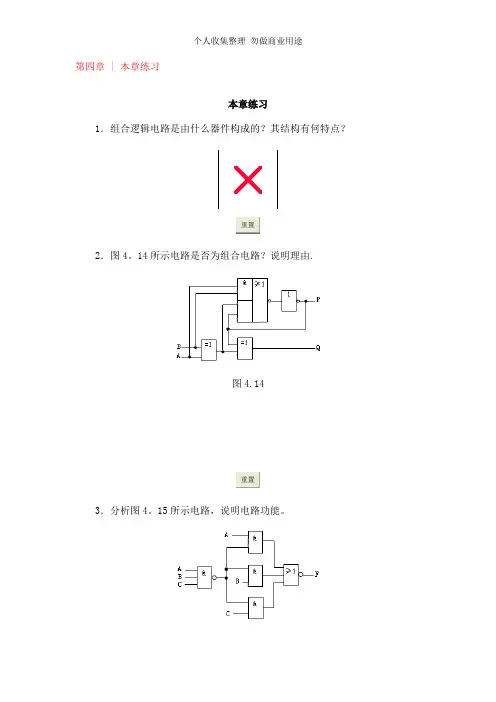

第四章 | 本章练习本章练习1.组合逻辑电路是由什么器件构成的?其结构有何特点?重置2.图4。

14所示电路是否为组合电路?说明理由.图4.14重置3.分析图4。

15所示电路,说明电路功能。

重置4.分析图4.16所示电路,试画出用异或门实现该电路功能的最简电路.图4.16重置5.分析图4.17所示电路,试列出真值表,说明电路功能.重置A B C D W X Y Z A B C D W X Y Z0 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 10 0 0 00 0 0 10 0 1 10 0 1 00 1 1 00 1 1 10 1 0 10 1 0 01 0 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 11 1 0 01 1 0 11 1 1 11 1 1 01 0 1 01 0 1 11 0 0 11 0 0 06.分析图4。

18所示电路,设输入ABCD为8421码,试列出真值表,说明电路功能。

图4.18重置A B C D W X Y Z A B C D W X Y Z0 0 0 0 1 0 0 1 0 1 0 1 0 1 0 07.设计一个组合逻辑电路,该电路输入端接收两个两位无符号二进制数A=A 1A 0和B=B 1B 0,当A=B 时,输出F 为1,否则F 为0。

试用合适的逻辑门构造出最简电路。

8.设计一个代码转换电路,将一位十进制数的8421码转换成余3码.9.用与非门设计一个组合逻辑电路,该电路输入为一位十进制数的2421码,当输入的数为素数时,输出F 为1,否则F 为0。

重置10.设计一个奇偶检测器,当输入的4位代码中1的个数为偶数时,输出为1,否则输出为0。

重置11.组合逻辑电路中产生竞争的原因是什么?竞争可以分为哪两种类型?重置12.什么叫组合逻辑电路中的险象?有哪几种消除险象的常用方法?。

实验四组合电路中的竞争与冒险姓名:班级:学号:实验时间:一、实验目的1、观察组合电路中的竞争与冒险现象。

2、了解消除竞争与冒险现象的方法。

二、实验仪器及器件1、数字电路实验箱、数字万用表、示波器。

2、74LS00、74LS20三、实验原理1、竞争冒险现象及其成因在组合逻辑电路中信号的传输可能通过不同的路径而汇合到某一门的输入端上。

由于门电路的传输延迟,各路信号对于汇合点会有一定的时差。

这种现象称为竞争。

这个时候如果电路的输出产生了错误输出,则称为逻辑冒险现象。

一般说来,在组合逻辑电路中,如果有两个或两个以上的信号参差地加到同一门的输入端,在门的输出端得到稳定的输出之前,可能出现短暂的,不是原设计要求的错误输出,其形状是一个宽度仅为时差的窄脉冲,通常称为尖峰脉冲或毛刺。

2、检查竞争冒险现象的方法在输入变量每次只有一个改变状态的简单情况下,如果输出门电路的两个输入信号A和是输入变量A经过两个不同的传输途径而来的,那么当输入变量的状态发生突变时输出端便有可能产生两个尖峰脉冲。

因此,只要输出端的逻辑函数在一定条件下化简成或则可判断存在竞争冒险。

3、消除竞争冒险现象的方法(1)接入滤波电路在输入端并接一个很小的滤波电容Cf,足可把尖峰脉冲的幅度削弱至门电中的阈值电压以下。

(2)引入选通脉冲对输出引进选通脉冲,避开险象。

(3)修改逻辑设计在逻辑函数化简选择乘积项时,按照判断组合电路是否存在竞争冒险的方法,选择使逻辑函数不会使逻辑函数产生竞争冒险的乘积项。

也可采用增加冗余项方法。

选择消除险象的方法应根据具体情况而定。

组合逻辑电路的险象是一个重要的实际问题。

当设计出一个组合电路,安装后应首先进行静态测试,也就是用逻辑开关按真值表依次改变输入量,验证其逻辑功能。

然后再进行动态测试,观察是否存在冒险。

如果电路存在险象,但不影响下一级电路的正常工作,就不必采取消除险象的措施;如果影响下一级电路的正常工作,就要分析险象的原因,然后根据不同的情况采取措施加以消除。

华师16秋《数字逻辑》在线作业⼀、单选题(共 40 道试题,共 40 分。

)V 1. Moor和Mly型时序电路的本质区别是(). 没有输⼊变量. 当时的输出只和当时电路的状态有关,和当时的输⼊⽆关. 没有输出变量. 当时的输出只和当时的输⼊有关,和当时的电路状态⽆关标准答案:2. 下列触发器中,()不可作为同步时序逻辑电路的存储元件。

. 基本R-S触发器. 触发器. J-K触发器. T触发器标准答案:3. 设计⼀个8421码加1计数器,⾄少需要()触发器. 3个. 4个. 6个. 10个标准答案:4.题⾯见图⽚:....标准答案:5.题⾯见图⽚:....标准答案:6. ⼀个T触发器,在T=1时,来⼀个时钟脉冲后,则触发器( )。

. 保持原态7. 下列逻辑门中,()不属于通⽤逻辑门. 与⾮门. 或⾮门. 或门. 与或⾮门标准答案:8. 以下哪⼀条不是消除竟争冒险的措施(). 接⼊滤波电路. 利⽤触发器. 加⼊选通脉冲. 修改逻辑设计标准答案:9.题⾯见图⽚:...标准答案:10.题⾯见图⽚:....标准答案:11. 和⼆进制码1100对应的格雷码是(). 0011. 1100. 1010. 0101标准答案:. 8⼊5出标准答案:13. 实现同⼀功能的Mly型同步时序电路⽐Moor型同步时序电路所需要的(). 状态数⽬更多. 状态数⽬更少. 触发器更多. 触发器⼀定更少标准答案:14. ⽤PL进⾏逻辑设计时,应将逻辑函数表达式变换成(). 异或表达式. 与⾮表达式. 最简“与—或”表达式. 标准“或—与”表达式标准答案:15.题⾯见图⽚:....标准答案:16.题⾯见图⽚:....标准答案:17. 构造⼀个模10同步计数器,需要()触发器. 3个. 4个. 5个18. 电平异步时序逻辑电路不允许两个或两个以上输⼊信号(). 同时为0. 同时为1. 同时改变. 同时出现标准答案:19. 组合型PL是由()构成. 与门阵列和或门阵列. ⼀个计数器. ⼀个或阵列. ⼀个寄存器标准答案:20. ⼀⽚四位⼆进制译码器,它的输出函数有(). 1个. 8个. 10个. 16个标准答案:21. ⽤ROM实现四位⼆进制码到四位循环码的转换,要求存储器的容量为()。