DLX流水线技术数据相关与结构相关

- 格式:doc

- 大小:389.50 KB

- 文档页数:14

计算机体系结构试题库判断题(102题)1.(√)执行时间不是唯一的性能指标,但它是最普遍的性能表示形式。

2.(×)根据Moore定律,DRAM的周期时间是每三年降低四倍。

3.(×)MIPS是测量计算机性能的一致性指标。

4.(√)在计算机性能测量中,调和平均的含义是单位时间机器能够执行的程序数。

5.(×)可以用典型程序来设计和优化指令集。

6.(×)增加流水线的级数总可以增加流水线的性能。

7.(×)多处理机系统中的素数模低位交叉存储器可以避免所有访存冲突。

8.(√)部件的可靠性通常可以用平均无故障时间来衡量。

9.(√)在向量处理机中,链接只能在顺序的Convoy(向量指令并行集)之间进行。

10.(×)n维超立方体单级互连网络中的节点数为n。

11.(×)MIPS和MFLOPS是计算机性能衡量的两个可靠指标。

12.(×)RISC结构的机器性能一定要比CISC结构的机器性能高。

13.(×)平均每条指令的执行周期数(CPI)与程序无关。

14.(√)CPU性能公式中指令条数(IC)与指令集格式和编译器有关。

15.(√)CPU的组织在一定程度上会影响CPU所能达到的频率。

16.(√)解释执行比翻译执行花的时间多,但存储空间占用较少。

17.(×)计算机体系结构设计这不必关心指令集具体实现。

18.(×)当前没有任何一种指令集结构是堆栈型结构,因为它已经过时了。

19.(√)虽然结构相关会影响流水线的性能,但是我们在具体的流水线设计中仍然允许一定的结构相关存在。

20.(×)程序的时间局部性指程序即将用到的信息很可能与目前正在使用的信息在空间上相邻或者临近。

21.(×)程序的空间局部性指程序即将用到的信息很可能就是目前正在使用的信息。

22.(√)Amdahl定律揭示的性能递减规则说明如果仅仅对计算机中的一部分做性能改进,则改进越多,系统获得的效果越小。

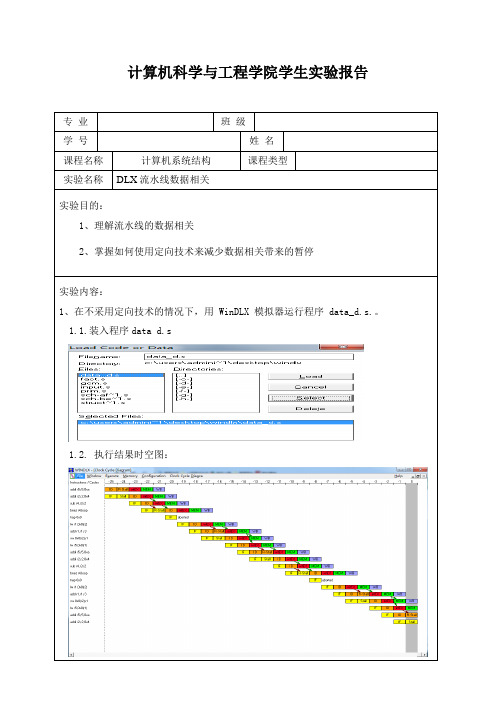

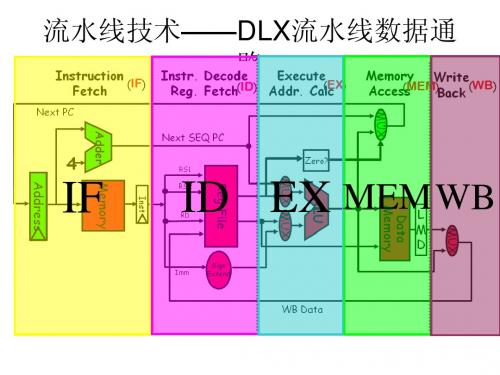

WinDLX实验报告1.实验目的:1)熟悉计算机流水线基本概念2)了解DLX基本流水线的各段的功能了解各种不同指令在流水线中的实际流动情况3)对流水线做性能分析4)了解影响流水线效率的因素——数据相关、结构相关、控制相关,了解相关的种类5)了解决数据相关的方法2.实验内容:1)在仿真器上分别运行单条指令:Load指令、Store指令、分支指令、寄存器ALU指令、立即数ALU指令,记录它们在流水线中的执行情况2)仿真器运行一段无相关的程序,记录执行情况,计算流水线的加速比、吞吐率与效率。

3)在仿真器运行一段程序,统计该程序在流水线中出现的各种相关个数,及其引起的流水线暂停周期数4)在流水线中设置定向路径来消除数据相关,运行程序并统计在流水线中出现的相关个数,及其引起的流水线暂停周期数5)通过对程序进行编译优化并结合其他相关解决方法——分支预测与延迟槽,运行程序并统计在流水线中出现的相关个数,及其引起的流水线暂停周期数。

3.实验步骤:1.)熟悉WinDLX的使用用WinDLX模拟器执行求阶乘程序fact.s 。

这个程序说明浮点指令的使用。

该程序从标准输入读入一个整数,求其阶乘,然后将结果输出。

该程序中调用了input.s中的输入子程序,这个子程序用于读入正整数。

实验结果:在载入fact.s和input.s之后,不设置任何断点运行。

a.不采用重新定向技术,我们得到的结果b.采用定向技术,我们得到的结果:从上面的数据我们可以看出定向的作用:在定向技术存在的情况下Statistics 窗口中的各种统计数字:总的周期数(215) 和暂停数(17 RAW, 25 Control, 12 Trap; 54 Total)在定向技术不存在时候,控制暂停和Trap 暂停仍然是同样的值,而RAW暂停从17变成了53,总的模拟周期数增加到236。

所以定向技术带来的加速比:236 / 215 = 1.098DLX forwarded比DLX not forwarded快9.8%。

实验二指令流水线相关性分析·实验目的通过使用WINDLX模拟器,对程序中的三种相关现象进行观察,并对使用专用通路,增加运算部件等技术对性能的影响进行考察,加深对流水线和RISC 处理器的特点的理解。

·实验原理:指令流水线中主要有结构相关、数据相关、控制相关。

相关影响流水线性能。

·实验步骤一.使用WinDLX模拟器,对Fact.s做如下分析:(1)观察程序中出现的数据/控制/结构相关。

指出程序中出现上述现象的指令组合。

(2)考察增加浮点运算部件对性能的影响。

(3)考察增加forward部件对性能的影响。

(4)观察转移指令在转移成功和转移不成功时候的流水线开销。

·实验过程一.使用WinDLX模拟器,对Fact.s做如下分析:浮点加、乘、除部件都设置为1,浮点数运算部件的延时都设置为4,如图1:图1 初始设置将fact.s和input.s加载至WinDLX中,如图2示。

图2 加载程序1.观察程序中出现的数据/控制/结构相关;指出程序中出现上述现象的指令组合。

1)数据相关点击F7,使程序单步执行,当出现R-Stall时停止,运行过程中出现下图3所示,输入整数6。

图3 输入整数6打开Clock Diagram,可以清楚的看到指令执行的流水线如图4所示。

图4 指令流水线双击第一次出现R-Stall的指令行,如图5所示。

图5 指令详细信息对以上出现的情况分析如下:程序发生了数据相关,R-Stall(R-暂停)表示引起暂停的原因是RAW。

lbu r3,0×0(r2)要在WB周期写回r3中的数据;而下一条指令seqi r5,r3,0×a要在intEX周期中读取r3中的数据。

上述过程发生了WR冲突,即写读相关。

为了避免此类冲突,seq r5,r4,0×a的intEX指令延迟了一个周期进行。

由此,相关指令为:2)控制相关由图6可以看出,在第4时钟周期:第一条指令处于MEM段,第二条命令处于intEX段,第三条指令出于aborted状态,第四条命令处于IF段。

计算机系统结构实验指导手册李静梅、吴艳霞哈尔滨工程大学目录1.实验内容 (1)1.1实验一流水线中的相关 (1)1.2实验二循环展开及指令调度 (3)2.模拟器安装方法 (4)3.演示例程 (4)3.1 配置WinDLX (4)3.2 装载测试程序 (5)3.3 模拟步骤 (5)4.WINDLX汇编语言简介 (8)5.WINDLX汇编语言语言示例 (10)5.1 数据定向和结构相关例程 (10)5.2 指令再定序例程 (11)6.大作业封面模板 (13)7.DLX指令集 (14)1.实验内容1.1实验一流水线中的相关实验目的1. 熟练掌握WinDLX模拟器的操作和使用,熟悉DLX指令集结构及其特点;2. 加深对计算机流水线基本概念的理解;3. 进一步了解DLX基本流水线各段的功能以及基本操作;4. 加深对数据相关、结构相关的理解,了解这两类相关对CPU性能的影响;5. 了解解决数据相关的方法,掌握如何使用定向技术来减少数据相关带来的暂停。

实验平台WinDLX模拟器实验内容和步骤(做实验前请先认真阅读WinDLX教程)1.用WinDLX模拟器执行下列三个程序(任选一个):●求阶乘程序fact.s●求最大公倍数程序gcm.s●求素数程序prim.s分别以步进、连续、设置断点的方式运行程序,观察程序在流水线中的执行情况,观察CPU 中寄存器和存储器的内容。

熟练掌握WinDLX的操作和使用。

注意:fact.s中调用了input.s中的输入子程序。

load程序时,要两个程序一起装入(都select 后再点击load)。

gcm.s也是如此。

2.用WinDLX运行程序structure_d.s,通过模拟:●找出存在结构相关的指令对以及导致结构相关的部件;●记录由结构相关引起的暂停时钟周期数,计算暂停时钟周期数占总执行周期数的百分比;●论述结构相关对CPU性能的影响,讨论解决结构相关的方法。

3.在不采用定向技术的情况下(去掉Configuration菜单中Enable Forwarding选项前的勾选符),用WinDLX运行程序data_d.s。

3.3.2流水线的数据相关1. 数据相关简介当指令在流水线中重叠执行时,流水线有可能改变指令读/写操作数的顺序,使得读/写操作顺序不同于它们非流水实现的顺序,这将导致数据相关。

首先让我们考虑下列指令在流水线中的执行情况:ADD R1,R2,R3SUB R4,R5,R1AND R6,R1,R7OR R8,R1,R9XOR R10,R1,R11ADD指令后的所有指令都要用到ADD指令的计算结果,如图3.3.4所示,ADD 指令在WB 段才将计算结果写入寄存器R1 中,但是SUB 指令在其ID 段就要从寄存器R1 中读取该计算结果,这种情况就叫做数据相关。

除非有措施防止这一情况出现,否则SUB 指令读到的是错误的值。

所以,为了保证上述指令序列的正确执行,流水线只好暂停ADD 指令之后的所有指令,直到ADD 指令将计算结果写入寄存器R1 之后,再启动ADD指令之后的指令继续执行。

从图3.3.4还可以看到,AND 指令同样也将受到这种相关关系的影响。

ADD 指令只有到第五个时钟周期末尾才能结束对寄存器R1 的写操作,所以AND 指令在第四个时钟周期从寄存器R1 中读出的值也是错误的。

而XOR 指令则可以正常操作,因为它是在第六个时钟周期读寄存器R1 的内容。

另外,利用DLX流水线的一种简单技术,可以使流水线顺利执行OR 指令。

这种技术就是:在DLX 流水线中,约定在时钟周期的后半部分进行寄存器文件的读操作,而在时钟周期的前半部分进行寄存器文件的写操作。

在本章的图中,我们将寄存器文件的边框适当地画成虚线来表示这种技术。

2. 通过定向技术减少数据相关带来的暂停图3.3.4中的数据相关问题可以采用一种称为定向(也称为旁路或短路)的简单技术来解决(动画演示)。

定向技术的主要思想是:在某条指令(如图3.3.4中的ADD 指令)产生一个计算结果之前,其它指令(如图3.3.4中的SUB 和AND 指令)并不真正需要该计算结果,如果能够将该计算结果从其产生的地方(寄存器文件EX/MEM)直接送到其它指令需要它的地方(ALU 的输入寄存器),那么就可以避免暂停。

基于这种考虑,定向技术的要点可以归纳为:(1) 寄存器文件EX/MEM 中的ALU 的运算结果总是回送到ALU 的输入寄存器。

(2) 当定向硬件检测到前一个ALU 运算结果的写入寄存器就是当前ALU 操作的源寄存器时,那么控制逻辑将前一个ALU 运算结果定向到ALU 的输入端,后一个ALU 操作就不必从源寄存器中读取操作数。

图3.3.4还表明,流水线中的指令所需要的定向结果可能并不仅仅是前一条指令的计算结果,而且还有可能是前面与其不相邻指令的计算结果,图3.3.5是采用了定向技术后上述例子的执行情况,其中寄存器文件和功能单元之间的箭头表示定向路径。

上述指令序列可以在图3.3.5中顺利执行而无需暂停。

上述定向技术可以推广到更一般的情况,可以将一个结果直接传送到所有需要它的功能单元。

也就是说,一个结果不仅可以从某一功能单元的输出定向到其自身的输入,而且还可以从某一功能单元的输出定向到其它功能单元的输入。

(1) 写后读相关(RAW:Read After Write)(命名规则):j 的执行要用到i 的计算结果,当它们在流水线中重叠执行时,j 可能在i 写入其计算结果之前就先行对保存该结果的寄存器进行读操作,从而得到错误的值。

这是最常见的一种数据相关,图3.3.6和图3.3.7中采用定向技术消除的数据相关就属于这种类型。

(2) 写后写相关(WAW:Write After Write ):j 和i 的目的寄存器相同,当它们在流水线中重叠执行时,j 可能在i 写入其计算结果之前就先行对该结果寄存器进行写操作,从而导致写入顺序错误,在目的寄存器中留下的是i 写入的值,而不是j 写入的值。

如果在流水线中不只一个段可以进行写操作,或者当流水线暂停某条指令时,允许该指令之后的指令继续前进,就可能会产生这种类型的数据相关。

由于DLX 流水线只在WB 段写寄存器,所以在DLX 流水线中执行的指令不会发生这种类型的数据相关。

如果我们对DLX流水线作如下改变,在DLX流水线中执行的指令就有可能发生WAW相关。

首先,将ALU 运算结果的写回操作移到MEM 段进行,因为这时计算结果已经有效;其次,假设访问数据存储器占两个流水段。

下面是两条指令在修改后的DLX 流水线中执行的情况:可以看出,在修改后的DLX 流水线中执行上述指令序列后,寄存器R1 中的内容是第一条指令(LW)的写入结果,而不是ADD 指令的写入结果。

这就是由于WAW 相关所带来的错误执行结果。

(3) 读后写相关(WAR:Write After Read ):j 可能在i 读取某个源寄存器的内容之前就先对该寄存器进行写操作,导致i 后来读取到的值是错误的。

由于DLX 流水线在ID 段完成所有的读操作,在WB 段完成所有的写操作。

所以,在DLX 流水线中不会产生这种类型的数据相关。

基于上面修改后的DLX 流水线,考察下面两条指令的执行情况:如果SW 指令在MEM2 段的后半部分读取寄存器R2 的值,ADD 指令在WB 段的前半部分将计算结果写回寄存器R2,则SW 将读取错误的值,将ADD 指令的计算结果写入存储器中。

值得注意的是,在读后读(RAR:Read After Read)的情况下,不存在数据相关问题。

4. 需要暂停的数据相关前面我们讨论了如何利用定向技术消除由于数据相关带来的暂停。

但是,并不是所有数据相关带来的暂停都可以通过定向技术消除。

为了保证流水线正确执行上述指令序列,可以设置一个称为流水线互锁(pipeline interlo ck)的功能部件。

一旦流水线互锁检测到上述数据相关,流水线暂停执行LW指令之后的所有指令,直到能够通过定向解决该数据相关为止。

图3.3.12为流水线互锁插入暂停后流水线数据通路;图3.3.13是加入暂停前后的流水线时空图。

下面讨论如何利用编译器技术来减少这种必须的暂停,然后论述如何在流水线中实现数据相关检测和定向。

5. 对数据相关的编译器调度方法流水线常常会遇到许多种类型的暂停。

比如,采用典型的代码生成方法对A = B + C这种常用的表达式进行处理,可以得到如图3.3.14所示的指令序列。

从图3.3.14可以看出,在ADD 指令的流水过程中必须插入一个暂停时钟周期,以保证变量C的读入值有效。

既然定向无法消除指令序列中所包含的这种暂停,那么能否让编译器在进行代码生成时就消除这些潜在的暂停呢?实际上,编译器的确可以通过重新组织代码顺序来消除这种暂停。

通常称这种重新组织代码顺序消除暂停的技术为流水线调度(pipeline scheduling)或指令调度(instruction schedulin g)。

例3.6 请为下列表达式生成没有暂停的DLX代码序列。

假设载入延迟为1个时钟周期。

a =b - c;d =e - f;解:调度前后的指令序列如表3.2所示。

可以看出,两条ALU指令(ADD Ra,Rb,R c 和SUB Rd,Re,Rf)分别和两条Load指令(LW Rc,c和LW Rf,f)之间存在数据相关。

为了保证流水线正确执行调度前的指令序列,必须在指令执行过程中插入两个时钟周期的暂停。

但是考察调度后的指令序列不难发现,由于流水线允许定向,就不必在指令执行过程中插入任何暂停周期。

6. 对DLX流水线控制的实现让一条指令从流水线的指令译码段(ID)移动到执行段(EX)的过程通常称为指令发射,而经过了该过程的指令为已发射的指令。

对于DLX 标量流水线而言,所有的数据相关均可以在流水线的ID段检测到,如果存在数据相关,指令在其发射之前就会被暂停。

这样,我们可以在ID段决定需要什么样的定向,然后设置相应的控制。

在流水线中较早地检测到相关,可以降低实现流水线的硬件复杂度,因为这样不必在流水过程中被迫将一条已经改变了机器状态的指令挂起。

另外一种方法是在使用一个操作数的时钟周期开始(DLX 流水线的EX 和MEM 段的开始)检测相关,确定必需的定向。

为了说明这两种方法的不同,我们将以Load 指令所引起的RAW 相关为例,论述如何通过在ID段的检测来实现流水线控制,其中到ALU 输入的定向路径可以在EX 段。

表3.3列出了流水线相关检测硬件可以检测到的各种相关情况。

现在来看看如何实现流水线互锁。

如果某条指令和Load 指令有一个RAW 相关时,该指令处于ID段,Load 指令处于EX段。

我们可以用表3.4来描述此时所有可能的相关情况。

一旦硬件检测到上述RAW 相关,流水线互锁必须在流水线中插入暂停周期,使正处于IF 和ID段的指令不再前进。

另外,还必须暂停向前传送IF/ID 寄存器组的内容,使得流水线能够保持被暂停的指令。

对定向而言,虽然可能要考虑许多情况,但是定向逻辑的实现方法是类似的。

实现定向逻辑的关键是,流水线寄存器不仅包含了被定向的数据,而且包含了目标和源寄存器域。

从上面的讨论可知,所有定向都是从ALU 或数据存储器的输出到ALU、数据存储器或0检测单元的输入的定向,我们可以分别将EX/MEM 和MEM/WB 段的寄存器IR 同ID/EX 和EX/MEM 段中的寄存器IR 相比较,决定是否需要定向,从而实现必需的定向控制。

定向的控制硬件除了需要用比较器和组合逻辑来确定什么时候打开哪一条定向路径之外,还需要在ALU 输入端采用具有多个输入的多路器,并增加相应的定向路径连接通路。

改进图3.2.17中的相关硬件,可以得到图3.3.15,图中画出了所增设的定向路径。

在DLX 中,任何流水线寄存器到任何功能单元的输入都可能需要定向路径。

前面的一些数据相关的实例均是有关寄存器操作数的,但是数据相关也有可能发生在一对指令对存储器同一单元进行读写的时候。

不过,本章仅讨论有关寄存器的数据相关。

3. 数据相关的分类根据指令对寄存器的读写顺序,可以将数据相关分为三类。

习惯上,这些相关是根据流水线所必须保持的访问顺序来命名的。

考虑流水线中的两条指令i 和j ,且i 在j 之前进入流水线,由此可能带来的数据相关有:。