ASICDesign4--复旦大学专用集成电路课件

- 格式:ppt

- 大小:436.50 KB

- 文档页数:44

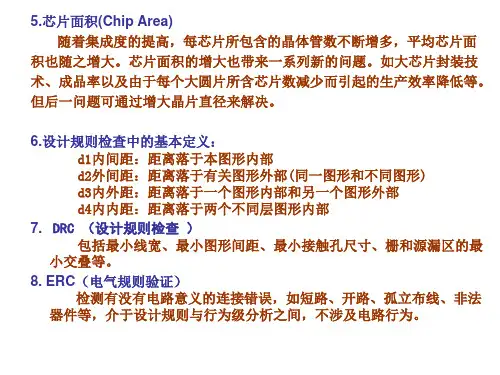

–集成电路设计流程与EDA软件•半定制设计流程•全定制设计流程–选择EDA设计工具的原则–主要的EDA Vendor工具特色–集成电路设计流程与EDA软件•半定制设计流程•全定制设计流程–选择EDA设计工具的原则–主要的EDA Vendor工具特色迭代性2与3可互换LVS/DRC1. 设计输入硬件描述语言设计输入,任何文本编辑工具–如:Ultraedit (IDM Computer Solutions 公司); vi (Linux 文本编辑工具)–仿真器自带编辑器…计规范检查:LEDA (Synopsys )-增强了设计人员检查HDL 代码的能力,包括可综合性,可仿真性、可测试性和可重用性Logic Design Flow2、逻辑综合–Synopsys:Design Compiler;380到500个综合库198890 %ASIC设计师选用1年的license 83万RMBLogic Design Flowdesign entryPhysical Design FlowDesign & timing SetupFloor Planning布图规划:包括裸片大小的规划、I/O规划、电源规划、大量硬核或模块(hard core、block)的规划等,是对芯片内部结构的完整规划和设计。

布图规划的合理与否直接关系到芯片的时序收敛、布线通畅。

CTSCTS步骤中,需要对设计的时钟分布有大体的了解,buffer tree的级数,时钟的skew等分为全局布线(global routing )、详细布线(detailrouting )和布线修正(search and repair )。

RoutingDesign For Manufacturability(DFM)保证芯片能被foundry正确制造:1.天线效应修补:如果某一层的一个信号线过长,在制造过程中可能会吸收大量的电荷,从而造成栅氧化层击穿。

一般工具软件会使信号跳层或者插入反偏二极管来消除;2.单孔变多孔:布线完成后不同层的金属在连接处都只用了单一孔来进行连接,这样接触电阻大,而且如果制造出问题时容易断路。