第三章(DSP第四讲).

- 格式:ppt

- 大小:1.40 MB

- 文档页数:51

DSP技术课程讲授提纲DSP技术课程讲述内容第一章DSP概述:在这一章中,我们将介绍我们数字信号处理的基本框图、DSP的组成特点、DSP的应用、TI的DSP系列等。

第二章和第三章分别介绍DSP的硬件结构与指令系统。

在这两章中我们将介绍TI的DSP 系列中的C2X,C3X,C54X和C6X系列。

重点讲解C54X的硬件结构和指令系统。

第四章开发环境:在这一章中我们将介绍TI的DSP的开发工具,如编译器、汇编器、连接器、调试器的使用,以及集成开发环境CCS的使用。

这章的最后还将介绍DSP的实时操作系统(RTOS)。

第五章DSP的算法实现:以C54X为例,介绍基本加、减、乘、除的实现(定点/浮点),FIR滤波器,自适应滤波器,FFT的实现等。

第六章DSP工程应用:这一章中我们将以两三个具体的应用事例,详细了解DSP的设计流程。

包括:VC5402 DEMO板设计,DTMF的产生和解码,IS-54移动电话,IP电话,V.34调制解调器等。

教材与参考书第一章概论§1-1 为什么要采用数字信号处理?(1)灵活性(2)精度(3)可靠性和可重复性(4)大规模集成(5)虚拟特性与升级(6)特殊应用:有些应用只有数字系统才能实现DSP信号流图§1-2 DSP的发展与特点DSP的特点∙哈佛结构∙硬件乘法/累加器∙并行性∙多DSP协调工作模式∙多种寻址方式∙ DMA∙片上测试口∙ DSP核及延伸芯片∙低功耗DSP的发展∙更高的运行速度和信号处理速度∙多DSP协同工作∙更方便的开发环境∙大量专用DSP的出现(DSP核)∙更低的价格,或更高的性能/价格比∙更广泛的应用(每年以30%增长)∙更低的功耗(55X 0.05mw/MIPS)---------------------------------------------------------------第一次课---------------------------------------- 例:滤波器的实现用模拟电路实现低通滤波器与使用DSP实现低通滤波器的比较。

《数字信号处理》教案第一章:绪论1.1 课程介绍理解数字信号处理的基本概念了解数字信号处理的发展历程明确数字信号处理的应用领域1.2 信号的概念与分类定义信号、模拟信号和数字信号掌握信号的分类和特点理解信号的采样与量化过程1.3 数字信号处理的基本算法掌握离散傅里叶变换(DFT)了解快速傅里叶变换(FFT)学习Z变换及其应用第二章:离散时间信号与系统2.1 离散时间信号理解离散时间信号的定义熟悉离散时间信号的表示方法掌握离散时间信号的运算2.2 离散时间系统定义离散时间系统及其特性学习线性时不变(LTI)系统的性质了解离散时间系统的响应2.3 离散时间系统的性质掌握系统的稳定性、因果性和线性学习时域和频域特性分析方法第三章:离散傅里叶变换3.1 离散傅里叶变换(DFT)推导DFT的数学表达式理解DFT的性质和特点熟悉DFT的应用领域3.2 快速傅里叶变换(FFT)介绍FFT的基本概念掌握FFT的计算步骤学习FFT的应用实例3.3 离散傅里叶变换的局限性探讨DFT在处理非周期信号时的局限性了解基于DFT的信号处理方法第四章:数字滤波器设计4.1 滤波器的基本概念理解滤波器的定义和分类熟悉滤波器的特性指标学习滤波器的设计方法4.2 数字滤波器的设计方法掌握常见数字滤波器的设计算法学习IIR和FIR滤波器的区别与联系了解自适应滤波器的设计方法4.3 数字滤波器的应用探讨数字滤波器在信号处理领域的应用学习滤波器在通信、语音处理等领域的应用实例第五章:数字信号处理实现5.1 数字信号处理器(DSP)概述了解DSP的定义和发展历程熟悉DSP的特点和应用领域5.2 常用DSP芯片介绍学习TMS320系列DSP芯片的结构和性能了解其他常用DSP芯片的特点和应用5.3 DSP编程与实现掌握DSP编程的基本方法学习DSP算法实现和优化技巧探讨DSP在实际应用中的问题与解决方案第六章:数字信号处理的应用领域6.1 通信系统中的应用理解数字信号处理在通信系统中的重要性学习调制解调、信道编码和解码等通信技术探讨数字信号处理在无线通信和光通信中的应用6.2 音频信号处理熟悉音频信号处理的基本概念和算法学习音频压缩、回声消除和噪声抑制等技术了解数字信号处理在音乐合成和音频效果处理中的应用6.3 图像处理与视频压缩掌握数字图像处理的基本原理和方法学习图像滤波、边缘检测和图像压缩等技术探讨数字信号处理在视频处理和多媒体通信中的应用第七章:数字信号处理工具与软件7.1 MATLAB在数字信号处理中的应用学习MATLAB的基本操作和编程方法熟悉MATLAB中的信号处理工具箱和函数掌握利用MATLAB进行数字信号处理实验和分析的方法7.2 其他数字信号处理工具和软件了解常用的数字信号处理工具和软件,如Python、Octave等学习这些工具和软件的特点和应用实例探讨数字信号处理工具和软件的选择与使用第八章:数字信号处理实验与实践8.1 数字信号处理实验概述明确实验目的和要求学习实验原理和方法掌握实验数据的采集和处理8.2 常用数字信号处理实验完成离散信号与系统、离散傅里叶变换、数字滤波器设计等实验8.3 数字信号处理实验设备与工具熟悉实验设备的结构和操作方法学习实验工具的使用技巧和安全注意事项第九章:数字信号处理的发展趋势9.1 与数字信号处理探讨技术在数字信号处理中的应用学习深度学习、神经网络等算法在信号处理领域的应用实例9.2 物联网与数字信号处理理解物联网技术与数字信号处理的关系学习数字信号处理在物联网中的应用,如传感器信号处理、无线通信等9.3 边缘计算与数字信号处理了解边缘计算的概念和应用场景探讨数字信号处理在边缘计算中的作用和挑战10.1 课程回顾梳理本门课程的主要内容和知识点10.2 数字信号处理在未来的发展展望数字信号处理技术在各个领域的应用前景探讨数字信号处理技术的发展趋势和挑战10.3 课程考核与评价明确课程考核方式和评价标准鼓励学生积极参与课堂讨论和实践活动,提高综合素质重点和难点解析重点一:信号的概念与分类信号的定义和分类是理解数字信号处理的基础,需要重点关注。

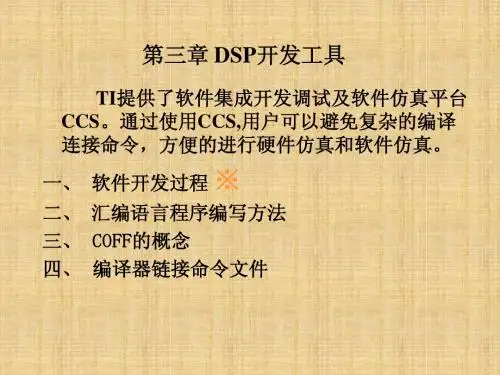

第三章DSP开发工具T提供了软件集成开发调试及软件仿真平台CCS。

通过使用CCS,用户可以避免复杂的编译连接命令,方便的进行硬件仿真和软件仿真。

一、软件开发过程※二、汇编语言程序编写方法三、COFF的概念四、编译器链接命令文件软件开发过程大体要经过化等几个主要过程。

1)编辑:编辑源程序(.ASM或.C)和链接器命令文件(.CMD)。

源程序可以用汇编或C语言来设计,当然也可以进行混合编程。

2)编译: 将原程序编译成为公共目标格式文件(COFF 格式的.OBJ)、存储器映像文件(.MAP)和列表文件(.LST),对于C程序首先要由C编译器编译成为汇编程序,然后再生成OBJ文件。

3)链接成可执行代码:将用户的多个COFF文件连同所引用的库文件一起组合成为可执行代码。

4)调试:通过软仿真或硬件仿真方式对程序进行调试5)固化:将执行代码烧写进ROM中,实现脱机运行。

第三章DSP开发工具一、软件开发过程二、汇编语言程序编写方法※三、COFF的概念四、编译器链接命令文件1)文件扩展名为.ASM2)汇编语言源程序的句法:如START: STM #0,SWWSR ;SWWSR=0不插入等待时间[标号][:] 助记符[操作数] [;注释]标号:标号和冒号都是可选项,代表段程序计数器(SPC)的值。

所有标号必须从第一列开始写,最多可达32字符(A~Z,a~z,0~9 …_‟,…$‟),第一字母不能数字。

如果不用标号,则第一字母必须为空格、分号或星号。

助记符:可以是助记符指令、汇编指令、宏指令和宏调用。

助记符指令一般大写。

汇编命令和宏命令均以“.”开始,并且小写。

汇编命令可以定义常量和变量,用于控制汇编和链接过程,可以不占存储空间。

注意:汇编命令不能写在第一列。

操作数:指令中的操作数或汇编命令中定义的内容,操作数之间必须以逗号隔开,也有一些指令没有操作数。

如NOP。

注释:注释前必须加分号,一般用于标注指令的执行信息,使程序增加可读性。

![DSP技术liuguoman_第四讲[1].C6000+DSP最小系统设计](https://uimg.taocdn.com/56f77423ed630b1c59eeb52e.webp)

第四讲 DSP 最小硬件系统的设计4.1引言一个 DSP 硬件系统可以分为最小硬件系统设计和外围接口设计两个部分。

本讲主要介绍 DSP 最小硬件系统的设计,包括复位、时钟、 电源及存储器接口等. 5402最小系统原理图 5402最小系统5402最小系统 电源图 继续返回返回返回4.2DSP 系统的基本硬件设计4.2.1 复位电路电压公式:电源刚加上电时, TMS320 DSP 芯片处于复位状态,/RS 低使芯片复位 为使芯片初始化正确,一般应保证/RS 为低至少持续 3 个 CLKOUT 周期 但是,在上电后,系统的晶体振荡器一般需要儿百毫秒的稳定期,一般为 100~200ms 。

选择 R = 100K , C = 47μ,可得 t1= 167ms 。

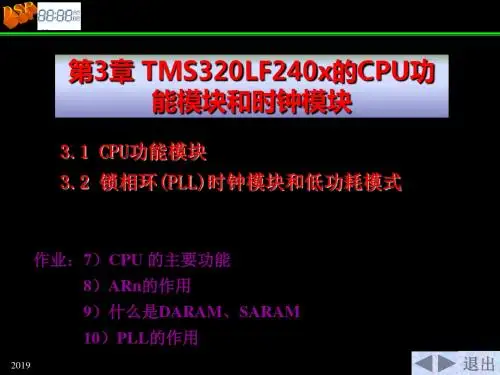

●此种复位特点: 提问:输入方式比较,阻容颠倒可以不? 存在不足:有时不能可靠复位 简单如何设计复位电路4.2.1 复位电路上电触发掉电保护触发4.2.2 时钟电路4.2.2 时钟电路TMS320VC5402内部具有一个可编程锁相环(PLL),它可以配置为两种模式:( 1 ) PLL 模式。

输入时钟乘以一个1~31之间的常数; ( 2 ) DIV 模式。

输入时钟除以 2 或 4 。

软件可编程 PLL 受一个存储器映射(地址为 58h )的时钟模式寄存器 CLKMD 控制,CLKMD 用于定义 PLL 时钟模块的配置。

复位后 CLKMD的值根据 DSP芯片三根输入引脚CLKMD1~CLKMD3 确定,从而确定 DSP 的工作时钟。

4.2.2 时钟电路由于 DSP 的程序需要从外部低速 EPROM 、EEPROM 中调入,可以采用较低工作频率的 DSP 复位时钟模式,待程序全部调入到内部快速 RAM 后,再用软件重新配置CLKMD 的值,使芯片工作在较高的频率上。

例如: 设外部晶体频率是 10MHz ,设置CLKMD1~CLKMD3 = 111,则复位后DSP的工作频率是10MH/2 = 5MHz。

一.数字信号处理概述1.DSP的优势:可控性强,稳定度高,精度高,抗干扰性强,实现自适应性,数据压缩,大规模集成。

2.实时数字信号处理:信号处理速度必须大于等于输入信号更新的速度,而且信号输入到处理后输出的延迟必须足够的小实时取决因素:芯片速度,运算量(数据率,算法复杂度)3.DSP子系统实现方式:通用CPU,加速处理模块,单片机,专用DSP芯片,可编程FPGA 器件,通用可编程DSP芯片3.DSP系统典型处理方法:数据流处理。

块处理矢量处理4.定点与浮点DSP芯片定点:小数Xf转换为定点数Xd:Xd=int(Xf×2Q)定点数Xd转换为小数Xf:Xf=float(Xd×2-Q)0.25的Q15表示法——0.25×215=8192=0x20000x4623的Q15表示小数——17955×2-15=0.547943第一位为符号位浮点:bit3bit3bit2bit2bit S e f浮点数=(-1)S×2(e-127)×1.f-0.75=-(0.11)2=-(1.1)×2-1=(-1)1×(1.1)×2(126-127)-0.75的IEEE单精度浮点格式数为:(BF400000)H5.DSPs芯片特点算数单元:硬件乘法器是DSPs区别于早期通用微处理起的重要标志多功能单元使DSP在单位时间内完成更多的操作,提高了程序执行速度总线结构:哈弗总线结构流水技术:是提高DSPs程序执行效率的另一个重要手段专用寻址单元:地址的计算不再额外占用CPU时间片内存储器:程序存储,数据存储,CACHE丰富的外设6.DSP处理器实现高速运算途径⏹硬件乘法器及乘加单元⏹高效的存储器访问⏹数据格式⏹零循环开销⏹多个执行单元⏹数据流的线性I/O⏹专门的指令集6.DSP评价方法:传统性能评价MIPS-----百万指令每秒MOPS-----百万操作每秒MFLOPS-----百万浮点操作每秒MACS-------乘加次数每秒完整应用评价核心算法评价7.选型依据:速度,精度,芯片资源,开发工具,支持多处理器,功耗与电源管理,成本。

DSP的基本原理及应⽤--第四讲第6章 DSP55xx芯⽚的指令系统及编程TMS320C55xx DSP指令集可分为六⼤类操作类型:①装载和存储指令:交换、数据移动、堆栈操作及复制(DELAY)②算术指令:加法、减法、加减、减加、乘法、乘累加、乘累减、移位、带条件加减、带条件移位,⽐较指令等③程序控制指令:条件转移、⽆条件转移、重复、条件执⾏、CALL等④bit控制指令:bit Test、Set、Clear、Complement⑤扩展辅助寄存器指令:辅助寄存器数据移动、堆栈操作⑥逻辑操作指令:与、或、⾮、异或、取反、逻辑移位⑦其它操作指令:mmap、port§6.1装载和存储指令语法并⾏使能bit长度周期流⽔线执⾏单元Accumulator, Auxiliary, or Temporary Register ContentSwapA unit ALUSWAP ARx, Tx Yes 2 1 AD A unit register file SWAP Tx, Ty Yes 2 1 AD A unit register file SWAP ARx, ARy Yes 2 1 AD A unit register file SWAP ACx, ACy Yes 2 1 X D unit register file SWAPP ARx, Tx Yes 2 1 AD A unit register file SWAPP T0, T2Yes 2 1 AD A unit register file SWAPP AR0, AR2Yes 2 1 AD A unit register file SWAPP AC0, AC2 Yes 2 1 X D unit register file SWAP4 AR4, T0 Yes 2 1 AD A unit register file Accumulator, Auxiliary, or Temporary Register LoadMOV k4, dst Yes 2 1 X A or D unit register file MOV –k4, dst Yes 2 1 X A or D unit register file MOV K16, dst No 4 1 X A or D unit register file MOV Smem, dst No 2 1 X A or D unit register file MOV [uns()high_byte(Smem)[]], dst No 3 1 X A or D unit register file MOV [uns()low_byte(Smem)[]], dst No 3 1 X A or D unit register file MOV K16 << #16, ACx No 4 1 X D unit ALUMOV K16 << #SHFT, ACx No 4 1 X D unit shifterMOV [rnd()Smem << Tx[]], ACx No 3 1 X D unit shifterMOV low_byte(Smem) << #SHIFTW, ACx No 3 1 X D unit shifterMOV [uns()Smem[]] << #SHIFTW, ACx No 4 1 X D unit shifterMOV[40] dbl(Lmem), ACx No 3 1 X D unit register file MOV Xmem, Ymem, ACx No 3 1 1 D unit register file MOV dbl(Lmem), pair(HI(ACx)) No 3 1 X D unit register file MOV dbl(Lmem), pair(LO(ACx)) No 3 1 X D unit register file MOV dbl(Lmem),pair(TAx) No 3 1 X A unit register file Accumulator, Auxiliary, or Temporary RegisterMOV src, dst Yes 2 1 X A or D unitAL U MOV HI(ACx), TAx Yes 2 1 X A unitAL UMOV TAx, HI(ACx) Yes 2 1 X D unitAL U Accumulator, Auxiliary, or Temporary RegisterMOV src, Smem No 2 1 X A or D unit register file MOV src, high_byte(Smem) No 3 1 X A or D unit register file MOV src,low_byte(Smem) No 2 1 X A or D unit register file MOV HI(ACx), Smem No 2 1 X D unit register file MOV [rnd()HI(ACx)[]], Smem No 3 1 X D unit register file MOV ACx << Tx, Smem No 3 1 X D unit register file MOV [rnd(]HI(ACx << Tx)[)], Smem No 3 1 X D unit register file MOV ACx << #SHIFTW, Smem No 3 1 X D unit register file MOV HI(ACx << #SHIFTW), Smem No 3 1 X D unit register file MOV [rnd()HI(ACx << #SHIFTW)[]], Smem No 4 1 X D unit register file MOV [uns(][rnd(]HI(saturate(ACx))[))], Smem No 3 1 X D unit register file MOV [uns(] [rnd(]HI(saturate(ACx << Tx))[))], Smem No 3 1 X D unit register file MOV [uns()(rnd()HI(saturate(ACx << #SHIFTW))[])], No 4 1 X D unit register file MOV ACx, dbl(Lmem) No 3 1 X D unit register file MOV [uns(]saturate(ACx)[)], dbl(Lmem) No 3 1 X D unit register file MOV ACx >> #1, dual(Lmem) No 3 1 X D unit register file MOV pair(HI(ACx)), dbl(Lmem) No 3 1 X D unit register file MOV pair(LO(ACx)), dbl(Lmem) No 3 1 X A unit register file MOV pair(TAx), dbl(Lmem) No 3 1 X D unit register file MOV ACx, Xmem, Ymem No 3 1 X D unit register file Memory DelayDELAY Smem No 3 1 X A or D unit register file Memory-to-Memory Move/Memory Initialization A or D unit register file MOV Cmem, Smem No 3 1 XMOV Smem, Cmem No 3 1 XMOV K8, Smem No 3 1 XMOV K16, Smem No 4 1 XMOV Cmem,dbl(Lmem) No 3 1 XMOV dbl(Lmem), Cmem No 3 1 XMOV dbl(Xmem), dbl(Ymem) No 3 1 XMOV Xmem, Ymem No 3 1 XPop Top of Stack (TOS) A or D unit register file POP dst1,dst2 Yes 2 1 XPOP Smem No 2 1 XPOP dbl(Lmem) No 2 1 XPush to Top of Stack (TOS) A or D unit register file PSH src1,src2 Yes 2 1 XPSH src Yes 2 1 XPSH src,Smem No 3 1 XPSH dbl(ACx) Yes 2 1 XPSH Smem No 2 1 XPSH dbl(Lmem) No 2 1 XSpecific CPU Register Load A or D unit register file MOV k12, BK03 Yes 3 1 ADMOV k12, BK47 Yes 3 1 ADMOV k12, BKC Yes 3 1 ADMOV k12, BRC0 Yes 3 1 ADMOV k12, BRC1 Yes 3 1 ADMOV k12, CSR Yes 3 1 ADMOV k7, DPH Yes 3 1 ADMOV k9, PDP Yes 3 1 ADMOV k16, BSA01 No 4 1 ADMOV k16, BSA23 No 4 1 ADMOV k16, BSA45 No 4 1 ADMOV k16, BSA67 No 4 1 ADMOV k16, BSAC No 4 1 ADMOV k16, CDP No 4 1 ADMOV k16, DP No 4 1 AD A or D unit register MOV k16, SP No 4 1 AD MOV k16, SSP No 4 1 ADMOV Smem, BK03No 3 1 XMOV Smem, BK47No 3 1 XMOV Smem, BKC No 3 1 XMOV Smem, BSA01 No 3 1 XMOV Smem, BSA23 No 3 1 XMOV Smem, BSA45 No 3 1 XMOV Smem, BSA67 No 3 1 XMOV Smem, BSAC No 3 1 XMOV Smem, BRC0 No 3 1 XMOV Smem, BRC1 No 3 1 XMOV Smem, CDP No 3 1 XMOV Smem, CSR No 3 1 XMOV Smem, DP No 3 1 XMOV Smem, DPH No 3 1 XMOV Smem, PDP No 3 1 XMOV Smem, SP No 3 1 XMOV Smem, SSP No 3 1 XSpecific CPU Register Move A unit ALUMOV TAx, BRC0Yes 2 1 XMOV TAx, BRC1Yes 2 1 XMOV TAx, CDP Yes 2 1 XMOV TAx, CSR Yes 2 1 XMOV TAx, SP Yes 2 1 XMOV TAx, SSP Yes 2 1 XMOV BRC0, TAx Yes 2 1 XMOV BRC1, TAx Yes 2 1 XMOV CDP, TAx Yes 2 1 XMOV RPTC, TAx Yes 2 1 XMOV SP, TAx Yes 2 1 XMOV SSP, TAx Yes 2 1 XSpecific CPU Register Store A or D unit register MOV BK03, Smem No 3 1 XMOV BK47, Smem No 3 1 XMOV BKC, Smem No 3 1 XMOV BSA01, Smem No 3 1 XMOV BSA23, Smem No 3 1 XMOV BSA45, Smem No 3 1 XMOV BSA67, Smem No 3 1 XMOV BSAC, Smem No 3 1 XMOV BRC0, Smem No 3 1 XMOV BRC1, Smem No 3 1 XMOV CDP, Smem No 3 1 XMOV CSR, Smem No 3 1 XMOV DP, Smem No 3 1 XMOV DPH, Smem No 3 1 XMOV PDP, Smem No 3 1 XMOV SP, Smem No 3 1 XMOV SSP, Smem No 3 1 XMOV TRN0, Smem No 3 1 XMOV TRN1, Smem No 3 1 XMOV RETA, dbl(Lmem) No 3 5 X§6.2算术指令语法并⾏使能bit长度周期流⽔线执⾏单元(⽮量距离)Absolute DistanceABDST Xmem, Ymem, ACx, ACy No 4 1 X(绝对值)Absolute ValueABS [src,] dst Yes 2 1 X A or D unit ALUADD Smem, [src,] dst No 3 1 X A or D unit ALU ADD ACx << Tx, ACy Yes 2 1 X D unit ALU & shifter ADD ACx <<#SHIFTW, ACy Yes 3 1 X D unit ALU & shifter ADD K16 << #16, [ACx,] ACy No 4 1 X D unit ALU ADD K16 << #SHFT, [ACx,] ACy No 4 1 X D unit ALU & shifter ADD Smem << Tx, [ACx,] ACy No 3 1 X D unit ALU & shifter ADD Smem << #16, [ACx,] ACy No 3 1 X D unit ALU ADD [uns(]Smem[)], CARRY, [ACx,] ACy No 3 1 X D unit ALU ADD [uns(]Smem[)], [ACx,]ACy No 3 1 X D unit ALU ADD [uns(]Smem[)] << #SHIFTW, [ACx,] ACy No 4 1 X D unit ALU & shifter ADD dbl(Lmem), [ACx,] ACy No 3 1 X D unit ALU ADD Xmem, Ymem, ACx No 3 1 X D unit ALU ADD K16, Smem No 4 1 X D unit ALU ADDV [ACx,] ACy Yes 2 1 X D unit MAC (⽐较)Compare and Select Extremum D unit ALU MAXDIFF ACx, ACy, ACz, ACw Yes 3 3 XDMAXDIFF ACx, ACy, ACz, ACw, TRNx Yes 3 1 XMINDIFF ACx, ACy, ACz, ACw Yes 3 1 XXDMINDIFF ACx, ACy, ACz, ACw, TRNx Yes 3 1 X(带条件加减法)Conditional Addition/SubtractionADDSUBCC Smem, ACx, TC1, ACy No 3 1 X D unit ALU ADDSUBCC Smem, ACx, TC2, ACy No 3 1 X D unit ALU ADDSUBCC Smem, ACx, TC1, TC2, ACy No 3 1 X D unit ALU ADDSUB2CC Smem, ACx, Tx, TC1, TC2, ACy No 3 1 X D unit shifter (带条件移位)Conditional ShiftSFTCC ACx, TCx Yes 2 1 X D unit shifter (带条件减法)Conditional SubtractSUBC Smem, [ACx,] ACy No 3 1 X D unit ALU 双16bit加减法Dual 16-Bit Arithmetic D unit ALU ADDSUB Tx, Smem, ACx No 3 1 XSUBADD Tx, Smem, ACx No 3 1 XADD dual(Lmem), [ACx,] ACy No 3 1 XSUB dual(Lmem), [ACx,] ACy No 3 1 XSUB ACx, dual(Lmem), ACy No 3 1 XSUB dual(Lmem), Tx, ACx No 3 1 XADD dual(Lmem), Tx, ACx No 3 1 XSUB Tx, dual(Lmem), ACx No 3 1 XADDSUB Tx, dual(Lmem), ACx No 3 1 XSUBADD Tx, dual(Lmem), ACx No 3 1 X并⾏乘法(Accumulate/Subtract) D unit MACs MPY[R][40] [uns()Xmem[]], [uns()Cmem[]], Acx∷MPY[R][40] [uns()Ymem[]], [uns()Cmem[)], ACy No 4 1 XMAC[R][40] [uns()Xmem[]], [uns()Cmem[]], AcxNo 4 1 X∷MPY[R][40] [uns()Ymem[]], [uns()Cmem[]], ACyMAS[R][40] [uns()Xmem[]], [uns()Cmem[]], AcxNo 4 1 X∷MPY[R][40] [uns()Ymem[]], [uns()Cmem[]], ACyAMAR XmemNo 4 1 X∷∷MAC[R][40] [uns()Ymem[]], [uns()Cmem[]], ACyAMAR XmemNo 4 1 X∷MAC[R][40] [uns()Ymem[]], [uns()Cmem[]], ACxMAS[R][40] [uns()Xmem[]], [uns()Cmem[]], AcxNo 4 1 X∷MAS[R][40] [uns()Ymem[]], [uns()Cmem[]], ACyAMAR XmemNo 4 1 X∷MAS[R][40] [uns()Ymem[]], [uns()Cmem[]], ACxMAC[R][40] [uns()Xmem[]], [uns()Cmem[]], ACx >> #16 ∷No 4 1 XMAC[R][40] [uns()Ymem[]], [uns()Cmem[]], ACyMPY[R][40] [uns()Xmem[]], [uns()Cmem[]], ACx∷MAC[40] [uns()Ymem[]], [uns()Cmem[]],ACy >> #16MAC[R][40] [uns()Xmem[]], [uns()Cmem[]], ACx >> 16∷No 4 1 XMAC[40] [uns()Ymem[]],[uns()Cmem[]],ACy >> #16MAS[R][40] [uns()Xmem[]], [uns()Cmem[]], ACxNo 4 1 X∷MAC[40] [uns()Ymem[]], [uns()Cmem[]],ACy >>#16 AMAR XmemNo 4 1 X∷MAC[40] [uns()Ymem[]], [uns()Cmem[]],ACx >> #16 AMAR Xmem, Ymem, Cmem No 4 1 XFinite Impulse Response Filter, Symmetrical/Antisymmetrical FIRSADD Xmem, Ymem, Cmem, ACx, ACyFIRSSUB Xmem, Ymem, Cmem, ACx, ACyImplied Paralleled InstructionsMPYM[R] [T3 = ]Xmem, Tx, ACyD unit MAC∷MOV HI(ACx << T2), Ymem No 4 1 XMACM[R] [T3 = ]Xmem, Tx, ACyD unit MAC∷MOV HI(ACx << T2), Ymem No 4 1 XMASM[R] [T3 = ]Xmem, Tx, ACyD unit MAC∷MOV HI(ACx << T2), Ymem No 4 1 XADD Xmem << #16, ACx, ACyD unit ALU∷MOV HI(ACy << T2), Ymem No 4 1 XSUB Xmem << #16, ACx, ACyD unit ALU∷MOV HI(ACy << T2), Ymem No 4 1 XMOV Xmem << #16, ACyD unit ALU∷MOV HI(ACx << T2), Ymem No 4 1 XMACM[R] [T3 = ]Xmem, Tx, AcxD unit MAC∷MOV Ymem << #16, ACy No 4 1 XMASM[R] [T3 = ]Xmem, Tx, AcxD unit MAC∷MOV Ymem << #16, ACy No 4 1 XLeast Mean Square (LMS)LMS Xmem, Ymem, ACx, ACy No 4 1 X D unit MAC &ALU Maximum Comparison MAX [src,] dst X A or D unit ALU Minimum ComparisonMIN [src,] dst X A or D unit ALU Memory Comparison A unit ALUCMP Smem == K16, TC1 No 4 1 XCMP Smem == K16, TC2 No 4 1 XAMOV TAx, TAy Yes 3 1 ADAADD k8, TAx Yes 3 1 ADASUB k8, TAx Yes 3 1 ADAMOV k8, TAx Yes 3 1 ADAMOV D16, TAx No 4 1 ADAMAR Smem No 2 1 ADModify Data Stack Pointer (SP)AADD K8, SP Yes 2 1 AD A unit ALUMultiply D unit MACSQR[R] [ACx,] ACy Yes 2 1 XMPY[R] [ACx,] ACy Yes 2 1 XMPY[R] Tx, [ACx,] ACy Yes 2 1 XMPYK[R] K8, [ACx,] ACy Yes 3 1 XMPYK[R] K16, [ACx,] ACy No 4 1 XMPYM[R] [T3 = ]Smem, Cmem, ACx No 3 1 XSQRM[R] [T3 = ]Smem, ACx No 3 1 XMPYM[R] [T3 = ]Smem, [ACx,] ACy No 3 1 XMPYMK[R] [T3 = ]Smem, K8, ACx No 4 1 XMPYM[R][40] [T3 = ][uns(]Xmem[)], [uns(]Ymem[)], ACx No 4 1 X MPYM[R][U] [T3 = ]Smem, Tx, ACx No 3 1 XMultiply and Accumulate (MAC) D unitMAC SQA[R] [ACx,] ACy Yes 2 1 XMAC[R] ACx, Tx, ACy[, ACy]Yes 2 1 XMAC[R] ACy, Tx, ACx, ACy Yes 2 1 XMACK[R] Tx, K8, [ACx,] ACy Yes 3 1 XMACK[R] Tx, K16, [ACx,] ACy N0 4 1 XMACM[R] [T3 = ]Smem, Cmem, ACx N0 3 1 XMACM[R]Z [T3 = ]Smem, Cmem, ACx N0 3 1 XSQAM[R] [T3 = ]Smem, [ACx,] ACy N0 3 1 XMACM[R] [T3 = ]Smem, [ACx,] ACy N0 3 1 XMACM[R] [T3 = ]Smem, Tx, [ACx,]N0 3 1 XMACMK[R] [T3 = ]Smem, K8, [ACx,] ACy N0 4 1 XMACM[R][40] [T3 = ][uns()Xmem[]], [uns()Ymem[]][ACx,]N0 4 1 XACyMACM[R][40] [T3 = ][uns()Xmem[]], [uns()Ymem[]]ACx >>N0 4 1 X#16[, ACy]Multiply and Subtract (MAS) D unitMAC SQS[R] [ACx,] ACy Yes 2 1 XMAS[R] Tx, [ACx,] ACy Yes 2 1 XMASM[R] [T3 = ]Smem, Cmem, ACx N0 3 1 XSQSM[R] [T3 = ]Smem, [ACx,] ACy N0 3 1 XMASM[R] [T3 = ]Smem, [ACx,] ACy N0 3 1 XMASM[R] [T3 = ]Smem, Tx, [ACx,] ACy N0 3 1 XMASM[R][40] [T3 = ][uns()Xmem[]], [uns()Ymem[]][ACx,]N0 4 1 XACyNormalization ALU& D unit shifter MANT ACx, ACyYes 3 1 XCMP[U] src RELOP dst, TCx Yes 3 1 XCMPAND[U] src RELOP dst, TCy, TCx Yes 3 1 XCMPAND[U] src RELOP dst, !TCy, TCx Yes 3 1 XCMPOR[U] src RELOP dst, TCy, TCx Yes 3 1 XCMPOR[U] src RELOP dst, !TCy, TCx Yes 3 1 XRoundROUND [ACx,] ACy Yes 2 1 X D unit ALU SaturateSAT[R] [ACx,] ACy Yes 2 1 X D unit ALU Signed ShiftSFTS dst, #–1 Yes 2 1 X ALU or D unitshifter SFTS dst, #1 Yes 2 1 X ALU or D unitshifter SFTS ACx, Tx[, ACy] Yes 2 1 X D unit shifter SFTSC ACx, Tx[, ACy] Yes 2 1 X D unit shifter SFTS ACx, #SHIFTW[, ACy] Yes 3 1 X D unit shifter SFTSC ACx, #SHIFTW[, ACy] Yes 3 1 X D unit shifter Square DistanceSQDST Xmem, Ymem, ACx, ACy No 4 1 X D unit MAC & ALU SubtractionSUB [src,] dst Yes 2 1 X A or D unit ALU SUB k4, dst Yes 2 1 X A or D unit ALU SUB K16, [src,] dst No 4 1 X A or D unit ALU SUB Smem, [src,] dst No 3 1 X A or D unit ALU SUB src, Smem, dst No 3 1 X A or D unit ALU SUB ACx << Tx, ACy Yes 2 1 X D unit ALU & shifter SUB ACx << #SHIFTW, ACy Yes 3 1 X D unit ALU,shifter SUB K16 << #16, [ACx,] ACy No 4 1 X D unit ALUSUB K16 << #SHFT, [ACx,] ACy No 4 1 X D unit ALU, shifter SUB Smem << Tx, [ACx,] ACy No 3 1 X D unit ALU, shifter SUB Smem << #16, [ACx,] ACy No 3 1 X D unit ALUSUB ACx, Smem << #16, ACy No 3 1 X D unit ALUSUB [uns(]Smem[)], BORROW, [ACx,] ACy No 3 1 X D unit ALUSUB [uns(]Smem[)], [ACx,] ACy No 3 1 X D unit ALUSUB [uns(]Smem[)] << #SHIFTW, [ACx,] ACy No 4 1 X D unit ALU,shifter SUB dbl(Lmem), [ACx,] ACy No 3 1 X D unit ALU SUB ACx, dbl(Lmem), ACy No 3 1 X D unit ALUSUB Xmem, Ymem, ACx No 3 1 X D unit ALU§6.3程序控制指令语法并⾏使能bit长度周期流⽔线Branch ConditionallyBCC l4, cond No 2 6/5 R BCC L8, cond Yes 3 6/5 R BCC L16, cond No 4 6/5 RB ACx No 2 10 X B L7 Yes 2 6?AD B L16 Yes 2 6?AD B P24 No 4 5 D Branch on Auxiliary Register Not ZeroBCC L16, ARn_mod ! = #0 No 4 6/5 AD Call ConditionallyCALLCC L16, cond No 4 6/5 R CALLCC P24, cond No 5 5/5 R Call UnconditionallyCALL ACx No 2 10 X CALL L16 Yes 36AD CALL P24 No45D Compare and BranchBCC[U] L8, src RELOP K8 No 4 7/6 X Execute ConditionallyXCC [label, ]cond No 2 1 AD XCCPART [label, ]cond No21X IdleIDLE No 4 ? D No Operation (NOP)NOP Yes 1 1 D NOP_16 Yes21D Repeat Block of Instructions UnconditionallyRPTBLOCAL pmad Yes 2 1 AD RPTB pmad Yes31AD Repeat Single Instruction ConditionallyRPTCC k8, cond Yes3 1 AD Repeat Single Instruction UnconditionallyRPT CSR Yes 2 1 AD RPTADD CSR, TAx Yes 2 1 X RPT k8 Yes 2 1 AD RPTADD CSR, k4 Yes 2 1 X RPTSUB CSR, k4Yes 2 1 X RPT k16 Yes 3 1 AD Return ConditionallyRETCC cond Yes 3 5/5 R Return UnconditionallyRET Yes 2 5 D Return from InterruptRETI Yes 2 5 D Software InterruptINTR k5 No 2 3 DTRAP k5 No 2 ? D疑难指令描述Absolute Distance (ABDST)ABDST Xmem,Ymem,ACx,Acy 并⾏完成以下操作ACy = ACy + |HI(ACx)|>>16ACx = (Xmem << #16) – (Ymem << #16)影响状态bit位:FRCT, C54CM, M40, SATD, SXMD Affects ACOVx, ACOVy, CARRY ABDST *AR0+,*AR1,AC0,AC1 Before AfterAC0 00 1234 0000 AC0 00 4500 0000AC1 00 E800 0000 AC1 00 E800 1234AR0 202 AR0 203AR1 302 AR1 302202 3400 202 3400302 EF00 302 EF00●MAXDIFF ACx, ACy, ACz, AcwTRN0 = TRN0 >> #1TRN1 = TRN1 >> #1ACw(39–16) = ACy(39–16) – ACx(39–16) ←分段减ACw(15–0) = ACy(15–0) – ACx(15–0)←分段减If (ACx(31–16) > ACy(31–16)) { bit(TRN0, 15) = #0 ; ACz(39–16) = ACx(39–16) }else { bit(TRN0, 15) = #1 ; ACz(39–16) = ACy(39–16) }if (ACx(15–0) > ACy(15–0)) { bit(TRN1, 15) = #0 ; ACz(15–0) = ACx(15–0) }else { bit(TRN1, 15) = #1 ; ACz(15–0) = ACy(15–0) }MAXDIFF AC0, AC1, AC2, AC1Before AfterAC0 10 2400 2222 AC0 10 2400 2222AC1 90 0000 0000 AC1 7F DC00 DDDEAC2 00 0000 0000 AC2 10 2400 2222TRN0 1000 TRN0 0800TRN1 0100 TRN1 0080●DMAXDIFF ACx, ACy, ACz, AcwIf M40 = 0:TRNx = TRNx >> #1ACw(39–0) = ACy(39–0) – ACx(39–0)If (ACx(31–0) > ACy(31–0)) { bit(TRNx, 15) = #0 ; ACz(39–0) = ACx(39–0) }else { bit(TRNx, 15) = #1 ; ACz(39–0) = ACy(39–0) }ACw(39–0) = ACy(39–0) – ACx(39–0)If (ACx(39–0) > ACy(39–0)) { bit(TRNx, 15) = #0 ; ACz(39–0) = ACx(39–0) } else { bit(TRNx, 15) = #1 ; ACz(39–0) = ACy(39–0) }ADDV [ACx,] ACyACx⾼16bit(32-16)的绝对值与ACy的值相加,结果存于ACy中。