LeadFrame Etch 制程简介

- 格式:ppt

- 大小:4.25 MB

- 文档页数:35

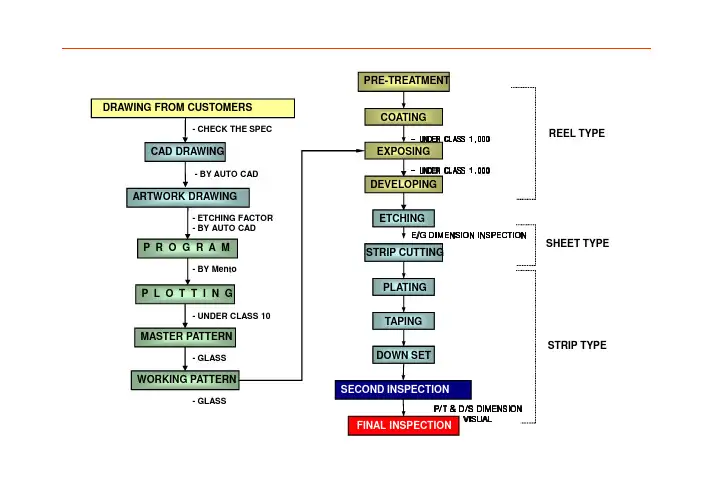

CAD DRAWINGDRAWING FROM CUSTOMERSARTWORK DRAWING-CHECK THE SPEC-BY AUTO CAD-ETCHING FACTOR -BY AUTO CADPRE-TREATMENTCOATINGEXPOSINGETCHINGREEL TYPESHEET TYPE-UNDER CLASS 1,000-UNDER CLASS 1,000E/G DIMENSION INSPECTIONDEVELOPINGP R O G R A MP L O T T I N GMASTER PATTERNWORKING PATTERN-UNDER CLASS 10-GLASS-BY Mento-GLASSNGSTRIP CUTTING PLATING TAPING DOWN SETSTRIP TYPEP/T & D/S DIMENSIONVISUALSECOND INSPECTIONFINAL INSPECTIONINPUTClean & RinsePR Coating & OUTPUTClean & PR Coating1. Purpose: Photo resist : Material2. Process FlowInput → Removing Dust & Oil (Alkali) → Acid Zone (HNO 3)→ Neutral Zone → Coating Zone → Dry Zone → Output☞TO ELEVATE CONTACTIVITY OF PR BY SURFACECLEANING & SURFACE TREATMENT☞TO COAT STRONG ANTI-ACIDITY RESIST AGAINST FeCl 3INPUTExposingOUTPUTExposing1. Purpose: Photo resist : Material UV Lamp: W/P Glass☞TO DIVIDE INTO EXPOSED & NON-EXPOSED PARTON PHOTO-RESIST BY ULTRA-VIOLET LIGHT -EXPOSED PART : WATER-INSOLUABLE -NON-EXPOSED PART : WATER-SOLUABLE2. Process FlowInput → Loading → Vacuum → Exposing →Non Vacuum → Unloading → Transfer → OutputINPUTDEVELOPINGDRY &OUTPUTDeveloping: Photo resist : Material1. Purpose2. Process FlowInput → Developing → PR Hardening → Dry → Output☞TO REMOVE NON-EXPOSED PART BY HOTINDUSTRIAL WATER☞TO GIVE STRONG ANTI-ACIDITY & HARDNESSTO EXPOSED PART(LOW MATERIAL): Photo resist: Material Etching1. Purpose2. Process Flow FeCl3☞TO SHAPE PRODUCT BY ERODING THE NON-EXPOSED SURFACE(LOW MATERIAL)☞TO STRIP THE WATER-INSOLUABLE PHOTO-RESIST BY SWELLING METHOD AFTER ETCHING -Process for making the figure of lead frame by melting the material with spraying the chemical solution on the surface of the material which the design of the product was printed.Sheet Loading → Pre-Etching → Etching → Stripping → Neutralization → Anti-Rust → Dry→ Sheet UnloadingSPOT PLATINGRING PLATINGPlatingDOUBLE RING PLATING2. Process Flow☞PROCESS FOR PLATING THE SILVER ON THE LEAD TIP FOR BONDING THE GOLD WIREIN THE ASSEMBLY PROCESS OF THE SEMICONDUCTOR.Strip Loading → Clean Activator → Chemical Polishing → Cu-strike → Anti-immersion → Ag Plating → Stripping → Rinse → Dry → Strip Unloading1. PurposeTaping ToolDown setting2. Process Flow☞PROCESS FOR DEPRESSING THE PAD TO PUT THE CHIP ON AND ATTACHING THE TAPETO PREVENT THE LEAD FROM DEFORMATION IN THE ASSEMBLY OF SEMICONDUCTOR.Loading → Taping(Taping Tool) → Down setting(D/S Tool)→ Unloading 1. PurposeTie barPadQ F P2. Process Flow☞PROCESS FOR DETECT A DEFECT BY AUTOMATIC INSPECTION MACHINE AND HUMANBEING(MIMENSION AND VISUAL)Loading → Auto Inspection(Dimension/Visual) → Unloading → Visual Inspection → OQC 1. PurposeQ F P。

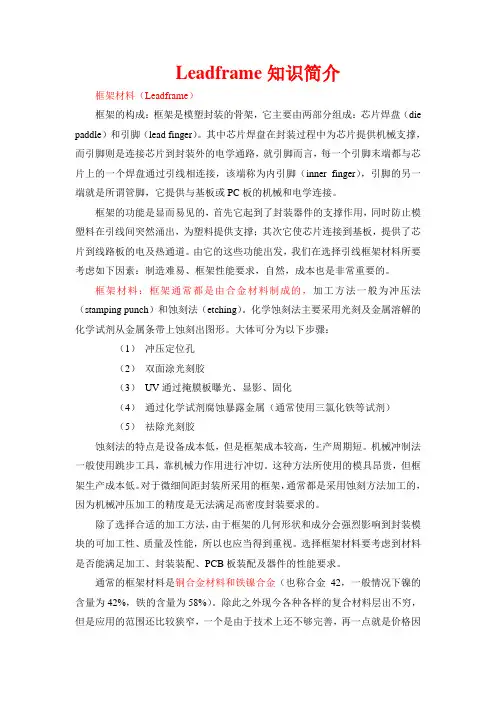

Leadframe知识简介框架材料(Leadframe)框架的构成:框架是模塑封装的骨架,它主要由两部分组成:芯片焊盘(die paddle)和引脚(lead finger)。

其中芯片焊盘在封装过程中为芯片提供机械支撑,而引脚则是连接芯片到封装外的电学通路,就引脚而言,每一个引脚末端都与芯片上的一个焊盘通过引线相连接,该端称为内引脚(inner finger),引脚的另一端就是所谓管脚,它提供与基板或PC板的机械和电学连接。

框架的功能是显而易见的,首先它起到了封装器件的支撑作用,同时防止模塑料在引线间突然涌出,为塑料提供支撑;其次它使芯片连接到基板,提供了芯片到线路板的电及热通道。

由它的这些功能出发,我们在选择引线框架材料所要考虑如下因素:制造难易、框架性能要求,自然,成本也是非常重要的。

框架材料:框架通常都是由合金材料制成的,加工方法一般为冲压法(stamping punch)和蚀刻法(etching)。

化学蚀刻法主要采用光刻及金属溶解的化学试剂从金属条带上蚀刻出图形。

大体可分为以下步骤:(1)冲压定位孔(2)双面涂光刻胶(3)UV通过掩膜板曝光、显影、固化(4)通过化学试剂腐蚀暴露金属(通常使用三氯化铁等试剂)(5)祛除光刻胶蚀刻法的特点是设备成本低,但是框架成本较高,生产周期短。

机械冲制法一般使用跳步工具,靠机械力作用进行冲切。

这种方法所使用的模具昂贵,但框架生产成本低。

对于微细间距封装所采用的框架,通常都是采用蚀刻方法加工的,因为机械冲压加工的精度是无法满足高密度封装要求的。

除了选择合适的加工方法,由于框架的几何形状和成分会强烈影响到封装模块的可加工性、质量及性能,所以也应当得到重视。

选择框架材料要考虑到材料是否能满足加工、封装装配、PCB板装配及器件的性能要求。

通常的框架材料是铜合金材料和铁镍合金(也称合金42,一般情况下镍的含量为42%,铁的含量为58%)。

除此之外现今各种各样的复合材料层出不穷,但是应用的范围还比较狭窄,一个是由于技术上还不够完善,再一点就是价格因素。

![[工艺]ETCHprocess的大师级讲解](https://uimg.taocdn.com/330e8ed8846a561252d380eb6294dd88d0d23d0b.webp)

[工艺]ETCHprocess的大师级讲解编者注: Etch是PIE不得不好好学习的课程,玄机太多了。

我曾经花太多时间研究这玩意,结果连皮毛都碰不上,每次跟人家讨论还是云里雾里~~~感谢Joph Chen,曾经的ETCH专家。

如果把黄光比作是拍照,那他就是完成了底片的功能,还需要蚀刻来帮忙把底片的图像转移到Wafer上。

蚀刻通常分为Wet Etch(湿蚀刻)和Dry Etch (干蚀刻),湿蚀刻主要各向同性蚀刻(Isotropic),所以profile是横向等于纵向,但是througput比较快,选择比高,而且陈本低。

我们在8寸制程的湿蚀刻都是用来做strip,只有dual gate etch 或者Silicide前面的RPO的Dry+Wet。

这两个都是尺寸比较大,而且不能直接用plasma轰击Si。

而干蚀刻主要用plasma离化反应气体(RIE: Reactived Ionized Etch),与被蚀刻物质反应成气态副产物被抽走(反应副产物一定的是气体,所以Cu制程无法用蚀刻。

),主要用来吃小pattern的,因为他的各向异性(Anisotropic)优点,但是他的制程复杂,tune recipe factor非常困难,价格昂贵。

需要澄清一点,干蚀刻的anisotropic的各项异性,不是指他吃的时候侧边就不会吃,是因为process会产生一种叫做polymer的物质,保护在侧壁使得侧边不会被吃掉。

polymer的形成主要靠F-C比(氟-碳比),来控制polymer多少来进一步控制profile (F-base的比例比C-base的比例多还是少?)蚀刻制程必须了解plasma,啥是plasma?说白了就是一群被充电了的准中性气体(类似闪电),其实就是一锅等离子汤(电浆)。

在这锅汤里有电子(elctrons)的雪崩碰撞(Avalanche)用于产生和维持等离子体汤,碰撞产生的离子Ions在电场的作用下撞击(bombardment)晶园表面也达到物理蚀刻的目的,如Ar+ e -->Ar* or Ar+ 和两个电子,而另一部分被离化的ions可以作为化学反应气体,与被蚀刻物质发生化学反应产生气态副产物达到化学蚀刻的目的(如CF4+e-->CFx[+] + Fx[-] + e, F[-]+Si-->SiFx(g) )。

引线框架(Leadframe):

2010-05-04 14:38:13| 分类:铜带应用:引线框 | 标签:引线引脚 leadframe 框架集成电路|字号订阅

引线框架作为集成电路的芯片载体,是一种借助于键合金丝实现芯片内部电路引出端与外引线的电气连接,形成电气回路的关键结构件,它起到了和外部导线连接的桥梁作用,绝大部分的半导体集成块中都需要使用引线框架,是电子信息产业中重要的基础材料。

产品类型有TO、DIP、ZIP、SIP、SOP、SSOP、QFP(QFJ)、SOD、SOT等。

主要用模具冲压法

和化学刻蚀法进行生产。

lead frame / 中文:引脚架,引线架

各种有密封主体及多双引脚的电子元件,如各种IC、网状电阻器或简单的二极管、三极管等,其主体中心与各引脚所暂时隔离固定的金属架,即为

脚架,又可称为定架。

其封装过程是,将中心部分的品片背面的金层或银层,利用高温熔接法与脚架中心的镀金层加以固定,再用金线或铝线从已焊牢固晶片的电极点与各引脚之间打线连通,然后再将整个主体用塑胶或玻璃封牢,并剪去脚架外框,并进一步弯脚成形以方便插焊或贴焊,即可得到所需的元件。

脚架在电子封装工业中占有很重要的地位,其合金材料常用Kovar、Alloy 42 及磷青铜等,脚架成形的方式有模具冲切法及化学蚀刻法等。

Leadframe知识简介框架材料(Leadframe)框架的构成:框架是模塑封装的骨架,它主要由两部分组成:芯片焊盘(die paddle)和引脚(lead finger)。

其中芯片焊盘在封装过程中为芯片提供机械支撑,而引脚则是连接芯片到封装外的电学通路,就引脚而言,每一个引脚末端都与芯片上的一个焊盘通过引线相连接,该端称为内引脚(inner finger),引脚的另一端就是所谓管脚,它提供与基板或PC板的机械和电学连接。

框架的功能是显而易见的,首先它起到了封装器件的支撑作用,同时防止模塑料在引线间突然涌出,为塑料提供支撑;其次它使芯片连接到基板,提供了芯片到线路板的电及热通道。

由它的这些功能出发,我们在选择引线框架材料所要考虑如下因素:制造难易、框架性能要求,自然,成本也是非常重要的。

框架材料:框架通常都是由合金材料制成的,加工方法一般为冲压法(stamping punch)和蚀刻法(etching)。

化学蚀刻法主要采用光刻及金属溶解的化学试剂从金属条带上蚀刻出图形。

大体可分为以下步骤:(1)冲压定位孔(2)双面涂光刻胶(3)UV通过掩膜板曝光、显影、固化(4)通过化学试剂腐蚀暴露金属(通常使用三氯化铁等试剂)(5)祛除光刻胶蚀刻法的特点是设备成本低,但是框架成本较高,生产周期短。

机械冲制法一般使用跳步工具,靠机械力作用进行冲切。

这种方法所使用的模具昂贵,但框架生产成本低。

对于微细间距封装所采用的框架,通常都是采用蚀刻方法加工的,因为机械冲压加工的精度是无法满足高密度封装要求的。

除了选择合适的加工方法,由于框架的几何形状和成分会强烈影响到封装模块的可加工性、质量及性能,所以也应当得到重视。

选择框架材料要考虑到材料是否能满足加工、封装装配、PCB板装配及器件的性能要求。

通常的框架材料是铜合金材料和铁镍合金(也称合金42,一般情况下镍的含量为42%,铁的含量为58%)。

除此之外现今各种各样的复合材料层出不穷,但是应用的范围还比较狭窄,一个是由于技术上还不够完善,再一点就是价格因素。

单晶硅锭(Ingot):圆柱形,重量约100Kg,硅纯度99.9999%。

晶圆切割(W afe r):直径含6英寸、12英寸、18英寸,表面光亮,完美无暇。

光刻(Photo):平面型晶体管和集成电路生产中的一个主要工艺。

是对半导体晶片表面的掩蔽物(如二氧化硅)进行开孔,以便进行杂质的定域扩散的一种加工技术。

蚀刻(Etching):按照掩模图形或设计要求对半导体衬底表面或表面覆盖薄膜进行选择性腐蚀或剥离。

刻蚀技术不仅是半导体器件和集成电路的基本制造工艺,而且还应用于薄膜电路、印刷电路和其他微细图形的加工。

刻蚀还可分为湿法刻蚀和干法刻蚀。

分层(Level):通过重复影印和蚀刻,形成多层的机构,AMD已达到9层。

封装(Package):安装半导体集成电路芯片用的外壳,起着安放、固定、密封、保护芯片和增强电热性能的作用,而且还是沟通芯片内部世界与外部电路的桥梁。

芯片封装类型包含双列直插DIP、贴片PLC C与TQFP、SOP、TSOP、PQFP、LGA、PGA、BGA。

测试(Final Te st):确保芯片满足设计的各项功能。

半导体制造工艺流程N型硅:掺入V族元素--磷P、砷As、锑SbP型硅:掺入III族元素—镓Ga、硼BPN结:半导体元件制造过程可分为前段(FrontEnd)制程晶圆处理制程(WaferFabrication;简称WaferFab)、晶圆针测制程(WaferProbe);後段(BackEnd)构装(Packaging)、测试制程(InitialTestandFinalTest)一、晶圆处理制程晶圆处理制程之主要工作为在矽晶圆上制作电路与电子元件(如电晶体、电容体、逻辑闸等),为上述各制程中所需技术最复杂且资金投入最多的过程,以微处理器(Microprocessor)为例,其所需处理步骤可达数百道,而其所需加工机台先进且昂贵,动辄数千万一台,其所需制造环境为为一温度、湿度与含尘(Particle)均需控制的无尘室(Clean-Room),虽然详细的处理程序是随着产品种类与所使用的技术有关;不过其基本处理步骤通常是晶圆先经过适当的清洗(Cleaning)之後,接着进行氧化(Oxidation)及沈积,最後进行微影、蚀刻及离子植入等反覆步骤,以完成晶圆上电路的加工与制作。

二、晶圆针测制程经过WaferFab之制程後,晶圆上即形成一格格的小格,我们称之为晶方或是晶粒(Die),在一般情形下,同一片晶圆上皆制作相同的晶片,但是也有可能在同一片晶圆上制作不同规格的产品;这些晶圆必须通过晶片允收测试,晶粒将会一一经过针测(Probe)仪器以测试其电气特性,而不合格的的晶粒将会被标上记号(InkDot),此程序即称之为晶圆针测制程(WaferProbe)。

然後晶圆将依晶粒为单位分割成一粒粒独立的晶粒三、IC构装制程IC构装制程(Packaging):利用塑胶或陶瓷包装晶粒与配线以成积体电路目的:是为了制造出所生产的电路的保护层,避免电路受到机械性刮伤或是高温破坏。

半导体制造工艺分类半导体制造工艺分类一双极型IC的基本制造工艺:A在元器件间要做电隔离区(PN结隔离、全介质隔离及PN结介质混合隔离)ECL(不掺金)(非饱和型)、TTL/DTL(饱和型)、STTL(饱和型)B在元器件间自然隔离I2L(饱和型)半导体制造工艺分类二MOSIC的基本制造工艺:根据栅工艺分类A铝栅工艺B硅栅工艺其他分类1、(根据沟道)PMOS、NMOS、CMOS2、(根据负载元件)E/R、E/E、E/D半导体制造工艺分类三Bi-CMOS工艺:A以CMOS工艺为基础P阱N阱B以双极型工艺为基础双极型集成电路和MOS集成电路优缺点半导体制造环境要求主要污染源:微尘颗粒、中金属离子、有机物残留物和钠离子等轻金属例子。