时序电路的分析和设计共32页

- 格式:ppt

- 大小:2.47 MB

- 文档页数:16

时序逻辑电路的状态图与状态表分析方法时序逻辑电路是一种在特定时间下根据输入信号的状态而改变输出信号的电路。

对于复杂的时序逻辑电路,为了更好地理解和分析其行为,我们可以使用状态图和状态表这两种分析方法。

一、状态图分析方法状态图是时序逻辑电路的状态及其转换之间关系的图形化表示。

它通常由一个或多个状态框和状态转换线组成。

1. 状态框:状态框代表一个特定的状态,一般用一个圆形或椭圆形表示,内部标识状态的名称。

2. 状态转换线:状态转换线表示状态之间的转换关系,一般用带箭头的直线表示。

箭头指向的状态表示由当前状态经过某个输入信号的改变而转换到的新状态。

绘制状态图的步骤如下:1. 根据时序逻辑电路的功能和要求,确定可能存在的状态数量及其命名。

2. 确定输入信号的类型和数量,并将其标记在状态图中。

3. 分析每个状态与输入信号之间的状态转换关系,并将其用状态转换线表示。

4. 绘制出完整的状态图。

通过观察状态图,我们可以清楚地了解时序逻辑电路的状态之间的转换关系,并可以判断其行为是否符合设计要求。

二、状态表分析方法状态表是一种简洁而直观的分析方法,它是将时序逻辑电路的各个状态及其输入信号和输出信号以表格形式表示出来。

状态表可以清晰地展示电路的状态转换规律。

状态表的组成如下:1. 状态列:表示电路的各个状态。

2. 输入列:表示输入信号的情况。

3. 输出列:表示输出信号的情况。

绘制状态表的步骤如下:1. 确定输入信号及其取值范围,并编写对应的输入列。

2. 确定状态之间的转换关系,并记录在状态表的状态列中。

3. 分析每个状态下的输出信号,并在输出列中进行记录。

通过状态表的分析,我们可以准确地了解每个状态下输入信号和输出信号的对应关系,并可以找出其中的规律,以进一步优化电路的设计和实现。

综上所述,时序逻辑电路的状态图与状态表分析方法是两种常用且有效的分析工具。

通过状态图和状态表的绘制和分析,我们可以更好地理解时序逻辑电路的行为,并能够进行合理的电路设计和调试。

数电习题及答案(总32页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--一、时序逻辑电路与组合逻辑电路不同,其电路由组合逻辑电路和存储电路(触发器)两部分组成。

二、描述同步时序电路有三组方程,分别是驱动方程、状态方程和输出方程。

三、时序逻辑电路根据触发器的动作特点不同可分为同步时序逻辑电路和异步时序逻辑电路两大类。

四、试分析图时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图。

解:驱动方程:001101J KJ K Q====状态方程:100111010nnQ QQ Q Q Q Q++==+输出方程:10Y Q Q=状态图:功能:同步三进制计数器五、试用触发器和门电路设计一个同步五进制计数器。

解:采用3个D触发器,用状态000到100构成五进制计数器。

(1)状态转换图(2)状态真值表(3)求状态方程(4)驱动方程(5)逻辑图(略)[题] 分析图所示的时序电路的逻辑功能,写出电路驱动方程、状态转移方程和输出方程,画出状态转换图,并说明时序电路是否具有自启动性。

解:触发器的驱动方程2001021010211J Q K J Q J QQ K Q K ====⎧⎧⎧⎨⎨⎨==⎩⎩⎩ 触发器的状态方程120011010112210n n n Q Q Q Q Q Q Q Q Q Q Q Q +++==+=⎧⎪⎪⎨⎪⎪⎩输出方程 2Y Q = 状态转换图如图所示所以该电路的功能是:能自启动的五进制加法计数器。

[题] 试分析图时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,并检查电路能否自启动。

解:驱动方程输出方程 状态方程状态转换图如图 所示功能:所以该电路是一个可控的3进制计数器。

[题] 分析图时序电路的功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,并检查电路能否自启动。

时序逻辑电路的设计与时序分析方法时序逻辑电路是数字电路中的一种重要类型,用于处理按时间顺序发生的事件。

它在各种电子设备中被广泛应用,例如计算机、通信设备等。

本文将介绍时序逻辑电路的设计原理和常用的时序分析方法。

一、时序逻辑电路的设计原理时序逻辑电路是根据输入信号的状态和时钟信号的边沿来确定输出信号的状态。

它的设计原理包括以下几个方面:1. 状态转移:时序逻辑电路的状态是通过状态转移实现的。

状态转移可以使用触发器实现,触发器是一种存储元件,能够存储和改变信号的状态。

常见的触发器有D触发器、JK触发器等。

2. 时钟信号:时序逻辑电路中的时钟信号是控制状态转移的重要信号。

时钟信号通常为周期性的方波信号,它的上升沿或下降沿触发状态转移操作。

3. 同步与异步:时序逻辑电路可以是同步的或异步的。

同步电路通过时钟信号进行状态转移,多个状态转移操作在同一时钟周期内完成。

异步电路不需要时钟信号,根据输入信号的状态直接进行状态转移。

二、时序分析方法时序分析是对时序逻辑电路的功能和性能进行分析的过程,它可以帮助设计人员检查和验证电路的正确性和可靠性。

以下是几种常用的时序分析方法:1. 序时关系图:序时关系图是一种图形表示方法,它直观地显示了输入信号和输出信号之间的时间关系。

通过分析序时关系图,可以确定电路的特性,例如最小延迟时间、最大延迟时间等。

2. 状态表和状态图:状态表是对时序逻辑电路状态转移过程的描述表格,其中包括当前状态、输入信号和下一个状态的对应关系。

状态图是对状态表的图形化表示,用图形的方式展示状态和状态转移之间的关系。

3. 时钟周期分析:时钟周期分析是对时序逻辑电路的时钟频率和时钟周期进行分析,以确保电路能够在规定的时钟周期内完成状态转移操作。

常用的时钟周期分析方法包括最小周期分析和最大频率分析。

4. 时序仿真:时序仿真是通过计算机模拟时序逻辑电路的行为来验证电路的功能和性能。

通过输入不同的信号序列,可以观察和分析电路的输出响应,以判断电路设计是否正确。

电子设计中的时序电路设计

时序电路是电子设计中非常重要的一部分,它用于控制信号在电子系统中的时

序和顺序。

时序电路的设计涉及到时钟信号的分配、同步和延迟等方面,是确保整个系统正常工作的关键因素。

在进行时序电路设计时,首先需要明确系统的时钟信号源以及时钟频率。

时钟

信号是整个系统中的主导信号,它决定了数据的传输速度和时序关系。

因此,在设计时需要保证时钟信号的稳定性和准确性,避免产生时序偏差和时序冲突。

另外,在时序电路设计中,时序分析是必不可少的一步。

时序分析可以帮助设

计人员理清系统中各模块之间的时序关系,确定数据传输的路径和时序要求。

通过时序分析,可以发现潜在的时序问题,并及时进行调整和优化,确保系统的可靠性和稳定性。

此外,在时序电路设计中,还需要考虑时序同步和时序延迟的问题。

时序同步

是指保证不同模块之间的时序一致性,避免数据传输过程中出现时序不匹配的情况。

而时序延迟则关系到数据在不同模块之间的传输速度和时序关系,需要设计合适的延迟电路来保证数据的正确接收和传输。

总的来说,时序电路设计是电子设计中至关重要的一环,它直接关系到整个系

统的性能和稳定性。

设计人员需要充分理解时序电路的原理和设计要求,合理规划时序分配和时序关系,通过时序分析和验证确保系统的正常工作。

只有做好时序电路设计,才能保证整个电子系统的可靠性和性能优化。

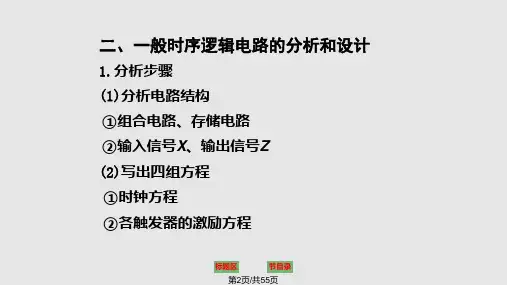

时序逻辑电路的分析和设计

[教学目的和要求]

通过本讲的学习,使学生掌握时序逻辑电路的定义及同步时序电路的分析与设计方法;深刻理解时序电路各方程组(输出方程组、驱动方程组、状态方程组),状态转换表、状态转换图及时序图在分析和设计时序电路中的重要作用。

[教学内容]

1.同步时序电路的分析方法

2.同步时序电路的设计方法

3.异步时序电路

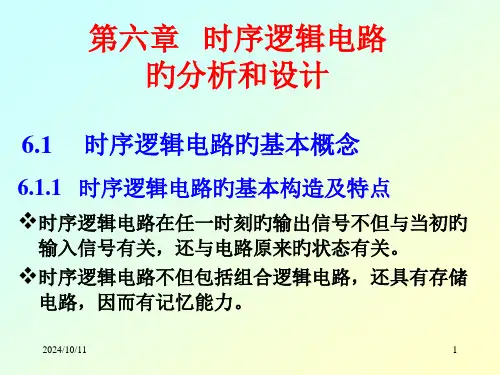

6.1 时序逻辑电路概述

1、时序电路的结构与特点

2、时序电路的分类

(1)根据时钟分类――同步时序电路、异步时序电路

(2)根据输出分类――米利型时序电路、穆尔型时序电路

3、时序电路逻辑功能的表示方法

逻辑表达式、状态表、卡诺图、状态图、时序图和逻辑图

6.2 时序逻辑电路的分析方法

1.时序电路的分析步骤:

2.具体实例讲解――同步分析例1:

例2:P217

例3:P219

3.具体实例讲解――异步分析P221,课本例6.2.3

具体方法总结

6.3 同步时序逻辑电路的设计方法

1.设计步骤

2.具体例题讲解

例1:设计一个按自然态序变化的7进制同步加法计数器,计数规则为“逢七进一”,产生一个进位输出。

例2:设计一个带进位输出端的十三进制计数器。

课本例题:例1:试设计一序列脉冲检测器,当连续输入信号110时,该电路输出为1,否则输出为0。

图6.3.2 原始状态图。