第3章Verilog设计入门

- 格式:ppt

- 大小:1.20 MB

- 文档页数:15

VerilogHDL培训教程——华为第一章:引言随着电子设计自动化(EDA)技术的不断发展,硬件描述语言(HDL)在数字电路设计领域扮演着越来越重要的角色。

VerilogHDL 作为一种主流的硬件描述语言,因其强大的功能、灵活的语法和广泛的应用范围,已成为数字集成电路设计工程师必备的技能之一。

本教程旨在帮助读者掌握VerilogHDL的基本概念、语法和设计方法,为华为等企业培养合格的数字电路设计人才。

第二章:VerilogHDL基础2.1VerilogHDL简介VerilogHDL是一种用于数字电路设计的硬件描述语言,它可以在多个层次上对数字系统进行描述,包括算法级、寄存器传输级(RTL)、门级和开关级。

VerilogHDL的设计初衷是为了提高数字电路设计的可重用性、可移植性和可维护性。

2.2VerilogHDL编程环境(1)文本编辑器:Notepad++、SublimeText等;(2)仿真工具:ModelSim、IcarusVerilog等;(3)综合工具:XilinxISE、AlteraQuartus等。

2.3VerilogHDL语法基础(1)关键字:VerilogHDL中的关键字具有特定含义,如module、endmodule、input、output等;(2)数据类型:包括线网类型(wire)、寄存器类型(reg)、整数类型(integer)等;(3)运算符:包括算术运算符、关系运算符、逻辑运算符等;(4)模块与端口:模块是VerilogHDL设计的基本单元,端口用于模块之间的信号传递;(5)行为描述与结构描述:行为描述用于描述电路的功能,结构描述用于描述电路的结构。

第三章:VerilogHDL设计流程3.1设计流程概述(1)需求分析:明确设计任务和功能要求;(2)模块划分:根据需求分析,将设计任务划分为若干个模块;(3)编写代码:使用VerilogHDL编写各个模块的代码;(4)仿真验证:对设计进行功能仿真和时序仿真,确保设计正确;(5)综合与布局布线:将VerilogHDL代码转换为实际电路,并进行布局布线;(6)硬件测试:在FPGA或ASIC上进行实际硬件测试。

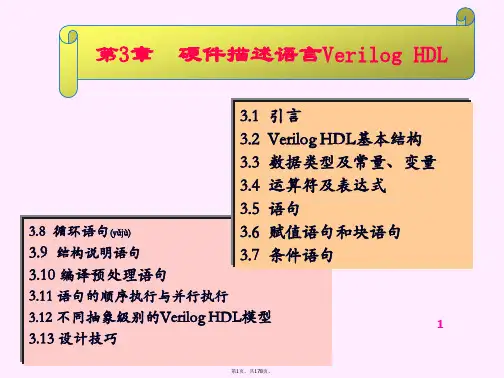

第三章 Verilog HDL的基本语法前言Verilog HDL是一种用于数字逻辑电路设计的语言。

用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型。

Verilog HDL既是一种行为描述的语言也是一种结构描述的语言。

这也就是说,既可以用电路的功能描述也可以用元器件和它们之间的连接来建立所设计电路的Verilog HDL模型。

Verilog模型可以是实际电路的不同级别的抽象。

这些抽象的级别和它们对应的模型类型共有以下五种:•系统级(system):用高级语言结构实现设计模块的外部性能的模型。

•算法级(algorithm):用高级语言结构实现设计算法的模型。

•RTL级(Register Transfer Level):描述数据在寄存器之间流动和如何处理这些数据的模型。

•门级(gate-level):描述逻辑门以及逻辑门之间的连接的模型。

•开关级(switch-level):描述器件中三极管和储存节点以及它们之间连接的模型。

一个复杂电路系统的完整Verilog HDL模型是由若干个Verilog HDL模块构成的,每一个模块又可以由若干个子模块构成。

其中有些模块需要综合成具体电路,而有些模块只是与用户所设计的模块交互的现存电路或激励信号源。

利用Verilog HDL语言结构所提供的这种功能就可以构造一个模块间的清晰层次结构来描述极其复杂的大型设计,并对所作设计的逻辑电路进行严格的验证。

Verilog HDL行为描述语言作为一种结构化和过程性的语言,其语法结构非常适合于算法级和RTL 级的模型设计。

这种行为描述语言具有以下功能:•可描述顺序执行或并行执行的程序结构。

•用延迟表达式或事件表达式来明确地控制过程的启动时间。

•通过命名的事件来触发其它过程里的激活行为或停止行为。

•提供了条件、if-else、case、循环程序结构。

•提供了可带参数且非零延续时间的任务(task)程序结构。