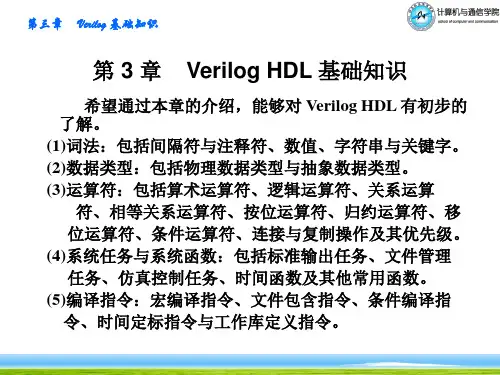

第3章 Verilog设计入门

- 格式:ppt

- 大小:2.45 MB

- 文档页数:84

目录•Verilog概述•Verilog基础语法•组合逻辑电路设计•时序逻辑电路设计•数字系统设计方法学•华为Verilog编程规范与技巧Verilog概述1 2 3Verilog语言诞生,最初用于模拟电子系统的行为。

1980年代初期Verilog逐渐发展成为硬件描述语言(HDL),用于描述数字电路和系统的结构和行为。

1980年代中期Verilog不断完善和发展,成为电子设计自动化(EDA)领域的重要标准之一,广泛应用于集成电路设计、FPGA开发等领域。

1990年代至今Verilog历史与发展集成电路设计Verilog可用于描述数字集成电路的逻辑功能、时序关系和电路结构,是IC设计领域的重要工具。

FPGA开发Verilog可用于FPGA的逻辑设计和编程,实现复杂的数字系统和算法。

ASIC设计Verilog可用于ASIC设计的各个阶段,包括逻辑设计、综合、布局布线等。

系统级建模与仿真Verilog可用于构建系统级模型,进行系统仿真和性能分析。

Verilog应用领域01Verilog 是一种硬件描述语言(HDL ),用于描述数字电路和系统的结构和行为。

02与其他硬件描述语言(如VHDL )相比,Verilog具有更接近C 语言的语法风格,易于学习和使用。

Verilog 支持多种抽象层次的描述,包括行为级、寄存器传输级(RTL )、门级和开关级,方便设计师在不同设计阶段使用。

Verilog 与硬件描述语言关系02Verilog基础语法标识符与关键字标识符用于标识变量、模块、函数等程序实体的名称,由字母、数字和下划线组成,首字符必须是字母或下划线。

关键字Verilog语言中的保留字,用于定义语言结构和控制语句,如`module`、`input`、`output`、`if`、`else`等。

数据类型与运算符数据类型包括整型(`integer`)、实型(`real`)、时间型(`time`)以及用户自定义类型等。

VerilogHDL培训教程——华为第一章:引言随着电子设计自动化(EDA)技术的不断发展,硬件描述语言(HDL)在数字电路设计领域扮演着越来越重要的角色。

VerilogHDL 作为一种主流的硬件描述语言,因其强大的功能、灵活的语法和广泛的应用范围,已成为数字集成电路设计工程师必备的技能之一。

本教程旨在帮助读者掌握VerilogHDL的基本概念、语法和设计方法,为华为等企业培养合格的数字电路设计人才。

第二章:VerilogHDL基础2.1VerilogHDL简介VerilogHDL是一种用于数字电路设计的硬件描述语言,它可以在多个层次上对数字系统进行描述,包括算法级、寄存器传输级(RTL)、门级和开关级。

VerilogHDL的设计初衷是为了提高数字电路设计的可重用性、可移植性和可维护性。

2.2VerilogHDL编程环境(1)文本编辑器:Notepad++、SublimeText等;(2)仿真工具:ModelSim、IcarusVerilog等;(3)综合工具:XilinxISE、AlteraQuartus等。

2.3VerilogHDL语法基础(1)关键字:VerilogHDL中的关键字具有特定含义,如module、endmodule、input、output等;(2)数据类型:包括线网类型(wire)、寄存器类型(reg)、整数类型(integer)等;(3)运算符:包括算术运算符、关系运算符、逻辑运算符等;(4)模块与端口:模块是VerilogHDL设计的基本单元,端口用于模块之间的信号传递;(5)行为描述与结构描述:行为描述用于描述电路的功能,结构描述用于描述电路的结构。

第三章:VerilogHDL设计流程3.1设计流程概述(1)需求分析:明确设计任务和功能要求;(2)模块划分:根据需求分析,将设计任务划分为若干个模块;(3)编写代码:使用VerilogHDL编写各个模块的代码;(4)仿真验证:对设计进行功能仿真和时序仿真,确保设计正确;(5)综合与布局布线:将VerilogHDL代码转换为实际电路,并进行布局布线;(6)硬件测试:在FPGA或ASIC上进行实际硬件测试。

Verilog HDL程序设计教程红色:做后有错。

粉红色:有疑问。

紫色:第二次仍有错。

绿色:文字错误第1章EDA技术综述 1.1引言1.摩尔定律1.2EDA的发展阶段1.阶段1.3设计方法与设计技术1.两种设计思路2.IP的含义3. IP核的分类。

4. SOC的含义1.4EDA的实现1.实现方法第2章EDA设计软件与设计流程 2.2EDA的设计流程1(FPGA的设计流程 2(综合的定义与类型。

3(仿真的类型第3章Verilog HDL设计初步(P18) 3.2完整的Verilog HDL设计1. 4位全加器的和4位计数器的程序。

2. 4位全加器的仿真程序(1.时间头文件 2.模块名(没有参数)3.参数规定(端口、延时、时钟)4.调用测试对象 5.设置参数(所有的输入端口都应初始化赋值)6.显示设置)。

3.3Verilog模块基本结构剖析 1.端口定义注意事项。

2.逻辑功能定义的几种方式第4章Verilog HDL语言要素(P32)4.1词法1.verilog中的四种基本逻辑状态4.2数据类型1.连线型(Net Type)的特点2.寄存器型(Register Type):定义、与连线型区别(赋值、保值)3.Parameter的使用格式4.3寄存器和存储器1.寄存器定义格式和标矢性2.存储器:定义、格式、位区选择方法4.3运算符1.等式与全等式的区别2.位拼接运算符第5章Verilog HDL行为语句(P45)5.2 Verilog HDL中的过程语句1.always过程语句格式。

2.initial过程语句格式。

5.3 块语句1.块语句。

2.用begin—end产生周期为10的个单位时间的方波.3.用fork—join产生周期为10的个单位时间的方波5.4赋值语句1.分类。

2.阻塞赋值和非阻塞赋值的区别5.5条件语句1.例5.11(模为60的BCD码加法计数器)2.case语句的三种表达形式5.6循环语句1.Verilog HDL中4种类型循环语句。