第三章 Verilog HDL语言要素

- 格式:ppt

- 大小:310.00 KB

- 文档页数:1

数字设计中的Verilog HDL语言基础Verilog HDL语言是数字设计中非常重要的一门编程语言,它被广泛应用于集成电路设计和硬件描述语言。

在数字设计中,Verilog HDL语言被用来描述硬件的行为和结构,使得工程师能够通过编写代码来设计和实现各种数字电路。

Verilog HDL语言具有如下几个基础要素:1. 模块(Module):Verilog HDL语言中的最基本构建单元就是模块,一个模块可以包含端口、输入、输出、内部信号和行为描述等部分。

模块用来描述数字电路中的一个功能模块或组件,它是实现数字电路的基础。

2. 信号(Signal):信号是Verilog HDL语言中用来传递信息的基本元素,它可以是输入信号、输出信号或者中间信号。

信号可以是数字类型、整数类型、浮点数类型等,通过信号的传输和逻辑操作来描述整个数字电路的行为。

3. 端口(Port):端口是模块与外部环境进行通信的接口,它可以是输入端口、输出端口或者双向端口。

端口定义了模块和其他模块或顶层模块之间的信号传输规则,是数字电路的输入输出通道。

4. 运算符(Operator):Verilog HDL语言中包含了各种运算符,用来对信号进行逻辑运算、算术运算和比较运算等操作。

常见的运算符包括与(&)、或(|)、非(!)、加(+)、减(-)、乘(*)、除(/)、取余(%)等,通过运算符的使用能够实现数字电路中的各种功能。

5. 时钟(Clock):时钟信号在数字设计中起到非常重要的作用,它用来同步数字电路中的各个组件,确保它们按照时序进行正确的操作。

时钟信号通常是周期性的信号,在数字电路中广泛用于触发、同步和控制各个模块的工作。

通过学习Verilog HDL语言的基础知识,可以帮助我们更好地理解数字设计中的原理和技术,进而能够设计和实现各种复杂的数字电路。

掌握Verilog HDL语言的基础概念和语法规则,是每一位数字设计工程师必备的技能之一。

VerilogHDL入门教程第一部分:Verilog HDL概述(约200字)Verilog HDL是一种硬件描述语言,用于描述和建模数字电路和系统。

它是一种被广泛使用的硬件设计语言,特别适合用于逻辑设计和验证。

Verilog HDL提供了一种形式化的方式来表示数字电路和系统的行为和结构,使得工程师可以更轻松地进行硬件设计和验证。

第二部分:Verilog HDL基础(约400字)在Verilog HDL中,最基本的组成单元是模块。

模块是Verilog HDL中的一个独立的、可重用的单元,可以由其他模块实例化和连接。

每个模块由端口(输入和输出)和内部功能(如逻辑代码和信号声明)组成。

module and_gate(input a, input b, output y);assign y = a & b;endmodule这个模块表示一个与门,它有两个输入a和b,一个输出y。

使用assign语句,我们将输出y连接到输入a和b的逻辑与操作。

第三部分:Verilog HDL高级特性(约400字)除了基本的模块和连接之外,Verilog HDL还提供了一些高级特性,用于更复杂的电路建模和验证。

一种特殊的构造是always块。

always块用于描述模块内的行为,基于一个条件或时钟信号的变化。

例如,下面是一个使用always块的模块示例:module counter(input clk, input enable, output reg count);if (enable)count = count + 1;endendmodule这个模块表示一个简单的计数器,在时钟上升沿时根据enable信号增加计数器的值。

Verilog HDL还支持层次化的建模,允许将模块层次化地组织起来,以便更好地管理和复用代码。

层次化建模通过使用模块的层次命名和连接来实现。

例如,我们可以将上面的计数器模块实例化为另一个模块,如下所示:module top_module(input clk, input enable, output reg count);countercounter_inst(.clk(clk), .enable(enable), .count(count));endmodule这个模块实例化了上面定义的计数器模块,并将其内部信号和端口连接到外部接口。

第1章简介1.Verilog HDL是在哪一年首次被IEEE标准化的?Verilog HDL是在1995年首次被IEEE标准化的。

2.Verilog HDL支持哪三种基本描述方式Verilog HDL可采用三种不同方式或混合方式对设计建模。

这些方式包括:行为描述方式—使用过程化结构建模;数据流方式—使用连续赋值语句方式建模;结构化方式—使用门和模块实例语句描述建模3.可以使用Verilog HDL描述一个设计的时序吗?Verilog HDL可以清晰的建立时序模型,故可以使用Verilog HDL描述一个设计的时序。

4.语言中的什么特性能够用于描述参数化设计?在行为级描述中, Verilog HDL不仅能够在RT L级上进行设计描述,而且能够在体系结构级描述及其算法级行为上进行设计描述,而且能够使用门和模块实例化语句在结构级进行结构描述,这种特性可用于描述参数化设计。

5.能够使用Verilog HDL编写测试验证程序吗?能,可以编写testbench来对编写的程序进行验证。

6.Verilog HDL是由哪个公司最先开发的?Verilog HDL是由Gateway Design Automation公司最先开发的7.Verilog HDL中的两类主要数据类型是什么?线网数据类型和寄存器数据类型。

线网类型表示构件间的物理连线,而寄存器类型表示抽象的数据存储元件。

8.UDP代表什么?UDP代表用户定义原语9.写出两个开关级基本门的名称。

pmos nmos10.写出两个基本逻辑门的名称。

and or第2章 HDL指南1. 在数据流描述方式中使用什么语句描述一个设计?设计的数据流行为使用连续赋值语句进行描述2. 使用` t i m e s c a l e 编译器指令的目的是什么?举出一个实例。

使用编译指令将时间单位与物理时间相关联。

例如` timescale 1ns /100ps 此语句说明时延时间单位为1ns并且时间精度为100ps (时间精度是指所有的时延必须被限定在0.1ns内)3. 在过程赋值语句中可以定义哪两种时延?请举例详细说明。

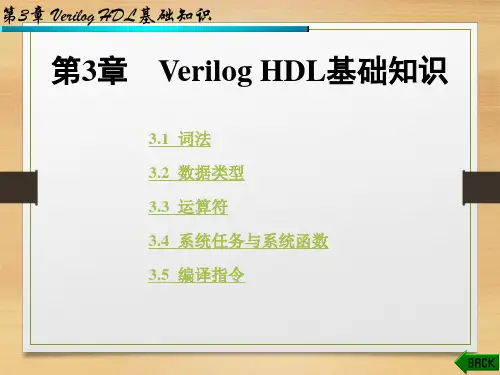

第三章 Verilog HDL的基本语法前言Verilog HDL是一种用于数字逻辑电路设计的语言。

用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型。

Verilog HDL既是一种行为描述的语言也是一种结构描述的语言。

这也就是说,既可以用电路的功能描述也可以用元器件和它们之间的连接来建立所设计电路的Verilog HDL模型。

Verilog模型可以是实际电路的不同级别的抽象。

这些抽象的级别和它们对应的模型类型共有以下五种:•系统级(system):用高级语言结构实现设计模块的外部性能的模型。

•算法级(algorithm):用高级语言结构实现设计算法的模型。

•RTL级(Register Transfer Level):描述数据在寄存器之间流动和如何处理这些数据的模型。

•门级(gate-level):描述逻辑门以及逻辑门之间的连接的模型。

•开关级(switch-level):描述器件中三极管和储存节点以及它们之间连接的模型。

一个复杂电路系统的完整Verilog HDL模型是由若干个Verilog HDL模块构成的,每一个模块又可以由若干个子模块构成。

其中有些模块需要综合成具体电路,而有些模块只是与用户所设计的模块交互的现存电路或激励信号源。

利用Verilog HDL语言结构所提供的这种功能就可以构造一个模块间的清晰层次结构来描述极其复杂的大型设计,并对所作设计的逻辑电路进行严格的验证。

Verilog HDL行为描述语言作为一种结构化和过程性的语言,其语法结构非常适合于算法级和RTL 级的模型设计。

这种行为描述语言具有以下功能:•可描述顺序执行或并行执行的程序结构。

•用延迟表达式或事件表达式来明确地控制过程的启动时间。

•通过命名的事件来触发其它过程里的激活行为或停止行为。

•提供了条件、if-else、case、循环程序结构。

•提供了可带参数且非零延续时间的任务(task)程序结构。

Verilog语言要素Verilog是用于描述和设计数字电路的硬件描述语言(HDL)。

它是一种通用的硬件描述语言,广泛应用于数字电路设计、验证、仿真和综合等领域。

Verilog包含了一系列的语法和语义规则,用于描述硬件行为和结构。

下面是Verilog语言最重要的要素。

1. 模块(Module):Verilog语言使用模块来组织和描述硬件组件。

一个模块代表了一个硬件组件或一个功能单元。

模块包含输入端口、输出端口以及内部逻辑。

模块由关键字"module"开始,用关键字"endmodule"结束。

2. 端口(Port):模块的输入和输出被定义为端口。

端口包括输入端口和输出端口。

输入端口用于将信号从外部引入模块,输出端口用于将信号从模块输出给外部。

端口可以被声明为信号向量,表示多个相关信号。

3. 信号(Signal):信号用于在模块内部表示数据或状态。

信号可以是标量(单个位)或向量(多个位),可以是有符号的或无符号的。

信号可以表示任意类型的数据,比如数字、布尔值或枚举类型等。

4. 寄存器(Register):寄存器是一种存储元件,用于存储和保持数据。

寄存器可以在时钟的上升沿或下降沿进行数据更新。

在Verilog中,可以使用关键字"reg"来声明寄存器类型。

6. 逻辑运算符(Logical Operators):Verilog提供了一系列逻辑运算符,用于对信号进行逻辑运算和位操作。

常见的逻辑运算符包括与(&&)、或(,)、非(!)和异或(^)等。

7. 控制结构(Control Structures):Verilog支持常见的控制结构,如if-else、for循环和while循环等。

这些控制结构允许根据特定条件执行不同的操作或循环执行一系列操作。

8. 合成指令(Synthesis Directives):Verilog提供了一些特殊的指令,用于指导合成工具对Verilog代码进行优化和综合。