Verilog入门训练3—二选一数据选择器

- 格式:pdf

- 大小:797.33 KB

- 文档页数:8

二选一数据选择器目录一:数据选择器的基本原理 (3)二电路逻辑功能 (2)2.1 电路逻辑图 (2)2.2真值表与表达式 (3)2.3电路设计及仿真 (3)三版图设计 (5)3.1总体版图设计及DRC验证 (5)3.1.1数据选择器版图设计步骤 (5)3.1.2版图验证 (8)3.2版图仿真 (9)四数据选择器版图LVS对比 (10)五结论及体会 (12)一:数据选择器的基本原理数据选择器是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去,实现数据选择功能的逻辑电路称为数据选择器。

它的作用相当于多个输入的单刀多掷开关,其示意图如下:图1 n位通道选择信号数据选择器除了可以实现一些组合逻辑功能以外,还可以做分时多路传输电路、函数发生器及数码比较器等。

常见的数据选择器有4选1、8选1、16选1电路。

在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号下图所示为二选一数据选择器原理图,a,b为输入端,sel为控制端,out为输出端图1-1数据选择器原理图二电路逻辑功能2.1 电路逻辑图=+(S是数据选择控制端,S为0时选择A,为1时选S择B)Y SA SB要实现2选1选择器,逻辑电路图如下所示图2-1数据选择器逻辑电路图2.2真值表与表达式二选一数据选择器逻辑表达式为:Y SA SB =+根据逻辑表达式所列真值表如下图所示图2-2数据选择器真值表图2.3电路设计及仿真根据原理电路图并使用S-Edit 软件设计出数据选择器的电路图及对应符号图如下:S A B Y 01 1 1 1 0 1 0 1 0 0 0 0 1 1 1 1 1 0 0 0 1 1 0图2-3数据选择器符号图根据符号图并使用S-Edit软件设计出的数据选择器电路图如下所示图2-4数据选择器电路图导出的SPICE文件,如下图所示图2-5 spice文件加载包含文件,如下图所示图2-6 加载后的SPICE文件在其基础上进行仿真:下图从上到下依次为Y. S B A,结合逻辑表达式及真值表可知,电路为正确的图2-7 模拟波形仿真图三版图设计3.1总体版图设计及DRC验证3.1.1数据选择器版图设计步骤(1)新建文件夹:在电脑本地磁盘新建文件夹,文件夹名为shuju。

实验三 4位2选1多路选择器的设计与实现一.实验目的1.使用ISE软件设计并仿真;2.学会程序下载。

二.实验内容使用ISE软件进行4位2选1多路选择器的设计与实现。

三.实验步骤1. 编写文本文件并编译2. 软件仿真3. 进行硬件配置四.实验原理1. ISE软件是一个支持数字系统设计的开发平台。

2. 用ISE软件进行设计开发时基于相应器件型号的。

注意:软件设计时选择的器件型号是与实际下载板上的器件型号相同。

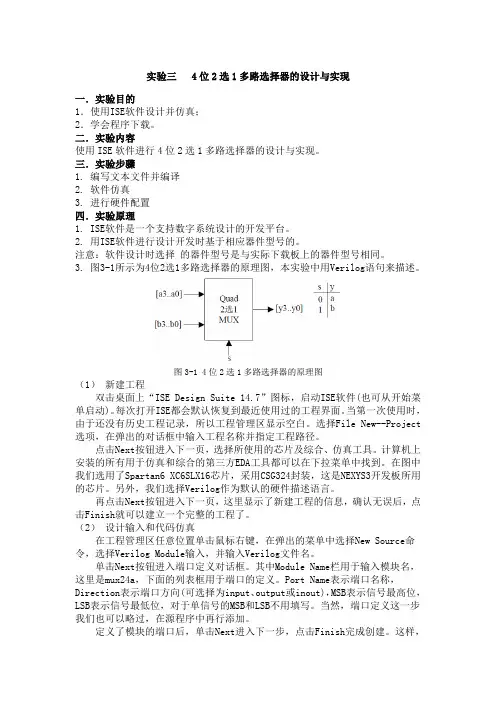

3. 图3-1所示为4位2选1多路选择器的原理图,本实验中用Verilog语句来描述。

图3-1 4位2选1多路选择器的原理图(1)新建工程双击桌面上“ISE Design Suite 14.7”图标,启动ISE软件(也可从开始菜单启动)。

每次打开ISE都会默认恢复到最近使用过的工程界面。

当第一次使用时,由于还没有历史工程记录,所以工程管理区显示空白。

选择File New--Project 选项,在弹出的对话框中输入工程名称并指定工程路径。

点击Next按钮进入下一页,选择所使用的芯片及综合、仿真工具。

计算机上安装的所有用于仿真和综合的第三方EDA工具都可以在下拉菜单中找到。

在图中我们选用了Spartan6 XC6SLX16芯片,采用CSG324封装,这是NEXYS3开发板所用的芯片。

另外,我们选择Verilog作为默认的硬件描述语言。

再点击Next按钮进入下一页,这里显示了新建工程的信息,确认无误后,点击Finish就可以建立一个完整的工程了。

(2)设计输入和代码仿真在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择New Source命令,选择Verilog Module输入,并输入Verilog文件名。

单击Next按钮进入端口定义对话框。

其中Module Name栏用于输入模块名,这里是mux24a,下面的列表框用于端口的定义。

Port Name表示端口名称,Direction表示端口方向(可选择为input、output或inout),MSB表示信号最高位,LSB表示信号最低位,对于单信号的MSB和LSB不用填写。

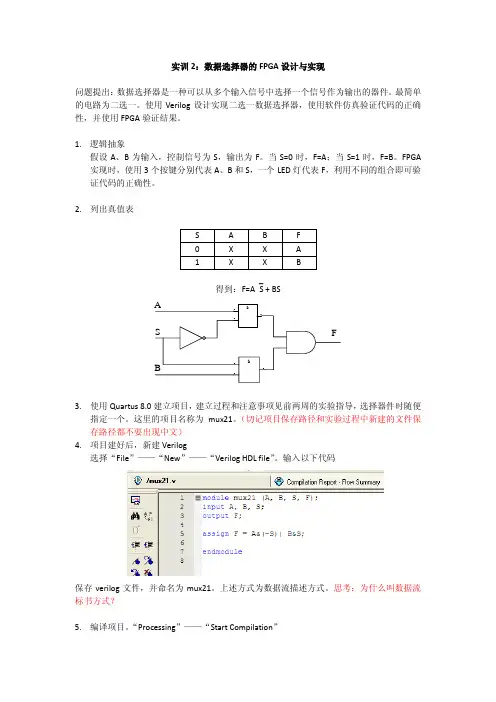

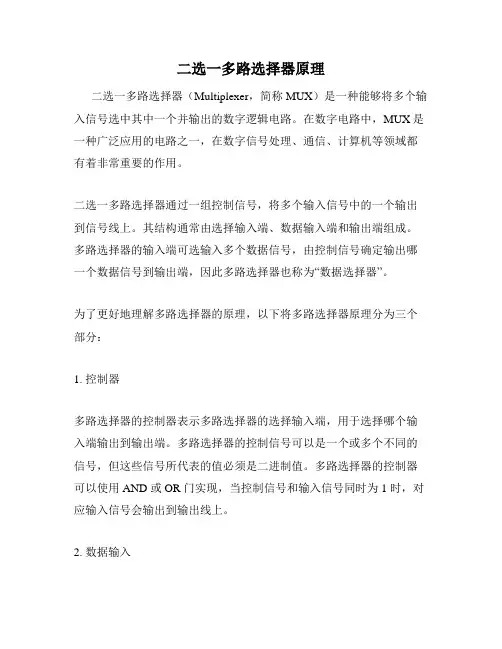

二选一多路选择器原理二选一多路选择器(Multiplexer,简称MUX)是一种能够将多个输入信号选中其中一个并输出的数字逻辑电路。

在数字电路中,MUX是一种广泛应用的电路之一,在数字信号处理、通信、计算机等领域都有着非常重要的作用。

二选一多路选择器通过一组控制信号,将多个输入信号中的一个输出到信号线上。

其结构通常由选择输入端、数据输入端和输出端组成。

多路选择器的输入端可选输入多个数据信号,由控制信号确定输出哪一个数据信号到输出端,因此多路选择器也称为“数据选择器”。

为了更好地理解多路选择器的原理,以下将多路选择器原理分为三个部分:1. 控制器多路选择器的控制器表示多路选择器的选择输入端,用于选择哪个输入端输出到输出端。

多路选择器的控制信号可以是一个或多个不同的信号,但这些信号所代表的值必须是二进制值。

多路选择器的控制器可以使用 AND 或 OR 门实现,当控制信号和输入信号同时为 1 时,对应输入信号会输出到输出线上。

2. 数据输入多路选择器的数据输入就是该选择器的多个输入端。

可以选择其中的一个输入端作为输出,这个输出端的值等于该输入端的值。

这些输入信号可以是数字信号、模拟信号或混合信号。

3. 输出多路选择器的输出端是计算机或其他设备使用的信号线。

多路选择器的输出值取决于选择输入端和输入端的状态。

当控制器的状态为0 时,多路选择器输出与第一个输入信号连接的值。

当控制器为 1 时,多路选择器输出与第二个输入信号相连的值。

这个选择过程由控制器完成。

综上所述,二选一多路选择器是一种能够将多个输入信号中的一个输出的数字逻辑电路。

其结构由选择输入端、数据输入端和输出端组成。

多路选择器通过一组控制信号,确定输出哪一个数据信号到输出端。

在数字信号处理、通信、计算机等领域中,多路选择器都有着广泛的应用,是非常重要的电路之一。

列表:1. 二选一多路选择器是什么?2. 多路选择器的控制器是如何实现的?3. 多路选择器的数据输入是什么?4. 多路选择器的输出是什么?5. 多路选择器在哪些领域有广泛的应用?。

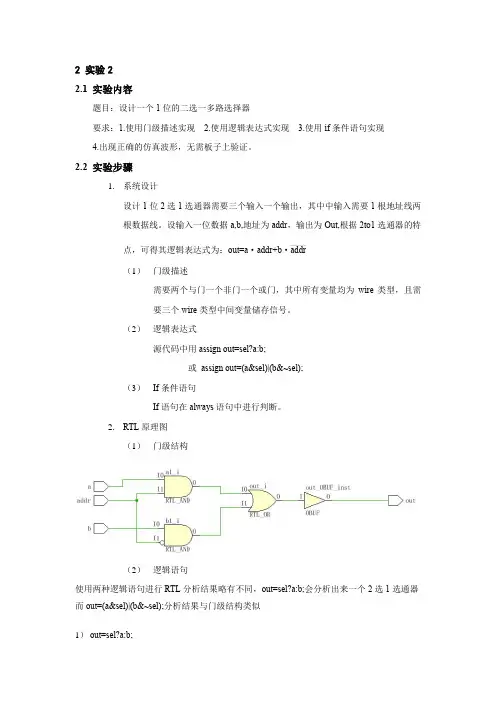

2 实验22.1 实验内容题目:设计一个1位的二选一多路选择器要求:1.使用门级描述实现 2.使用逻辑表达式实现 3.使用if条件语句实现4.出现正确的仿真波形,无需板子上验证。

2.2 实验步骤1.系统设计设计1位2选1选通器需要三个输入一个输出,其中中输入需要1根地址线两根数据线。

设输入一位数据a,b,地址为addr,输出为Out,根据2to1选通器的特_______点,可得其逻辑表达式为:out=a·addr+b·addr(1)门级描述需要两个与门一个非门一个或门,其中所有变量均为wire类型,且需要三个wire类型中间变量储存信号。

(2)逻辑表达式源代码中用assign out=sel?a:b;或assign out=(a&sel)|(b&~sel);(3)If条件语句If语句在always语句中进行判断。

2.RTL原理图(1)门级结构(2)逻辑语句使用两种逻辑语句进行RTL分析结果略有不同,out=sel?a:b;会分析出来一个2选1选通器而out=(a&sel)|(b&~sel);分析结果与门级结构类似1)out=sel?a:b;2)out=(a&sel)|(b&~sel);(3)if语句3.重要源代码及注释(1)门级结构module mux2_1(a,b,out,addr);input a,b,addr;output out;wire naddr,a1,b1;//定义中间变量not (naddr,addr);and (b1,b,naddr);and (a1,a,addr);or (out,a1,b1);endmodule(2)逻辑语句module luoji(input a,input b,input sel,output out);assign out=(a&sel)|(b&~sel);endmodule(3)if语句module mux2_1if(a,b,sel,out);input a,b,sel;output out;reg out;always@(a or b or sel)beginif(sel) out=a;else out=b;end2.3 结果分析1.Testbench代码(3种方式testbench 中代码类似,此处以if语句为例)module mux2_1if_tb();reg a,b,sel;mux2_1if m1(a,b,sel,out);initialbegina=0;b=0;sel=0;endalwaysbegin#10 a<=~a;endalwaysbegin#20 b<=~b;endalwaysbegin#15 sel<=1;#8 sel<=0;endendmodule2.仿真波形图(1)门级结构(2)逻辑语句(3)If语句3.说明三种方式均定义当选择端值为1时输出a,选择端值为0输出b;其中逻辑语句与if语句testbench部分代码相同,门级结构咯有不同,三种波形仿真图像均正确,符合2选1选通器功能。

2选1数据选择器的VHDL描述ENTITY mux21a ISPORT( a, b : IN BIT ;s : IN BIT;y : OUT BIT ) ;END ENTITY mux21a ;ARCHITECTURE one OF mux21a ISBEGINy <= a WHEN s = '0'ELSE b ;END ARCHITECTURE one ;译码器的设计architecture dec_behave of e1 issignal sel : std_logic_vector( 0 to 3) ;beginsel(0) <= en ; sel(1) <= a(0) ; sel(2) <= a(1) ; sel(3) <= a(2) ;with sel selecty <= "00000001" when "1000","00000010" when "1001","00000100" when "1010","00001000" when "1011","00010000" when "1100","00100000" when "1101","01000000" when "1110","10000000" when "1111","00000000" when others ;end dec_behave ;8-3优先编码器library IEEE; ……;entity encoder83 isport (ind: in std_logic_vector(7 downto 0);outd: out std_logic_vector(2 downto 0));end ;architecture behave of encoder83 isbeginprocess (ind)beginif ind (7) = ‘1' then outd<= "111";elsif ind (6) = ‘1' then outd<= "110";elsif ind (5) = ‘1' then outd<= "101"; elsif ind (4) = ‘1' then outd<= "100"; elsif ind (3 )= ‘1' then outd<= "011"; elsif ind (2) = ‘1' then outd<= "010"; elsif ind (1) = ‘1' then outd<= "001"; elsif ind (0) = ‘1' then outd<= "000"; else outd<= "000";end if;end process; end behave;。

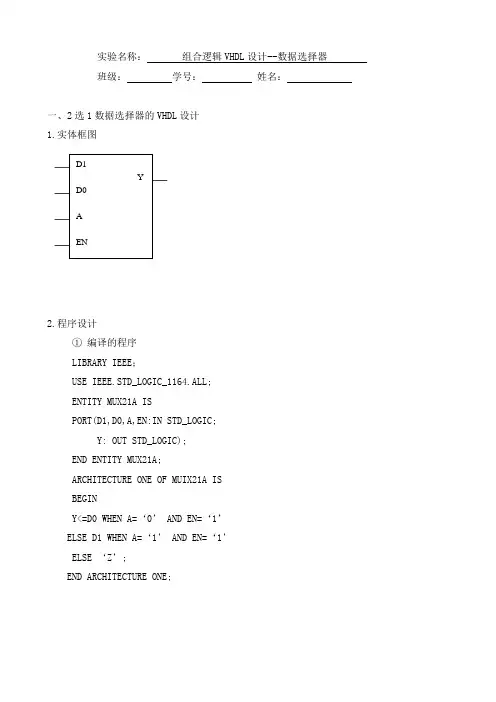

实验名称:组合逻辑VHDL设计--数据选择器班级:学号:姓名:一、2选1数据选择器的VHDL设计1.实体框图2.程序设计①编译的程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX21A ISPORT(D1,D0,A,EN:IN STD_LOGIC;Y: OUT STD_LOGIC);END ENTITY MUX21A;ARCHITECTURE ONE OF MUIX21A ISBEGINY<=D0 WHEN A=‘0’ AND EN=‘1’ELSE D1 WHEN A=‘1’ AND EN=‘1’ELSE ‘Z’;END ARCHITECTURE ONE;3.仿真波形图4.仿真波形分析(1)EN为高电平使能端口即当高电平时有效,低电平时无效,当高电平有效时A如果为高电平则Y输出D1的波形,反之A为低电平时输出D0的波形。

(2)为区分波形图,A,D1,D0的周期应该设置不一样的周期,明显一点可以是倍数关系二、4选1数据选择器的VHDL设计1.实体框图2.程序设计①编译的程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX41A ISPORT(A1,A0,D0,D1,D2,D3:IN STD_LOGIC;Y:OUT STD_LOGIC);END ENTITY MUX41A;ARCHITECTURE ONE OF MUX41A ISBEGINY<=D0 WHEN A1=‘0’ AND A0=‘0’ELSE D1 WHEN A1=‘0’ AND A0=‘1’ELSE D2 WHEN A1=‘1’ AND A0=‘0’ELSE D3 WHEN A1=‘1’ AND A0=‘1’ELSE ‘Z’;END ARCHITECTURE ONE;3.仿真波形图4.仿真波形分析(1)当a1=‘0’,a0=‘0’时输出d0的波形当a1=‘0’,a0=‘1’时输出d1的波形当a1=‘1’,a0=‘0’时输出d2的波形当a1=‘1’,a0=‘1’时输出d3的波形(2)为便于分析图形,可以设置不一样的周期,倍数关系,看的清晰一点。

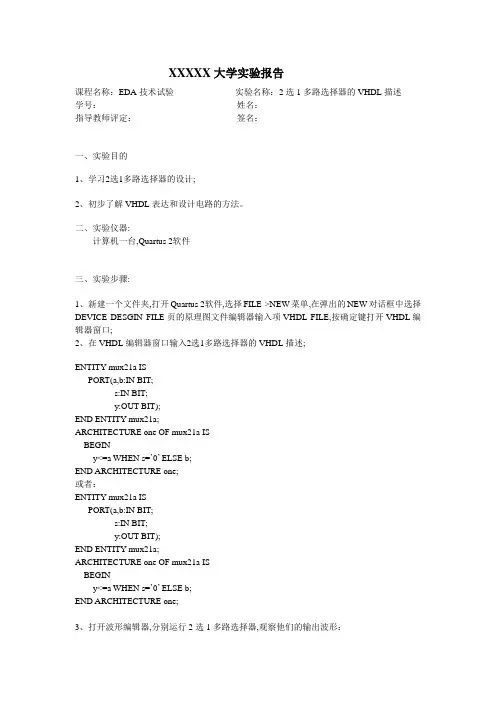

XXXXX大学实验报告课程名称:EDA技术试验实验名称:2选1多路选择器的VHDL描述学号:姓名:指导教师评定:______________________ 签名:_____________________________一、实验目的1、学习2选1多路选择器的设计;2、初步了解VHDL表达和设计电路的方法。

二、实验仪器:计算机一台,Quartus 2软件三、实验步骤:1、新建一个文件夹,打开Quartus 2软件,选择FILE->NEW菜单,在弹出的NEW对话框中选择DEVICE DESGIN FILE页的原理图文件编辑器输入项VHDL FILE,按确定键打开VHDL编辑器窗口;2、在VHDL编辑器窗口输入2选1多路选择器的VHDL描述;ENTITY mux21a ISPORT(a,b:IN BIT;s:IN BIT;y:OUT BIT);END ENTITY mux21a;ARCHITECTURE one OF mux21a ISBEGINy<=a WHEN s=’0’ ELSE b;END ARCHITECTURE one;或者:ENTITY mux21a ISPORT(a,b:IN BIT;s:IN BIT;y:OUT BIT);END ENTITY mux21a;ARCHITECTURE one OF mux21a ISBEGINy<=a WHEN s=’0’ ELSE b;END ARCHITECTURE one;3、打开波形编辑器,分别运行2选1多路选择器,观察他们的输出波形:;4、调出VHDL描述产生的2选1多路选择器的原理图.点击TOOLS->NELIST VIEWERS->RTL VIEWERS,即调出VHDL描述产生的2选1多路选择器的RTL电路图,如下所示:四、实验小结经过本次试验初步了解了Quartus 2软件的使用,及VHDL表达和设计电路的方法。

一、实验目的01.学会使用VHDL语言并熟悉;0用VHDL语言完成2选1多路选择器设计和8位硬件加法器VHDL设计;02.二.实验设备:0名称规格数量0计算机586及以上1台0Quartus II软件 6.0以上0三、实验内容及步骤01.利用VHDL语言完成2选1多路选择器的设计01).打开Quartus II新建打开VHDL界面,输入程序,并保存名为mux21a.vhdl,程序如图3-1:0图3-1VHDL语言描述0在窗口中点击compile,编译成功如图3-2:0图3-202). 编译成功后,新建波形文件。

将上述描述语言进行波形仿真。

编译成功如图3-3,仿真波形如下图3-40图3-30图3-4仿真波形图0由此可得到结构图,如图3-50图3-508位硬件加法器的VHDL设计01.如同2选1多路选择器的设计类似,输入VHDL描述语言,保存到adder8b 工程中。

描述语言如下图3-60图3-602.编译成功后,新建波形文件。

将上述描述语言进行波形仿真。

仿真波形如下图3-7图3-70通过对波形的分析可知,达到设计目的。

0四、实验小结0,1.多路选择器是典型的组合电路,应该熟悉它们。

0,2.通过此次实验,可知主要考察通过VHDL语言编译器件的能力,因此对语言的描述一定要到位。

0,3.通过本次实验对VHDL描述语言的语法又有了更进一步的认识和熟悉,从整体上把握VHDL程序的基本结构和设计特点,为以后编辑大型器件奠定了厚实的基础。

0。

实验一二选一数据选择器VHDL设计Quartus II 6.0开发环境与EDA实验箱使用一实验目的1.熟悉在Quartus II 6.0环境下原理图输入方法。

2.熟悉Quartus II 6.0环境下编辑、编译综合、仿真的操作方法。

3、掌握利用EDA软件进行电路设计的详细流程;4、熟悉EDA实验箱的基本使用方法。

学会对实验板上的FPGA/CPLD进行编程下载,硬件验证自己的设计项目。

二实验仪器PC机、Quartus II 6.0软件三实验内容1.详细解读教材117页。

2.在QuartusⅡ上输入该设计的原理图,并进行编辑、编译、综合、适配、仿真。

3.给出其所有信号的时序仿真波形。

四实验原理及步骤1.启动Quartus II 6.0软件在桌面上双击Quartus II 6.0图标或者在开始—>所有程序—>Altera—> Quartus II 6.0,如下图2.建立工作库文件夹及工程任何一次设计都是一项工程(Project),所有此工程相关的所有设计文件都需要放在同一个文件夹里。

不同的设计放在不同的文件夹中。

在E盘下建立一个存放本次设计的工程文件夹,比如“shiyan1”。

注意不要使用中文文件夹,文件夹的存放路径也不要包含中文。

注意本实验室计算机C盘和D盘是重启后复原,不要将任何文件和文件夹放置在桌面或者C、D盘下。

初次打开Quartus II 6.0,会有如图提示:选择是的情况下,首先是新工程向导:介绍下一步下一步下一步,选择目标芯片,首先在Family栏选择ACEX1K系列,然后选择此系列的具体芯片:EP1K30TC144-3。

注意不要选成了EP1K30TC144-3。

下一步就点完成。

3.建立文本程序文件选择File菜单下的New或者直接点击工具栏中的新建图标,选择新建文件类型为VHDL File。

接下来另存文件:保存时需更改文件名与项目名称一样,注意保存在同一个工程文件夹下面。

基础项⽬(2)⼆选⼀数据选择器的设计写在前⾯的话数据选择器在数字电路设计中的应⽤尤为⼴泛。

同时,作为基础的电路功能单元,也⽐较适合作为初学者的⼊门实验。

现在梦翼师兄陪⼤家⼀起来设计⼀个最基础的数据选择器。

项⽬需求设计⼀个⼆选⼀数据选择器,然后⽤⼀路控制信号选择输出数据选通哪⼀路输⼊的数据信号。

系统架构模块功能介绍模块名功能描述mux2通过Data_sel 选择输出结果的值顶层模块端⼝描述端⼝名端⼝说明Data_a A通道数据输⼊Data_b B通道数据输⼊Data_out数据输出端Data_sel数据选通控制代码解释mux2代码解释/***************************************************** Engineer : 梦翼师兄* QQ : 761664056* The module function:⼆选⼀多路器*****************************************************/00 module mux2(01 data_a, //A通道数据输⼊02 data_b, //B通道数据输⼊03 data_sel, //输出数据选通信号04 data_out //数据输出05 );06 //系统输⼊07 input data_a; //A通道数据输⼊08 input data_b; //B通道数据输⼊09 input data_sel; //输出数据选通信号10 //系统输出11 output reg data_out;//数据输出12 //⼆选⼀多路器控制逻辑13 always@(*)14 begin14 begin15 if(data_sel)//选通信号为⾼电平16 data_out=data_a;//输出结果为A通道数据17 else //选通信号为低电平18 data_out=data_b;//输出结果为B通道数据19 end20 endmodule01~05⾏列出了多路器所有输⼊/输出接⼝,07~11⾏定义了端⼝属性,13~19⾏描述了⼆选⼀多路器的逻辑功能。

实验报告课程名称:FPGA设计及应用实验项目:设计二选一多路选择器实验时间:20XX年4月1号实验班级:12电子信息工程X班指导教师:李XX二〇〇四年四月十三日广东技术师范学院实验报告学院:电子与信息学院专业:电子信息工程班级:12电本X班成绩:姓名:学号:20XX0442430 组别:组员:实验地点:工业中心实验日期: 4.01 指导教师签名:实验七项目名称:设计二选一多路选择器一、实验目的和要求设计二选一多路选择器:通过简单完整而典型的VHDL设计,初步了解VHDL表达和设计电路的方法并对由此而引出的语言对象和语言规则加以有针对性的说明。

二、实验步骤预习情况操作情况考勤情况数据处理情况1、创建新的工程,步骤如下:2、创建新的文件3、用VHDL语言根据实验要求的功能编写代码4、编译5、引脚分配6、链接数据线,下载程序三、实验源代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux21a ISPORT(a,b:IN BIT;s:IN BIT;y:OUT BIT);END;ARCHITECTURE one OF mux21a ISBEGINy<=a WHEN s='0' ELSE b;END ARCHITECTURE one;四、实验结果与总结1、通过本节上机实验,加深了解了VHDL语言现象和语句规律。

2、程序很简单,按照示例程序输入没有什么错误。

主要是通过这个简单程序了解了仿真的全过程。

3、实验后基本能从整体上把握VHDL程序的基本结构和设计特点。

掌握固定表达句式。