数字电路实验考试参考题目

- 格式:doc

- 大小:26.00 KB

- 文档页数:1

数电实验考试题及答案一、选择题(每题2分,共20分)1. 在数字电路中,一个触发器的状态由其输入端的信号决定,而不受输出端的影响。

这个触发器是()。

A. RS触发器B. D触发器C. JK触发器D. T触发器答案:B2. 以下哪个不是组合逻辑电路的特点?()A. 输出只依赖于当前输入B. 输出与输入之间存在时间延迟C. 输出与输入之间没有记忆功能D. 输出状态随输入状态的变化而变化答案:B3. 在一个4位二进制计数器中,当计数器从0计数到15时,输出端Q3Q2Q1Q0的状态变化顺序是()。

A. 0000 -> 0001 -> 0010 -> 0011 -> 0100 -> 0101 -> 0110 -> 0111 -> 1000 -> 1001 -> 1010 -> 1011 -> 1100 -> 1101 -> 1110 -> 1111 -> 0000B. 0000 -> 0001 -> 0010 -> 0011 -> 0100 -> 0101 -> 0110 -> 0111 -> 1000 -> 1001 -> 1010 -> 1011 -> 1111 -> 1110 -> 1101 -> 0000C. 0000 -> 0001 -> 0010 -> 0011 -> 0100 -> 0101 -> 0110 ->0111 -> 1000 -> 1001 -> 1010 -> 1011 -> 1110 -> 1101 -> 1111 -> 0000D. 0000 -> 0001 -> 0010 -> 0011 -> 0100 -> 0101 -> 0110 -> 0111 -> 1000 -> 1001 -> 1010 -> 1011 -> 1100 -> 1101 -> 1110 -> 1111答案:A4. 以下哪个逻辑门电路可以实现异或(XOR)功能?()A. 与非门B. 或非门C. 与门D. 异或门答案:D5. 在数字电路中,一个D触发器的输出Q与输入D的关系是()。

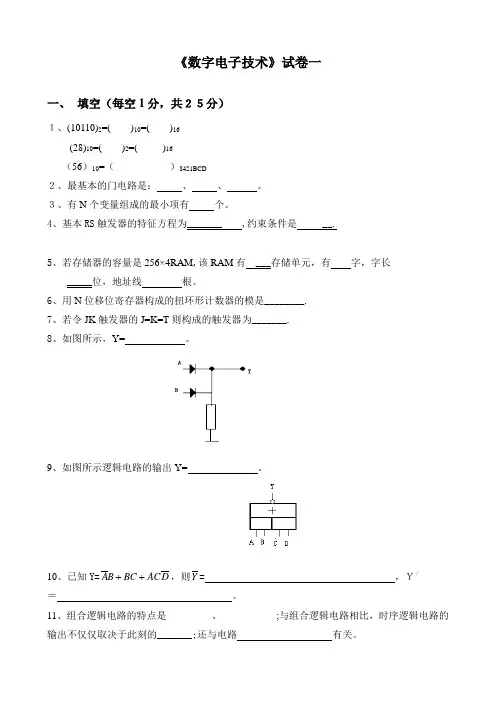

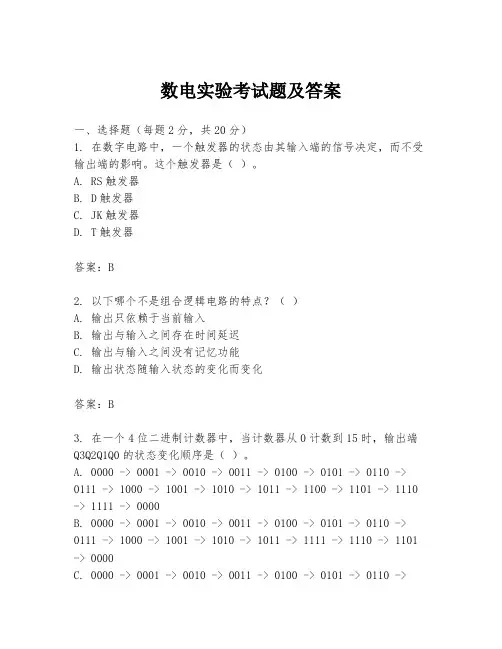

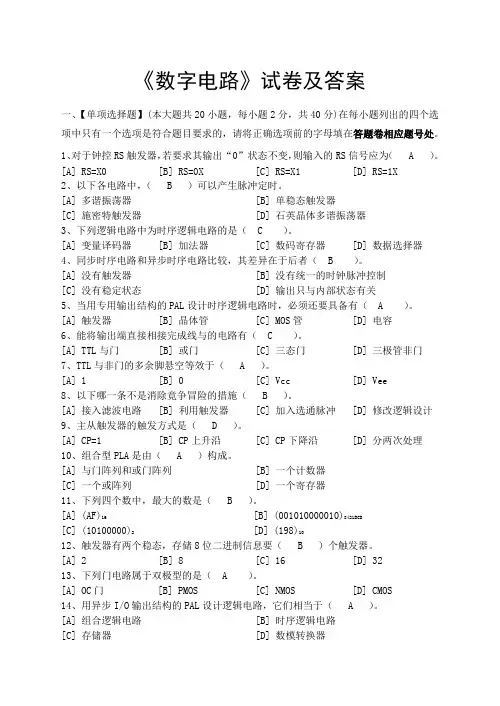

《数字电路》试卷及答案一、【单项选择题】(本大题共20小题,每小题2分,共40分)在每小题列出的四个选项中只有一个选项是符合题目要求的,请将正确选项前的字母填在答题卷相应题号处。

1、对于钟控RS触发器,若要求其输出“0”状态不变,则输入的RS信号应为( A )。

[A] RS=X0 [B] RS=0X [C] RS=X1 [D] RS=1X2、以下各电路中,( B )可以产生脉冲定时。

[A] 多谐振荡器[B] 单稳态触发器[C] 施密特触发器[D] 石英晶体多谐振荡器3、下列逻辑电路中为时序逻辑电路的是( C )。

[A] 变量译码器[B] 加法器[C] 数码寄存器[D] 数据选择器4、同步时序电路和异步时序电路比较,其差异在于后者( B )。

[A] 没有触发器[B] 没有统一的时钟脉冲控制[C] 没有稳定状态[D] 输出只与内部状态有关5、当用专用输出结构的PAL设计时序逻辑电路时,必须还要具备有( A )。

[A] 触发器[B] 晶体管[C] MOS管[D] 电容6、能将输出端直接相接完成线与的电路有( C )。

[A] TTL与门[B] 或门[C] 三态门[D] 三极管非门7、TTL与非门的多余脚悬空等效于( A )。

[A] 1 [B] 0 [C] Vcc [D] Vee8、以下哪一条不是消除竟争冒险的措施( B )。

[A] 接入滤波电路[B] 利用触发器[C] 加入选通脉冲[D] 修改逻辑设计9、主从触发器的触发方式是( D )。

[A] CP=1 [B] CP上升沿[C] CP下降沿[D] 分两次处理10、组合型PLA是由( A )构成。

[A] 与门阵列和或门阵列[B] 一个计数器[C] 一个或阵列[D] 一个寄存器11、下列四个数中,最大的数是( B )。

[A] (AF)16[B] (001010000010)8421BCD[C] (10100000)2[D] (198)1012、触发器有两个稳态,存储8位二进制信息要( B )个触发器。

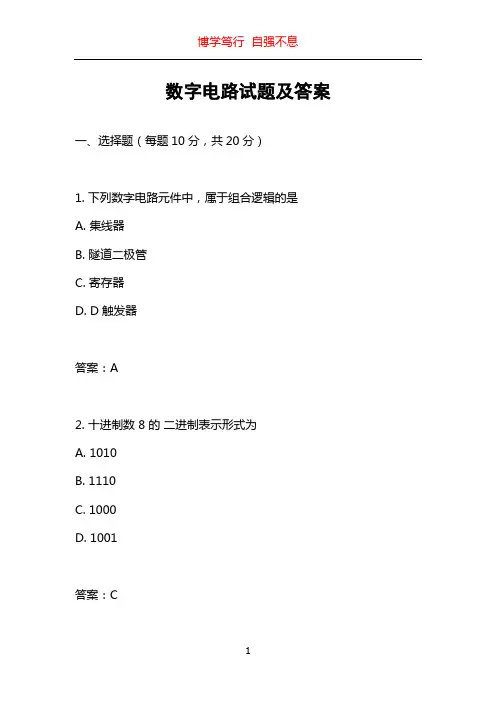

数字电路试题及答案一、选择题(每题10分,共20分)1. 下列数字电路元件中,属于组合逻辑的是A. 集线器B. 隧道二极管C. 寄存器D. D触发器答案:A2. 十进制数 8 的二进制表示形式为A. 1010B. 1110C. 1000D. 1001答案:C3. 十六进制数 B 的二进制表示形式为A. 1010B. 1101C. 1111D. 1011答案:D4. 以下哪个逻辑门的输出是其他逻辑门输出的非A. 与门B. 或门C. 非门D. 异或门答案:C二、填空题(每题10分,共20分)1. 使用 2 输入 AND 门,将 A 和 B 两个开关输入,如果 A 和 B 均为高电平时,输出为________答案:高电平2. 使用 2 输入 OR 门,将 A 和 B 两个开关输入,如果 A 和 B 中有一个或两个为高电平时,输出为________答案:高电平3. 使用 2 输入 XOR 门,将 A 和 B 两个开关输入,如果 A 和 B 中只有一个为高电平时,输出为________答案:高电平4. 使用 2 输入 NAND 门时,输出为低电平的条件是________答案:A 和 B 均为高电平三、简答题(每题20分,共40分)1. 请简述组合逻辑和时序逻辑的区别。

答案:组合逻辑是指电路的输出仅由当前时刻的输入确定,与之前的输入无关。

组合逻辑电路的输出仅取决于输入信号的组合,对于相同的输入,始终保持相同的输出。

而时序逻辑是指电路的输出除了与当前输入有关外,还与之前的输入和输出有关。

时序逻辑电路的输出不仅取决于输入信号的组合,还受到电路之前状态的影响。

2. 请简述二进制和十六进制之间的转换原理。

答案:二进制是一种基于2的数制,只有两个数位 0 和 1。

而十六进制是一种基于16的数制,包含了 0 到 9 的数字和 A 到 F 的六个字母。

进行二进制到十六进制的转换时,将二进制数按照每四位分组,然后将每个四位二进制数转换为相应的十六进制数,最终得到的十六进制数就是对应的表示。

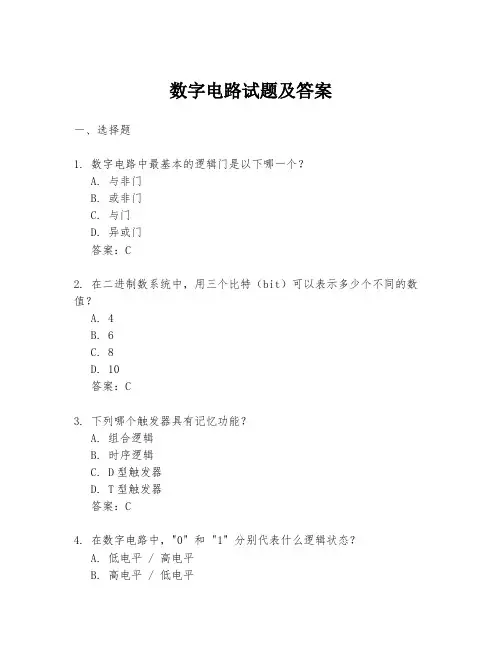

数字电路试题及答案一、选择题1. 数字电路中最基本的逻辑门是以下哪一个?A. 与非门B. 或非门C. 与门D. 异或门答案:C2. 在二进制数系统中,用三个比特(bit)可以表示多少个不同的数值?A. 4B. 6C. 8D. 10答案:C3. 下列哪个触发器具有记忆功能?A. 组合逻辑B. 时序逻辑C. D型触发器D. T型触发器答案:C4. 在数字电路中,"0" 和 "1" 分别代表什么逻辑状态?A. 低电平 / 高电平B. 高电平 / 低电平C. 接地 / 供电D. 禁用 / 启用答案:A5. 以下哪种类型的逻辑门是使用晶体管实现开关功能的?A. 模拟门B. 数字门C. 模拟数字门D. 晶体管逻辑门答案:D二、填空题1. 在数字电路中,一个______门输出的高电平可以驱动多个输入端,而不会改变输出电平。

答案:或门2. _______是数字电路设计中的一种基本方法,它将复杂的电路分解为更简单的子电路。

答案:模块化设计3. 在数字电路中,一个______触发器在时钟信号的上升沿改变状态,而______触发器在下降沿改变状态。

答案:D型;JK型4. 一个4位二进制计数器的最大输出值是______。

答案:155. 在数字电路中,______是一种用于存储数据的电路,它可以在没有时钟信号的情况下保持信息。

答案:触发器三、简答题1. 请简述数字电路与模拟电路的主要区别。

答:数字电路处理的是离散的信号,通常只有两种状态(如高电平代表“1”,低电平代表“0”),而模拟电路处理的是连续变化的信号。

数字电路的主要优点是抗干扰能力强,易于实现逻辑运算和存储功能,而模拟电路则更擅长处理连续变化的信号,如音频和视频信号。

2. 什么是组合逻辑和时序逻辑?答:组合逻辑是指其输出仅依赖于当前输入信号的逻辑电路,不包含存储元件,如与门、或门和非门等。

时序逻辑则包含存储元件(如触发器),其输出不仅依赖于当前的输入信号,还依赖于历史状态,因此具有记忆功能。

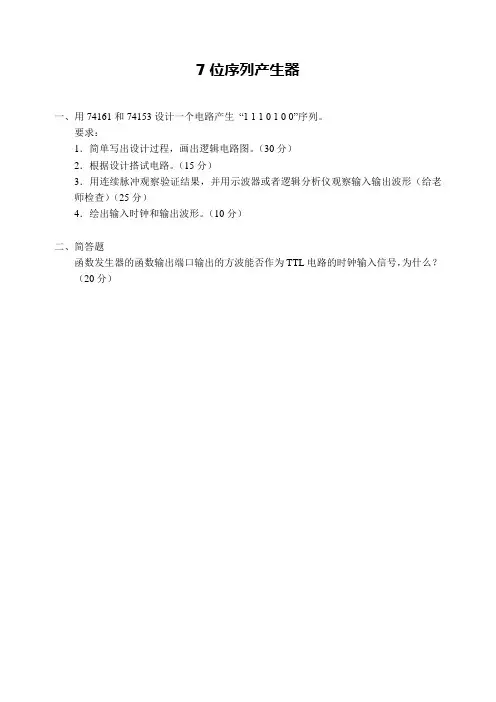

7位序列产生器一、用74161和74153设计一个电路产生“1 1 1 0 1 0 0”序列。

要求:1.简单写出设计过程,画出逻辑电路图。

(30分)2.根据设计搭试电路。

(15分)3.用连续脉冲观察验证结果,并用示波器或者逻辑分析仪观察输入输出波形(给老师检查)(25分)4.绘出输入时钟和输出波形。

(10分)二、简答题函数发生器的函数输出端口输出的方波能否作为TTL电路的时钟输入信号,为什么?(20分)7位序列产生器(答案及评分标准)一、74161和74153设计一个电路产生“1 1 1 0 1 0 0”序列。

要求:1.简单写出设计过程,画出逻辑电路图。

(30分)2.根据设计搭试电路。

(15分)3.用连续脉冲观察验证结果,并用示波器观察输入输出波形(给老师检查)(25分)4.定量绘出输入时钟和输出波形。

(10分)1.先用74ls161设计一个模值为7的计数器(10分),然后完成下图所示的后续电路(74153的应用)(20分);其他设计方案也可。

2.电路接线符合基本规范,电源连接正确(15分);3.信号源使用(输入信号):频率的调整,波形的选择正确(5分)示波器使用:含调零电平,置校准位(模拟示波器),DC耦合,双踪观察(5分)结果正确(15分);或者逻辑分析仪的使用:连接方法正确(包括接地)5分,结果正确15分。

4.波形记录符合规范:相位对齐(5分),画满一个周期4分,方波边沿画出1分。

二、函数发生器的函数输出端口输出的方波能否作为TTL电路的输入信号,为什么?答:能(6分),但有条件(3分)当调整函数发生器的V oltage Out端口输出方波,使其高低电平值满足TTL电路输入信号0V和3V(5V)要求时,即可以代替TTL信号(11分)。

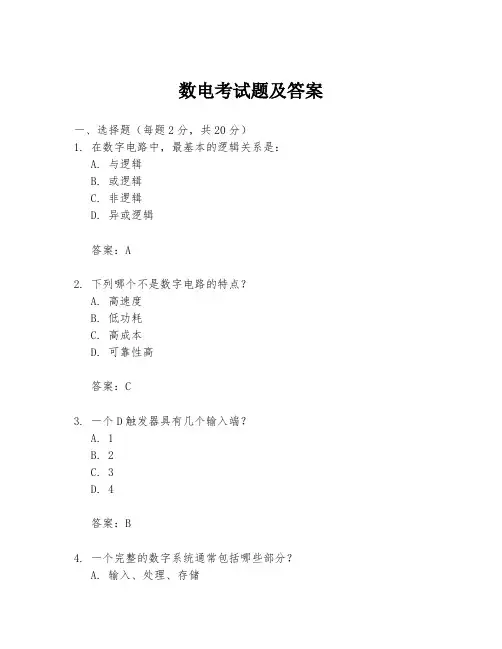

数电考试题及答案一、选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑关系是:A. 与逻辑B. 或逻辑C. 非逻辑D. 异或逻辑答案:A2. 下列哪个不是数字电路的特点?A. 高速度B. 低功耗C. 高成本D. 可靠性高答案:C3. 一个D触发器具有几个输入端?A. 1B. 2C. 3D. 4答案:B4. 一个完整的数字系统通常包括哪些部分?A. 输入、处理、存储B. 输入、处理、输出C. 输入、存储、输出D. 存储、处理、输出答案:B5. 下列哪个不是组合逻辑电路的特点?A. 输出只依赖于当前输入B. 输出在输入改变后立即改变C. 有记忆功能D. 结构简单答案:C6. 一个4位二进制计数器最多能计数到:A. 15B. 16C. 255D. 1023答案:B7. 在数字电路中,逻辑门的输入端可以连接多少个其他逻辑门的输出端?A. 1个B. 2个C. 3个D. 无限制答案:D8. 一个简单的数字钟电路至少需要几个计数器?A. 1B. 2C. 3D. 4答案:B9. 逻辑门的输出电压通常分为哪两个电平?A. 高电平、低电平B. 正电平、负电平C. 直流电平、交流电平D. 标准电平、非标准电平答案:A10. 下列哪个是数字电路设计中常用的仿真软件?A. MATLABB. AutoCADC. PhotoshopD. SolidWorks答案:A二、填空题(每空2分,共20分)1. 数字电路中最基本的逻辑关系包括______、______和非逻辑。

答案:与逻辑,或逻辑2. 一个3-8译码器有______个输入端,______个输出端。

答案:3,83. 在数字电路中,常用的计数器类型包括二进制计数器、______计数器和______计数器。

答案:十进制,BCD4. 一个8位寄存器可以存储______位二进制数。

答案:85. 触发器的两个稳定状态是______和______。

答案:0,1三、简答题(每题10分,共30分)1. 请简述数字电路与模拟电路的主要区别。

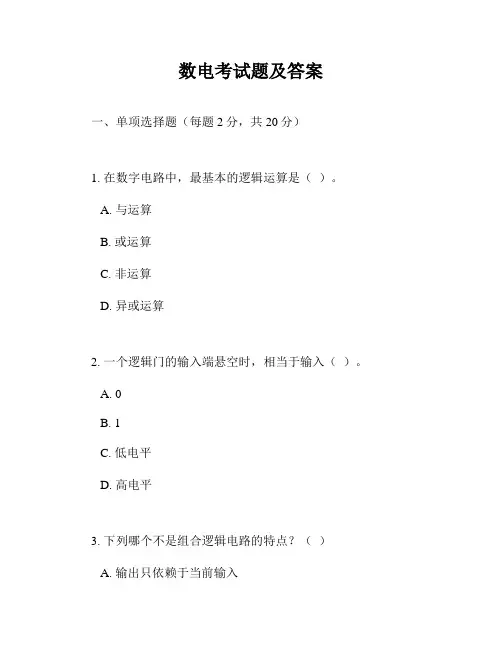

数电考试题及答案一、单项选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑运算是()。

A. 与运算B. 或运算C. 非运算D. 异或运算2. 一个逻辑门的输入端悬空时,相当于输入()。

A. 0B. 1C. 低电平D. 高电平3. 下列哪个不是组合逻辑电路的特点?()A. 输出只依赖于当前输入B. 输出与输入之间存在时延C. 输出与输入之间没有记忆功能D. 输出与输入之间存在时延4. 在数字电路中,一个触发器可以存储()位二进制信息。

A. 1B. 2C. 4D. 85. 一个4位二进制计数器可以计数的最大值是()。

A. 7B. 15C. 16D. 2556. 下列哪个不是时序逻辑电路的特点?()A. 输出不仅依赖于当前输入,还依赖于电路状态B. 具有记忆功能C. 输出与输入之间存在时延D. 输出只依赖于当前输入7. 在数字电路中,一个D触发器的输出Q与输入D的关系是()。

A. Q=DB. Q=非DC. Q=D的非D. Q=非D的非8. 一个3线-8线译码器可以译码的输入信号有()种。

A. 2B. 4C. 8D. 169. 在数字电路中,一个JK触发器可以工作在()状态。

A. 稳定状态B. 振荡状态C. 稳定状态和振荡状态D. 以上都不是10. 一个8位A/D转换器的量化步长是()。

A. 1/8B. 1/16C. 1/256D. 1/512二、填空题(每题2分,共20分)1. 在数字电路中,逻辑“与”运算的符号是___________。

2. 一个2进制计数器的计数范围是___________。

3. 一个3位二进制数可以表示的最大十进制数是___________。

4. 在数字电路中,逻辑“或”运算的符号是___________。

5. 一个4位二进制数可以表示的最大十进制数是___________。

6. 在数字电路中,逻辑“非”运算的符号是___________。

7. 一个5位二进制数可以表示的最大十进制数是___________。

数电试题及答案一、选择题1. 在数字电路中,最基本的逻辑关系有哪几种?A. 与、或、非B. 与、异或、同或C. 与、或、非、异或D. 与、或、非、同或、非门答案:C2. 下列哪个不是数字电路的特点?A. 抗干扰能力强B. 功耗低C. 运算速度快D. 模拟信号处理答案:D3. 逻辑门电路中,"0"和"1"分别代表的电压值是:A. 低电压和高电压B. 高电压和低电压C. 低电压和任意电压D. 任意电压和高电压答案:A二、填空题1. 数字电路是由_______和_______构成的电路。

答案:逻辑门;组合逻辑2. 一个基本的逻辑门至少需要_______个输入端。

答案:13. 一个完整的数字系统通常包括_______、_______和_______。

答案:输入设备;处理单元;输出设备三、简答题1. 请简述数字电路与模拟电路的区别。

答案:数字电路主要处理离散的数字信号,使用二进制逻辑来表示和处理信息,具有抗干扰能力强、功耗低、运算速度快等特点。

而模拟电路处理连续变化的模拟信号,能够模拟自然界的物理量变化,但易受干扰,运算速度相对较慢。

2. 什么是组合逻辑电路?它有哪些特点?答案:组合逻辑电路是由逻辑门组成的电路,其输出只依赖于当前的输入状态,不包含存储元件。

其特点是输出对输入具有即时响应,没有记忆功能,且输出状态的确定性使得电路设计和分析相对简单。

四、计算题1. 给定一个逻辑表达式:Y = A'B + AB',其中A和B是输入变量,Y是输出。

如果A=1,B=0,求Y的值。

答案:将A=1,B=0代入表达式,得到Y = 1'0 + 10' = 0 + 0 = 0。

2. 计算以下逻辑电路的输出Z,当A=1,B=0,C=1时。

逻辑电路表达式:Z = (A + B')(A' + B + C)答案:将A=1,B=0,C=1代入表达式,得到Z = (1 + 0')(1' + 0 + 1) = (1)(1 + 1) = 2,但由于逻辑运算中只考虑0和1,因此Z的实际值为1。

序列信号发生器

一、设计一个双序列信号发生器,同时输出的两个序列分别如下:

Y1:110101 (高位先出)

Y2:010110 (高位先出)

要求:

1. 简单写出设计过程,画出原理图(30分),有合理设计过程,且原理图正

确得30分,若使能端电平接错或者不接,扣5分.

2. 根据设计搭试电路(15分)

3. 静态验证结果并用双踪示波器观察并分别输入时钟和Y1、Y2输出的波

形。

(由老师检查,只能够正确实现模6计数器给15分,完全实现25分)(25分)

4. 在答卷上绘出输入时钟和Y1、Y2输出的波形。

(波形应注意相位对齐,

并至少画满一个周期,方波的边沿一定要画出)(10分)

相位对齐6分(每个波形3分),至少画满一个周期3分,方波边沿画出1分。

二、简答:

函数发生器的V oltage Out端口输出的方波能否作为TTL电路的输入信号,为什么?(20分)

答:直接输出不能,因为V oltage Out端口输出的方波是一个交流信号,其VH 和VL等于(1/2)VPP。

若想作为TTL电路的输入信号,则其VPP至少要为6V以上,否则不能满足TTL电平的要求;或者,若是VPP大于3V,则叠加上(1/2)VPP的直流电平后就可以作为TTL电路的输入信号了。

数电考试题及答案大学一、选择题(每题3分,共30分)1. 在数字电路中,最基本的逻辑关系不包括以下哪一项?A. 与(AND)B. 或(OR)C. 非(NOT)D. 异或(XOR)答案:D2. 二进制数1011转换为十进制数是多少?A. 8B. 11C. 13D. 15答案:D3. 下列哪个触发器可以实现边沿触发?A. SR触发器B. JK触发器C. D触发器D. T触发器答案:C4. 在CMOS技术中,一个N型MOSFET在其栅极施加()时导通。

A. 低电平B. 高电平C. 任意电平D. 不确定答案:B5. 一个4位二进制计数器的最大计数范围是多少?A. 4B. 8C. 16D. 32答案:C6. 以下哪个是数字电路的优点?A. 高速度B. 低功耗C. 高稳定性D. 所有以上答案:D7. 在数字电路中,逻辑0通常对应于哪个电压范围?A. 0VB. 接近0VC. 接近电源电压D. 任意电压答案:B8. 一个简单的RAM存储单元通常由多少个晶体管组成?A. 4B. 6C. 8D. 16答案:A9. 在数字电路设计中,布尔代数主要用于实现什么?A. 逻辑简化B. 信号放大C. 电源管理D. 时钟分配答案:A10. 以下哪个不是数字电路中的存储元件?A. 触发器B. 寄存器C. 计数器D. 门电路答案:D二、填空题(每题4分,共20分)11. 在数字电路中,一个基本的逻辑门至少需要________个输入端。

答案:212. 一个8位的寄存器可以存储的最大十进制数是________。

答案:25513. 在TTL电路中,逻辑1的最小输出电压是________V。

答案:2.014. CMOS门电路的功耗主要取决于________。

答案:开关频率15. 一个3-8线译码器可以将3位二进制信号转换为________个独立信号。

答案:8三、简答题(每题10分,共30分)16. 解释什么是同步计数器和异步计数器,并说明它们的区别。

数字电路考试题目及答案一、选择题(每题2分,共20分)1. 以下哪个选项是数字电路中的基本逻辑门?A. 与门B. 或门C. 非门D. 所有以上选项答案:D2. 在数字电路中,一个输入为0,另一个输入为1时,或门的输出是什么?A. 0B. 1C. 不确定D. 无输出答案:B3. 一个触发器的初始状态是0,当触发器的时钟信号上升沿到来时,触发器的状态会如何变化?A. 保持不变B. 变为1C. 变为0D. 随机变化答案:B4. 下列哪个不是数字电路中的计数器类型?A. 二进制计数器B. 十进制计数器C. 十六进制计数器D. 模拟计数器答案:D5. 在数字电路中,一个D触发器的Q输出和Q'输出之间的关系是什么?A. 相同B. 相反C. 无关系D. 有时相同有时相反答案:B6. 一个4位二进制计数器能表示的最大数值是多少?A. 15B. 16C. 255D. 256答案:B7. 以下哪个不是数字电路中的编码方式?A. 二进制编码B. 格雷码编码C. 十进制编码D. 模拟编码答案:D8. 在数字电路中,一个异或门的输出为1的条件是什么?A. 输入相同B. 输入不同C. 至少一个输入为0D. 至少一个输入为1答案:B9. 一个3线到8线解码器有多少个输入线?A. 3B. 4C. 5D. 8答案:A10. 在数字电路中,一个锁存器和触发器的主要区别是什么?A. 锁存器可以保持一个稳定的状态,而触发器不能B. 触发器可以保持一个稳定的状态,而锁存器不能C. 两者没有区别D. 两者都是存储设备答案:B二、填空题(每题2分,共20分)1. 在数字电路中,一个3位二进制计数器可以表示的最大数值是__7__。

2. 如果一个触发器的J和K输入都是1,则触发器的状态将会__翻转__。

3. 在数字电路中,一个4位二进制计数器有__16__个不同的状态。

4. 一个D触发器的输出Q在时钟信号的__上升沿__时更新。

5. 一个3线到8线解码器可以产生__8__个输出。

数字电路试题及答案一、选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑关系是:A. 与逻辑B. 或逻辑C. 非逻辑D. 异或逻辑答案:A2. 一个3输入的与门,当所有输入都为高电平时,输出为:A. 低电平B. 高电平C. 浮空D. 不确定答案:B3. 触发器的两个稳定状态是:A. 0和1B. 正和负C. 高和低D. 真和假答案:A4. 下列哪个不是数字电路的优点?A. 高速度B. 高稳定性C. 低功耗D. 易于集成答案:C5. 以下哪个是组合逻辑电路的特点?A. 输出状态只与当前输入有关B. 具有记忆功能C. 输出状态与过去输入有关D. 以上都不是答案:A6. 一个D触发器的Q端在时钟信号上升沿触发时,其输出将:A. 保持不变B. 变为0C. 变为1D. 翻转答案:D7. 以下哪个逻辑门不是基本逻辑门?A. 与门B. 或门C. 非门D. 异或门答案:D8. 以下哪个是数字电路设计中的同步设计?A. 所有信号在同一个时钟信号下操作B. 信号在不同的时钟信号下操作C. 信号没有时钟信号D. 以上都不是答案:A9. 一个4位二进制计数器,其计数范围是:A. 0到3B. 0到7C. 0到15D. 1到4答案:C10. 在数字电路中,布尔代数的基本原理不包括:A. 幂等律B. 互补律C. 反演律D. 欧拉定律答案:D二、简答题(每题10分,共30分)1. 简述数字电路与模拟电路的主要区别。

答:数字电路主要处理离散的数字信号,使用二进制数字表示信息,具有较高的抗干扰能力,易于实现大规模集成。

而模拟电路处理连续变化的模拟信号,使用电压或电流的连续变化来表示信息,通常需要较高的精度和稳定性。

2. 解释什么是时序逻辑电路,并给出一个例子。

答:时序逻辑电路是一种数字电路,其输出不仅依赖于当前的输入,还依赖于电路的历史状态。

这种电路通常包含存储元件,如触发器或寄存器。

一个常见的例子是计数器,它可以按照时钟信号的上升或下降沿进行计数。

数电考试题及答案一、选择题(每题1分,共10分)1. 数字电路中最基本的逻辑关系是()。

A. 与逻辑B. 或逻辑C. 非逻辑D. 异或逻辑2. 下列哪个不是数字电路的特点?()A. 抗干扰能力强B. 功耗低C. 体积小D. 工作速度慢3. 一个二进制数1011转换为十进制数是()。

A. 10B. 11C. 13D. 154. 在数字电路中,以下哪个不是基本的逻辑门?()A. 与门B. 或门C. 非门D. 放大门5. 触发器的主要用途是()。

A. 放大信号B. 存储信息C. 转换信号D. 滤波6. 一个完整的数字系统包括()。

A. 逻辑电路B. 电源C. 输入设备D. 所有选项7. 以下哪个不是数字电路的分类?()A. 组合逻辑电路B. 时序逻辑电路C. 模拟电路D. 存储电路8. 一个4位二进制计数器最多可以计数到()。

A. 8B. 16C. 32D. 649. 以下哪个是数字电路的优点?()A. 易受干扰B. 集成度高C. 功耗大D. 灵活性差10. 一个简单的数字钟至少需要多少个触发器?()A. 1B. 2C. 4D. 6二、填空题(每空1分,共10分)1. 数字电路中,最基本的逻辑运算包括________、________和________。

2. 一个二进制数1101转换为十进制数是________。

3. 触发器的两个稳定状态是________和________。

4. 一个数字电路系统由________、________和________组成。

5. 一个4位二进制计数器的计数范围是________到________。

三、简答题(每题5分,共20分)1. 简述数字电路与模拟电路的区别。

2. 解释什么是组合逻辑电路和时序逻辑电路。

3. 描述数字电路中的触发器是如何工作的。

4. 什么是数字电路的抗干扰能力?四、计算题(每题10分,共20分)1. 给定一个二进制数101101,转换为十进制数是多少?2. 如果一个数字钟使用4位二进制计数器,计算它的计数周期是多少秒?(假设时钟频率为1Hz)五、综合题(每题15分,共30分)1. 设计一个简单的数字电路,实现两个输入信号A和B的异或逻辑功能。

1、检测74LS00,74LS86逻辑功能。

(报告中要画出检测电路图)………………………………………………………………………………………….2、用四2输入异或门(74LS86)和四2输入与非门(74LS00)设计一个一位全加器。

(要求写清楚设计过程)…………………………………………………………………………………………….3、在一个射击游戏中,每人可打三枪,一枪打鸟(A),一枪打鸡(B),一枪打兔子(C)。

规则是:打中两枪并且其中有一枪必须是打中鸟者得奖(Z)。

试用与非门设计判断得奖的电路。

(请按照设计步骤独立完成之,要求写清楚设计过程)…………………………………………………………………………….4、测试74LSl39中一个2—4译码器的逻辑功能。

……………………………………………………………………………………………………..5、利用使能端将两个2线-4线译码器组合成一个3线-8线译码器(设计性内容)6、验证数据选择器74LS153的功能。

………………………………………………………………………………………………….7、用数据选择器74LS153设计1位全加器。

…………………………………………………………………………………………………….8、用74LS00构成基本RS触发器并验证触发器功能。

9、用74LS74验证D触发器的功能。

10、用74LS112验证JK触发器的功能。

11、用74ls74构成二进制计数器(分频器),电路图如下图所示Q0 Q1 Q2 Q312、用74ls162十进制同步计数器构成十进制计数器。

(1)实现复位(2)实现预置(3)实现计数13、用 1 片 74LS162 和l片74LSOO 采用复位法构成一个模 7 计数器。

14、用 1 片 74LS162 和l片74LSOO 采用置位法构成一个模 7 计数器。

大学数电测试题及答案一、选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑运算是:A. 与运算B. 或运算C. 非运算D. 异或运算答案:A2. 以下哪个不是数字电路的组成部分?A. 逻辑门B. 触发器C. 电阻D. 电容器答案:C3. 一个基本的RS触发器由几个逻辑门组成?A. 1个B. 2个C. 3个D. 4个答案:B4. 在数字电路中,一个D触发器的输出在时钟脉冲的哪个时刻更新?A. 上升沿B. 下降沿C. 任何时刻D. 时钟脉冲的中间时刻答案:A5. 以下哪个是组合逻辑电路的特点?A. 有记忆功能B. 输出只依赖于当前输入C. 输出依赖于历史输入D. 需要时钟信号答案:B6. 一个4位二进制计数器的最大计数是:A. 8B. 16C. 32D. 64答案:B7. 在数字电路中,一个锁存器与一个触发器的主要区别是什么?A. 锁存器可以保持数据,触发器不能B. 触发器可以保持数据,锁存器不能C. 锁存器和触发器没有区别D. 锁存器需要外部时钟信号,触发器不需要答案:B8. 以下哪个逻辑门可以实现逻辑非运算?A. 与门B. 或门C. 非门D. 异或门答案:C9. 一个典型的二进制加法器可以处理的最大输入是:A. 0和1B. 1和0C. 1和1D. 0和0答案:C10. 在数字电路中,一个寄存器的主要功能是什么?A. 进行算术运算B. 存储数据C. 产生时钟信号D. 转换模拟信号为数字信号答案:B二、填空题(每题2分,共20分)1. 在数字电路中,逻辑“1”通常表示为电压______。

答案:高电平2. 一个完整的数字系统通常包括输入设备、______和输出设备。

答案:处理单元3. 一个8位二进制数可以表示的最大十进制数是______。

答案:2554. 在数字电路中,一个计数器的进位输出通常在计数到______时发生。

答案:最大值5. 一个典型的二进制减法器在减法运算中使用的是______。

数字电路试题及答案一、选择题1. 数字电路的基本组成单元是:A. 逻辑门B. 电源C. 电阻D. 电源线答案:A2. 下列哪种逻辑门的输出只有当所有输入都为高电平时才为高电平?A. 与门B. 或门C. 非门D. 异或门答案:A3. 使用逻辑门和触发器可以构建哪种类型的数字电路?A. 计数器B. 比较器C. 放大器D. 滤波器答案:A4. 下列哪种逻辑门的输出为输入信号的反相?A. 与门B. 或门C. 非门D. 异或门答案:C5. 在数字电路中,使用哪种逻辑门可以实现逻辑加法?A. 与门B. 或门C. 非门D. 异或门答案:D二、填空题1. 以下真值表表示的逻辑函数是______。

输入A | 输入B | 输出Y-----------------------------0 | 0 | 10 | 1 | 01 | 0 | 01 | 1 | 1答案:异或门2. 基本的二进制加法器是由______和______构成的。

答案:半加器和全加器3. 在数字电路中,时钟信号被用于控制______。

答案:触发器4. 使用______逻辑门,可以实现任意逻辑函数。

答案:与、或、非、与非5. ______________电路可以将电压信号进行放大。

答案:放大器三、解答题1. 简述半加器的功能和工作原理。

答案:半加器是一种能够实现二进制数相加的数字电路组件。

它接受两个输入信号A和B,并产生两个输出信号Sum和Carry。

Sum表示相加的结果,Carry表示进位的情况。

半加器的工作原理如下:- 将输入信号A和B分别输入两个异或门,得到的输出连接到一个与门,得到Sum。

- 将输入信号A和B分别输入一个与门和一个与非门,得到的输出连接到一个或门,得到Carry。

2. 请简要解释触发器的作用及其类型。

答案:触发器是一种能够存储和记忆输入信号状态的数字电路组件。

它可以在时钟信号的控制下,将输入的电平状态保持在输出上,实现状态的存储和延迟功能。

数字电路实验考试参考题目

1.请采用两种方法(分别用与非门器件和数据选择器)设计一个三人表决器。

2.请采用两种方法(分别用与非门器件和数据选择器)设计一个四人表决器。

3.采用数据选择器(74LS151)设计完成下列逻辑函数:

F1=A BC+A B D+B C D+AC D;

F2=ABC+BCD+ACD+ABD

4.利用JK触发器设计一个异步四进制计数器(可采用74LS73),并用示波器观测电路输

入、输出波形。

5.设计一个模21的计数器(可采用74LS390或74LS192等),用发光二极管观察并记录

电路的所有有效计数状态。

6.设计一个模22的计数器(可采用74LS390或74LS192等),用发光二极管观察并记录

电路的所有有效计数状态。

7.设计一个模23的计数器(可采用74LS390或74LS192等),用发光二极管观察并记录

电路的所有有效计数状态。

8.设计一个模24的计数器(可采用74LS390或74LS192等),用发光二极管观察并记录

电路的所有有效计数状态。

9.设计一个模25的计数器(可采用74LS390或74LS192等),用发光二极管观察并记录

电路的所有有效计数状态。

10.设计一个模20的计数器(可采用74LS390或74LS192等),用发光二极管观察电路的

所有有效计数状态;并用示波器观测计数器的输入输出端波形。

11.采用移位寄存器设计一个具有自启动功能的四位环形计数器,记录电路所有状态(包括

由偏离态进入有效循环的过程),并画出状态转移图。

12.设计一个具有自启动功能的、有效状态分别为1000,0100,0010,0001的四位右移环

形计数器。

13.设计一个具有自启动功能的、有效状态分别为0001,0010,0100,1000的四位左移环

形计数器。

14.设计一个具有自启动功能的、有效状态分别为1110,1101,1011,0111的四位左移环

形计数器。

15.设计一个具有自启动功能的、有效状态分别为1110,0111,1011,1101的四位右移环

形计数器。

16.设计一个具有自启动功能的、有效状态分别为1100,1001,0011,0110的四位左移环

形计数器。

17.设计一个具有自启动功能的、有效状态分别为1100,0110,0011,1001的四位右移环

形计数器。

18.采用2MHZ的晶体振荡器、与非门、电阻等器件设计一个晶体稳频多谐振荡电路,经

分频后,电路输出脉冲信号频率为1MHZ。

19.采用555定时器设计电路,要求输出一个频率为1KHZ的脉冲信号,并用示波器观测电

路输出波形。

20.采用大规模集成存储器、编程器、计数器等元件和设备,设计完成一个八路彩灯控制电

路。

(可能还有小范围调整,请大家继续关注网站通知)。