原边反馈反激式

- 格式:doc

- 大小:330.00 KB

- 文档页数:10

FSR原边反馈反激式变换器及原理FSR(Flyback Switching Regulator)原边反馈反激式变换器是一种常见的开关电源拓扑结构,可以同时实现输入输出电压的隔离和转换。

本文将详细介绍FSR原边反馈反激式变换器的工作原理及其特点。

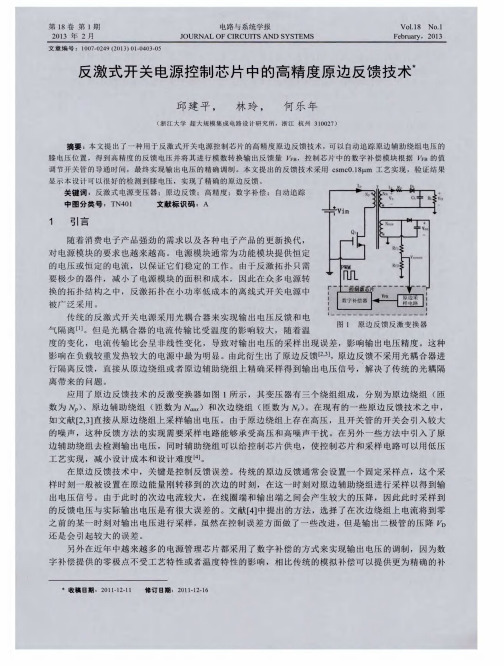

[图片]在FSR原边反馈反激式变换器中,电源输入通过变压器的一侧加入,并由输入电容进行滤波。

控制IC产生的PWM信号控制MOSFET的开关,将输入电压转换为短暂的高功率矩形脉冲,并传输给变压器。

由于变压器的变比,高功率脉冲信号被变压器转换为低功率矩形脉冲信号,然后通过输出二次侧的整流和滤波电路得到所需的输出电压。

1.输入滤波和整流:电源输入先通过输入电容进行滤波,降低电源噪声。

然后,经过整流电路将交流输入转换为直流输入。

2.反激开关:控制IC通过控制频率和占空比产生PWM信号,控制功率MOSFET的通断。

当MOSFET导通时,电源输入电源通过变压器传递到输出端;当MOSFET截止时,输出端的电压会产生反向电压,称为反激。

3.变压器:变压器是FSR变换器的核心组件。

它以一定的变比将输入电压转换为输出电压。

当功率MOSFET导通时,输入脉冲能量被储存在变压器的磁场中;当MOSFET截止时,储存在磁场中的能量通过变压器的绕组耦合到二次侧,并转换为输出电压。

4.输出整流和滤波:由于输出是交流信号,需要进行整流和滤波处理,将其转换为直流输出。

通常,采用整流二极管和输出电容来实现。

1.隔离性:由于变压器的存在,输入与输出之间具有隔离性,使输出与输入之间不会存在电气连接。

这保证了输出的安全性和稳定性。

2.最小化元件数量:FSR变换器相对于其他开关电源结构,所需元件数量较少,减小了系统的复杂性。

3.简化控制电路:FSR变换器采用原边反馈控制方式,可实现电流和电压双回路控制,简化了控制电路的设计。

4.可实现多输出:FSR变换器可通过变压器的设计来实现多种输出,满足不同应用的需求。

开关电源原边反馈技术

原边反馈(PSR)简介

●在小功率消费类电子应用中,反激式电源是主流,因为反激式电源非常适合小功率段,同时天然提供了隔离的效果。

●隔离后,如果要检测输出的情况,需要用隔离元件,比如光耦等,这样就增加了电源的成本,光耦本身的寿命也会成为电源的瓶颈,基于此,开发出了原边反馈技术。

-原边反馈不从输出直接采样,而是从初级线圈采样,通过初级线圈的情况来计算次级线圈的情况,进一步推算输出的情况。

-部分信息难以从初级线圈直接得到,因此通常还使用一个辅助线圈,辅助线圈和初级线圈共地,和次级隔离

辅助线圈的用途

●增加辅助线圈会增加成本和复杂度,因此,最好能让辅助线圈完成更多的工作,一般辅助线圈都同时做2件事情:

-反映初级线圈和次级线圈的情况,辅助线圈通过电阻分压,将原边和副边的电压情况反映在VSES点,此时辅助线圈和原边/副边构成变压器。

和初级线圈形成一个反激结构,给IC供电,由于反激结构本身无法恒压,因此要加一个限压的二极管。

不使用辅助线圈是否可行

●如果不要求辅助线圈供电,那么是否可以用其他检测方法,比如在初级线圈上检测来做原边反馈?

●理论上是可行的,思路如下:

-在初级线圈上并联一个高阻支路,对初级线圈进行采样,同时提供TOFF期。

一种多模式控制原边反馈反激变换器设计刘天翔;倪超;谢君甫【摘要】原边反馈反激变换器因其体积小、效率高且能够实现隔离等特点在中小功率电源领域中使用十分广泛.针对传统的单模式控制方式反激变换器不能在全负载范围内做出合适的效率优化的缺点,采用多模式控制方法,提高变换器轻载效率.本文基于凌特公司的控制芯片LT8303,设计完成了一款5V/2W的多模式控制反激变换器.详细分析了该电路的工作原理,并给出关键参数设计原则.实验结果表明该反激变换器具有轻载效率高,负载调节性能好等优点.【期刊名称】《电子设计工程》【年(卷),期】2019(027)008【总页数】5页(P85-89)【关键词】多模式控制;原边反馈;反激变换器;LT8303【作者】刘天翔;倪超;谢君甫【作者单位】中国航空工业集团公司雷华电子技术研究所江苏无锡 214063;中国航空工业集团公司雷华电子技术研究所江苏无锡 214063;中国航空工业集团公司雷华电子技术研究所江苏无锡 214063【正文语种】中文【中图分类】TN86在现代电子设备设计中,节约电源成本,提高电源转换效率日益受到人们的关注。

国际能源署的“一瓦计划”以及美国的“能源之星”计划等都对电源的平均效率及待机功耗做了严格的规定[1]。

传统的原边反馈反激变换器采用单一的PWM或PFM控制方式,系统平均效率较低[2-4]。

为提高电源转换效率,目前主要通过优化电源控制方式实现。

在不同负载条件下,开关电源内部各损耗占比不同。

轻载时功率器件的开关损耗以及辅助电路的附加损耗占总损耗的主要部分;重载时功率器件的导通损耗及导通回路的电阻损耗占总损耗的主要部分。

传统的单一模式控制方式难以在整个负载范围内全面的进行效率优化[5-6]。

因此多模式控制方案,即在不同负载条件下采用不同的模式控制方法,成为国内外研究的热点方向[7-9]。

本文基于凌特公司的LT8303控制芯片,设计了一款多模式控制原边反馈的反激变换器,有效的提高变换器轻载及待机时的效率。

高功率因数原边反馈反激IC芯片1. 导言高功率因数原边反馈反激IC芯片是一种用于高功率因数电源的控制芯片,其具有提高功率因数和效率、减小器件尺寸和成本等优点。

本文将介绍高功率因数原边反馈反激IC芯片的原理、特点、应用和发展趋势。

2. 原理高功率因数原边反馈反激IC芯片采用原边反馈控制,通过测量输入电压的波形来实现功率因数校正。

其电路包括功率因数校正电路、反激控制电路和监控电路。

功率因数校正电路用来对输入电压进行谐振,使其与输入电流同相位,从而实现功率因数校正。

反激控制电路用来调节输出电压,使其稳定在设定值。

监控电路用来监测输入电压、输出电压和电流等参数,并根据实际情况进行调节。

3. 特点(1)高功率因数:采用原边反馈控制,能够实现高功率因数,提高系统的功率因数,使其接近1,减小谐波对电网的污染。

(2)高效率:由于功率因数的改善,整个系统的效率也得到提高,能够减少能量的损耗,降低电能的消耗。

(3)小尺寸:高功率因数原边反馈反激IC芯片集成了多个功能模块,能够实现电源控制的全面功能,从而减小了电源的尺寸。

(4)低成本:由于集成度高、功率因数高和效率高,能够减少材料和成本,降低产品的制造成本。

4. 应用高功率因数原边反馈反激IC芯片广泛应用于电力电子、LED照明、工业控制等领域。

在电力电子领域,其功率因数校正功能可以提高电源系统的功率因数,减小谐波对电网的污染,满足各种场景下的电能质量要求。

在LED照明领域,其小尺寸和高功率因数等特点能够满足LED照明驱动的需求,提高LED电源的性能。

在工业控制领域,其高效率和稳定性能能够保证工业设备的稳定运行,提高工作效率。

5. 发展趋势随着电力电子、LED照明、工业控制等领域的不断发展,对功率因数和能效的要求也越来越高,因此高功率因数原边反馈反激IC芯片将会在未来有更加广阔的应用前景。

未来,高功率因数原边反馈反激IC芯片将会更加注重集成度、高效率和高功率因数等方面的性能,以满足不同领域对电源的要求。

目前比较流行的低成本、超小占用空间方案设计基本都是采用PSR原边反馈反激式,通过原边反馈稳压省掉电压反馈环路(TL431和光耦)和较低的EMC辐射省掉Y电容,不仅省成本而且省空间,得到很多电源工程师采用。

比较是新技术,目前针对PSR原边反馈开关电源方案设计的相关讯息在行业中欠缺。

下面结合实际来讲讲我对PSR原边反馈开关电源设计的“独特”方法——以实际为基础。

要求条件:全电压输入,输出5V/1A,符合能源之星2之标准,符合IEC60950和EN55022安规及EMC标准。

因充电器为了方便携带,一般都要求小体积,所以针对5W的开关电源充电器一般都采用体积较小的EFD-15和EPC13的变压器,此类变压器按常规计算方式可能会认为CORE太小,做不到,如果现在还有人这样认为,那你就OUT了。

磁芯以确定,下面就分别讲讲采用EFD15和EPC13的变压器设计5V/1A 5W的电源变压器。

1. EFD15变压器设计目前针对小变压器磁芯,特别是小公司基本都无从得知CORE的B/H曲线,因PSR线路对变压器漏感有所要求。

所以从对变压器作最小漏感设计入手:已知输出电流为1A,5W功率较小,所以铜线的电流密度选8A/mm2,次级铜线直径为:SQRT(1/8/3.14)*2=0.4mm。

通过测量或查询BOBBIN资料可以得知,EFD15的BOBBIN的幅宽为9.2mm。

因次级采用三重绝缘线,0.4mm的三重绝缘线实际直径为0.6mm.为了减小漏感把次级线圈设计为1整层,次级杂数为:9.2/0.6mm=15.3Ts,取15Ts.因IC内部一般内置VDS耐压600~650V的MOS,考虑到漏感尖峰,需留50~100V的应力电压余量,所以反射电压需控制在100V以内,得:(Vout+VF)*n<100,即:n<100/(5+1),n<16.6,取n=16.5,得初级匝数NP=15*16.5=247.5取NP=248,代入上式验证,(Vout+VF)*(NP/NS)<100,即(5+1)*(248/15)=99.2<100,成立。

确定NP=248Ts.假设:初级248Ts在BOBBIN上采用分3层来绕,因多层绕线考虑到出线间隙和次层以上不均匀,需至少留1Ts余量(间隙)。

得:初级铜线可用外径为:9.2/(248/3+1)=0.109mm,对应的实际铜线直径为0.089mm,太小(小于0.1mm不易绕制),不可取。

假设:初级248Ts在BOBBIN上采用分4层来绕,初级铜线可用外径为:9.2/(248/4+1)=0.146mm,对应的铜线直径为0.126mm,实际可用铜线直径取0.12mm。

IC的VCC电压下限一般为10~12V,考虑到至少留3V余量,取VCC电压为15V左右,得:NV=Vnv/(Vout+VF)*NS=15/(5+1)*15=37.5Ts,取38Ts.因PSR采用NV线圈稳压,所以NV的漏感也需控制,仍然按整层设计,得:NV线径=9.2/(38+1)=0.235mm, 对应的铜线直径为0.215mm,实际可用铜线直径取0.2mm。

也可采用0.1mm双线并饶到此,各线圈匝数就确定下来了。

下面来确定绕线顺序。

因要工作在DCM模式,且采用无Y设计,DI/DT比较大,变压器磁芯研磨气隙会产生穿透力强杂散磁通导致线圈测试涡流,影响EMC噪音,所以需先在BOBBIN上采用0.1mm直径的铜线绕满一层作为屏蔽,且引出端接NV的地线绕完屏蔽后,保TAPE1层;再绕初级,按以上计算的分4层绕制,完成后包TAPE 1层;为减小初次级间的分布电容对EMC的影响,再用0.1mm的线绕一层屏蔽,包TAPE 1层;再绕次级,包TAPE 1层;再绕反馈,包TAPE 2层。

可能有人会说:怎么没有计算电感量?因前面说了,CORE的B/H不确定,所以得先从确定饱和AL值下手。

把变压器CORE中柱研磨一点,然后装上以上方式绕好的线圈装机,并用示波器检测Rsenes上的波形,见下图中R5.输入AC90V/50Hz,慢慢加载,观察CORE有没有饱和,如果有饱和迹象,拆下再研磨……直到负载到1.1~1.2A刚好出现一点饱和迹象,(此波形需把波形放大到满屏观察最佳)OK,拆下变压器测量电感量,此时所测得的电感量作为最大值依据,再根据厂商制造能力适当留+3%~+5%的误差范围和余量,如:测量为2mH,则取2-2*0.05=1.9mH,误差为+/-0.1mH.现在再来验证以上参数变压器BOBBIN的绕线空间。

已知:E1和E2铜线直径为0.1mm,实际外径为0.12mm;NP铜线直径为0.12mm,实际外径为0.14mm;NS铜线直径为0.4mm,实际外径为0.6mm;TAPE采用0.025mm厚的麦拉胶纸。

A.NV若采用铜线直径为0.2mm,实际外径为0.22mm线包单边厚度为:E1+TAPE+NP+TAPE+E2+TAPE+NS+TAPE+NV+TAPE=0.12+0.025+0.14*4+0.025+0.12+0.025+0.6+0.025+0.22+0.025*2=1.77mm.B.NV若采用铜线直径为0.1mm双线并饶,实际外径为0.12mm线包单边厚度为:E1+TAPE+NP+TAPE+E2+TAPE+NS+TAPE+NV+TAPE=0.12+0.025+0.14*4+0.025+0.12+0.025+0.6+0.025+0.12+0.025*2=1.67mm.测量或查EFD15的BOBBIN的单边槽深为2.0mm,所以以上2种方式绕制的变压器都可行。

2. EPC13的变压器设计依然沿用以上设计方法,测量或查BOBBIN资料可得EPC13 BOBBIN幅宽为6.8mm,次级匝数为:6.8/0.6=11.3Ts,取11Ts.初级匝数为:11*16.5=181.5Ts,取182Ts.反馈匝数为:15/(5+1)*11=27.5Ts,取28Ts.继续,EPC13的绕线方式同EFD15,再这里就不再重复了。

以上变压器设计出的各项差数是以控制漏感为出发点的,各项参数(肖特基的VF,MOS管的电压应力余量……)都是零界或限值,实际设计中会因次级绕线同名端对应输出PIN位出现交叉,或输出飞线套铁氟龙套管,或供应商的制程能力,都会使次级线圈减少1~2圈,对应的初级和反馈也需根据匝比减少圈数;另,目前市场的竞争导致制造商把IC内置MOS管的VDS耐压减小一点来节省成本,为保留更大的电压应力余量,需再减少初级匝数;以上的修改都会对EMC辐射造成负面影响,对应的取舍还需权衡,但前提是必须使产品工作在DCM模式。

从08年市场上推出PSR原边反馈方案到现在我一直都有在用此方案设计产品,回顾看看,市场上也出现了很多不同品牌的PSR方案,但相对以前刚推出的PSR控制IC来说,有因市场反映不良而不断改进的部分,但也有因为恶性竞争而COST DOWN的部分。

主要讲讲COST DOWN的部分因受一些品牌在IC封装工艺上的专利限制,所以目前大部分的内置MOS的IC(不仅是PSR控制IC,也包括PWM 控制IC)采用的是在基板上置入控制晶圆和MOS晶圆,之间用金线作跳线连接,这样就有2个问题产品了:1. 金线带来的EMC辐射。

2. 研制控制晶圆的公司可以自己控制控制晶圆的成本,但MOS晶圆一般采用的从MOS晶圆生产上购买,这样一来,MOS晶圆的成本控制也成为IC成本控制的案上肉。

辐射可以采用优化设计来控制。

但MOS晶圆的COST DOWN的路径来源于降低其VDS的耐压,目前已有很多不同品牌的IC将VDS为650V的内置MOS降到620~630V,甚至560~600V。

这样一来,只控制漏感降低VDS峰值电压是不够的,所以还需为VDS保留更大的电压应力余量。

面再以EPC13为实例,讲讲优化设计后的变压器设计。

方法同上……先计算出次级,因考虑到输出飞线套铁氟龙套管或输出线与BOBBIN PIN位交叉,所以需预留1匝空间,得,次级匝数为:6.8/0.6-1=10.3,取10Ts.再计算初级匝数,因考虑到为MOS管留更大的电压应力余量,所以反射电压取之前的75%得:(Vout+VF)*n<100*75%,输出5V/1A,采用2A/40V的肖特基即可,2A/40V的肖特基其VF值一般为0.55V。

代入上式得:n<13.51,取13.5,得NP=10*13.5=135Ts.代入上式验证(5+0.55)*(135/10)=74.925<75,成立。

确定NP=135Ts.面再计算反馈匝数,依然取反馈电压为15V,得,15/(5+0.55)*10=27Ts电感量与间隙的关系:L=N2*ALCORE研磨后AL会变小,也就是气息增大,AL会变小,匝数不变的情况下,电感量也就小了。

PSR电路一般OCP设计的不是很大,一般在120%左右,如果你测试是是以输入AC90/50Hz(没打错,不是60Hz哦),输出帯载到1.2A刚好出现一点饱和,实际烧机1.0A是不会饱和的,你可以试试,实际烧机后的OCP会在110%左右。

变压器10%的误差太大了点吧,变压器采用机械研磨误差没那么大。

匝数多可以提高一点电感量,可以让负载时的频率辐射低些,当然,你也可以把EFD15的匝数减少些,但EMC的处理就和EPC13一样需特别注意布线EE16的变压器绕142TS,1.85的感量多饱和余量来说留得还是比较大的,这个匝比不错,但感量低了会影响工作频率也会影响电流峰值,建议把感量做到2.0~2.2mH.你可以试一下,就这个匝数和匝比不变,用1.85和2.0mH的变压器测试比较下,EMC影响比较大。

找不到放大后的图,就看看这个没放大的吧。

把这个波形在示波器上拉宽,看那条上升的斜线,那是电流上升的波形,要保持是一条缓慢上升的斜线,如果在顶端出现突然上升,说明变压器有饱和迹象。

当然,变压器有一点饱和迹象,在实际中是可以长期烧机的,但因为电流突然上升会测试较强的辐射噪音,所以要控制到变压器不饱和为佳。

但,不饱和就得再研磨CORE,降低电感量,但CORE研磨多了,气隙大了,漏感和涡流也会增大,同样会影响EMC噪音,所以把CORE研磨到零界饱和点是最佳取舍方式。

先不说你计算电感量的B/H值从何来,你可以权衡下你计算出的电感量在EMC取舍上有此方式直接和有效吗?我认为我这种方式更有效也更直接。

空载与满载切换时,输出电压的过冲和下冲与变压器有一定关系,但此问题主要是PSR IC延时检测造成的,解决方法我会在后续讲解,不是变压器的问题。

我们的客人在别家公司做的产品出了这个问题,而我们的没有,因此我们接到了一个转过来的200K订单呢。

EMC图纸我得整理下,因为之前认证整改的产品测试PASS一般就没管它。