2018年宁波大学考博试题3810数字集成电路设计基础(A卷)

- 格式:pdf

- 大小:408.95 KB

- 文档页数:4

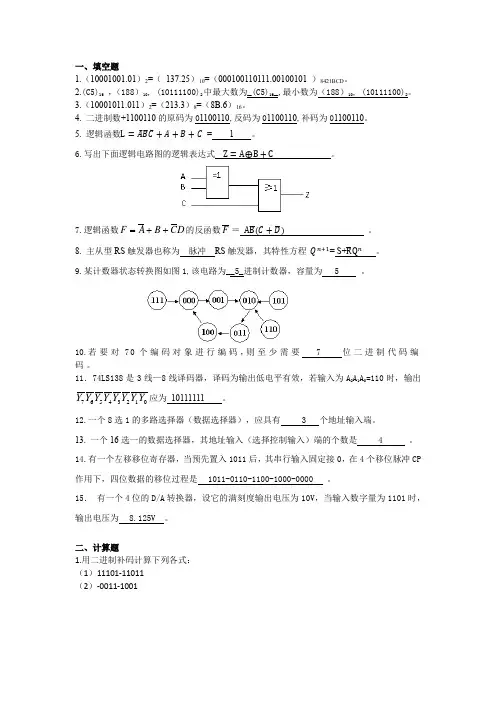

一、填空题1.(10001001.01)2=( 137.25)10=(000100110111.00100101 )8421BCD 。

2.(C5)16 ,(188)10, (10111100)2中最大数为_(C5)16_,最小数为(188)10, (10111100)2。

3.(10001011.011)2=(213.3)8=(8B.6)16。

4. 二进制数+1100110的原码为01100110,反码为01100110,补码为01100110。

5. 逻辑函数L =A B̅C +A +B +C = 1 。

6.写出下面逻辑电路图的逻辑表达式 Z =A⨁B +C 。

7.逻辑函数D C B A F ++=的反函数F = AB̅(C +D ̅) 。

8. 主从型RS 触发器也称为 脉冲 RS 触发器,其特性方程 Q n+1= S+R ̅Q n 。

9.某计数器状态转换图如图1,该电路为__5_进制计数器,容量为 5 。

10.若要对70个编码对象进行编码,则至少需要 7 位二进制代码编码。

11.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出01234567Y Y Y Y Y Y Y Y 应为 10111111 。

12.一个8选1的多路选择器(数据选择器),应具有 3 个地址输入端。

13. 一个16选一的数据选择器,其地址输入(选择控制输入)端的个数是 4 。

14.有一个左移移位寄存器,当预先置入1011后,其串行输入固定接0,在4个移位脉冲CP 作用下,四位数据的移位过程是 1011-0110-1100-1000-0000 。

15. 有一个4位的D/A 转换器,设它的满刻度输出电压为10V ,当输入数字量为1101时,输出电压为 8.125V 。

二、计算题1.用二进制补码计算下列各式: (1)11101-11011 (2)-0011-10012.用卡诺图化简下列逻辑函数为最简与—或表达式: (1){Z =AB A B C A B C +••+••BC =0(2)Y (A,B,C,D )=∑m(1,3,8,9,10,11,14,15)(1)解:真值表 卡诺图化简A B C Z0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 × 1 0 0 1 1 0 1 1 1 1 0 0 1 1 1 ×表达式: Z=C B A B A ++ (2)解:3.下图电路中,G 1和G 2为OC 与非门,输出为线与结构。

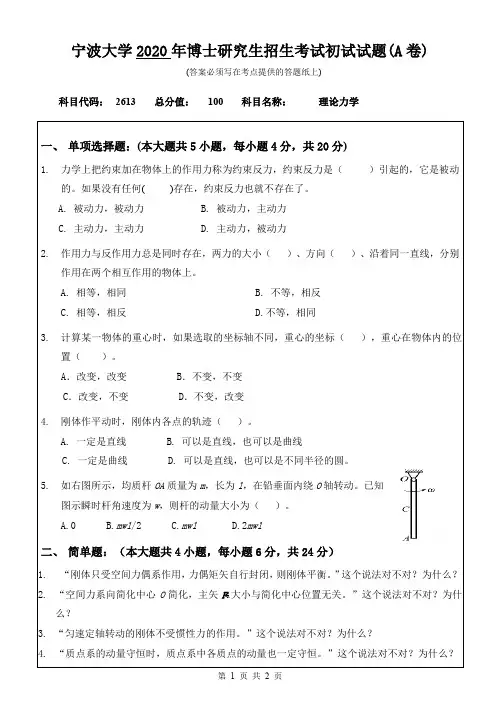

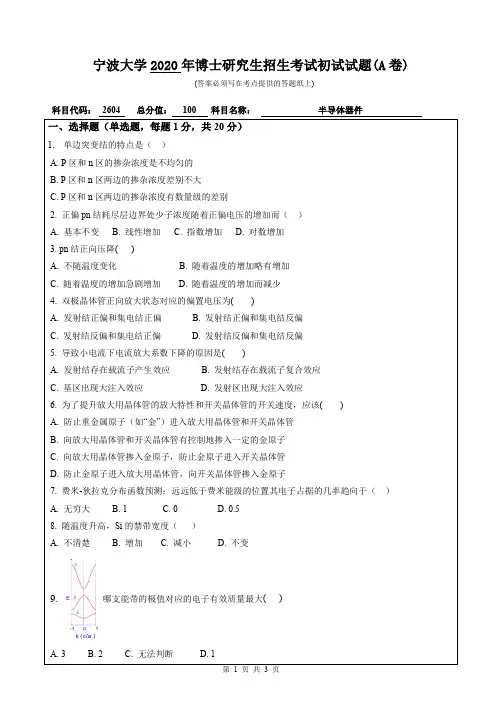

(答案必须写在考点提供的答题纸上) A. 3 B. 2(答案必须写在考点提供的答题纸上)(答案必须写在考点提供的答题纸上)考试科目:半导体器件科目代码:2604适用专业:微纳信息系统一、单项选择题:本大题共5小题,每小题5分,共25分。

在每小题列出的四个选项中只有一个是符合题目要求的,请将其代码填在题前的括号内。

错选、多选或未选均不得分。

()1.在半导体太阳能电池中,关于暗电流说法正确的是A.没有光照时电流B.由外加偏压产生C.其方向与光电流方向相同D.由光生电压降落在势垒区而产生()D正常工作时,其MOS单元半导体表面所处状态是A.强反型B.多子积累C.深耗尽D.多子耗尽()3.在以下复合跃迁中,非辐射复合跃迁是A.带间复合B.激子复合C.俄歇复合D.不存在()4.与LED量子效率有关的因素有A.结两侧参杂浓度B.结深C.表面反射D.以上都有关()5.太阳能电池工作时,对应P-N结内部处于:A.正偏电压B.反偏电压C.没有电压D.耗尽第1页共2页考试科目:半导体器件科目代码:2604适用专业:微纳信息系统二问答题(共35分)1.采用载流子扩散与漂移的观点分析PN结的单向导电性。

(10分)2.试述NPN双极型晶体管的四种工作模式。

(15分)3.试述金属-半导体接触:肖特基接触与欧姆接触的各自特点。

(10分)三.计算与推导(共40分)1.计算一硅p-n结在300K时的内建电势,其N A=1018cm-3和N D=1015cm-3.(10分)2.一理想晶体管其发射效率为0.999,集基极漏电流为10μA,假设I B=0,请算出由空穴所形成的放大模式发射极电流。

(15分)3.简述评估太阳能电池器件性能的四个基本参数,那些因素会影响太阳能电池器件性能(15分)第2页共2页考试科目:半导体器件科目代码:2604适用专业:微纳信息系统第1页共2页一、判断题(共20分,每题1分)1.()半导体材料的导电性能介于导体和绝缘体之间。

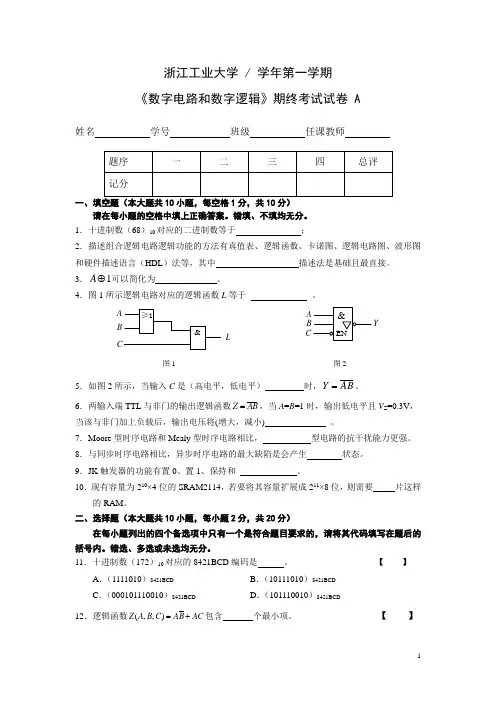

浙江工业大学 / 学年第一学期 《数字电路和数字逻辑》期终考试试卷 A姓名 学号 班级 任课教师一、填空题(本大题共10小题,每空格1分,共10分)请在每小题的空格中填上正确答案。

错填、不填均无分。

1.十进制数(68)10对应的二进制数等于 ;2.描述组合逻辑电路逻辑功能的方法有真值表、逻辑函数、卡诺图、逻辑电路图、波形图和硬件描述语言(HDL )法等,其中 描述法是基础且最直接。

3.1A⊕可以简化为 。

4.图1所示逻辑电路对应的逻辑函数L 等于 。

A B L≥1&CYC图1 图25.如图2所示,当输入C 是(高电平,低电平) 时,AB Y =。

6.两输入端TTL 与非门的输出逻辑函数AB Z =,当A =B =1时,输出低电平且V Z =0.3V ,当该与非门加上负载后,输出电压将(增大,减小) 。

7.Moore 型时序电路和Mealy 型时序电路相比, 型电路的抗干扰能力更强。

8.与同步时序电路相比,异步时序电路的最大缺陷是会产生 状态。

9.JK 触发器的功能有置0、置1、保持和 。

10.现有容量为210×4位的SRAM2114,若要将其容量扩展成211×8位,则需要 片这样的RAM 。

二、选择题(本大题共10小题,每小题2分,共20分)在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括号内。

错选、多选或未选均无分。

11.十进制数(172)10对应的8421BCD 编码是 。

【 】A .(1111010)8421BCDB .(10111010)8421BCDC .(000101110010)8421BCD D .(101110010)8421BCD12.逻辑函数AC B A C B A Z +=),,(包含 个最小项。

【 】A .2B .3C .4D .513.设标准TTL 与非门AB Z =的电源电压是+5V ,不带负载时输出高电平电压值等于+3.6V ,输出低电平电压值等于0.3V 。

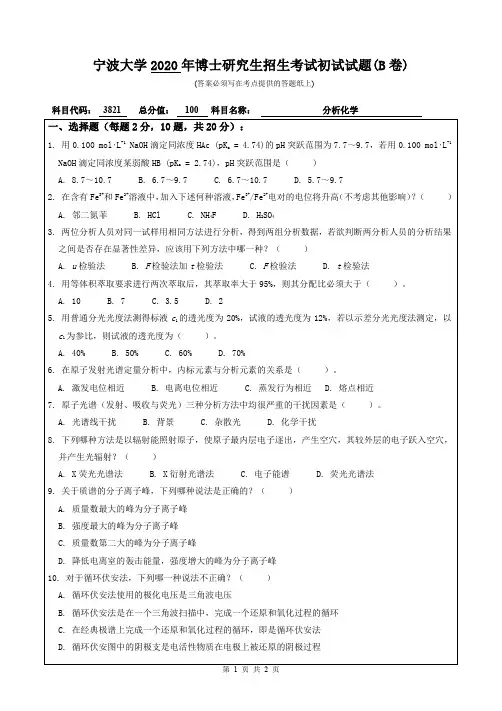

科目代码: 3809 科目名称:智能系统

1. 机器学习通常可分为指导性学习和非指导性学习,学习模型则可分为生成模型和

判别模型二类。

假定现在要完成以下的任务:

(a)函数拟合与插值;(b)聚类分析;(c)模式识别,

请简要解释以下学习模型各自属于生成模型还是判别模型,可以胜任哪种任务:(1)深度学习网络,(2)RBF网络,(3)Boltzmann机,(4)SOM网络。

(10%) 2. 如果将异或(XOR)问题推广为3输入的parity问题,要求输入和输出实现如下

真值表:

输入1 输入2 输入3 输出

0 0 0 0

0 0 1 1

0 1 0 1

0 1 1 0

1 0 0 1

1 0 1 0

1 1 0 0

1 1 1 1

请设计一个多层网络实现3-parity,并给出相应的学习算法。

(12%)

3. Hopfield网络是全相连的反馈型网络,可以用于实现“吸引子”联想记忆,如果

要使一个Hopfield网络同时记住“A”、“I”、“Y”三个字母(3x4点阵),试为其设计一个合理的结构,并给出学习算法和具体的网络权值。

(12%)

科目代码: 3809 科目名称:智能系统

科目代码: 3809 科目名称:智能系统

;

同时生成模型则以产生出能够“愚弄”判别模型使其以为真的数据为目标,即极。

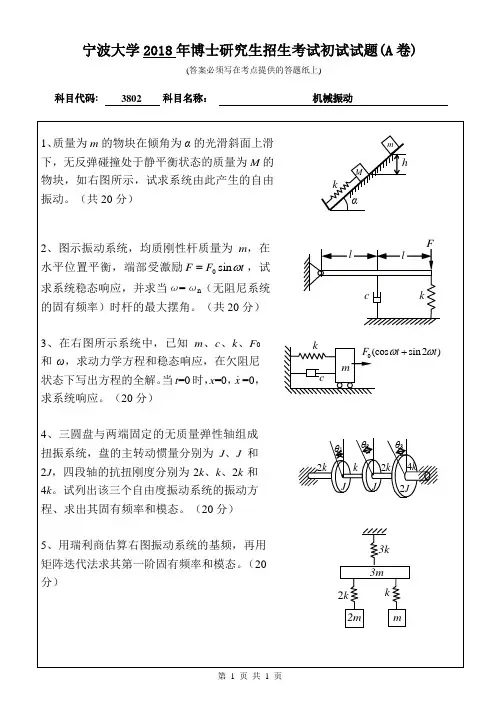

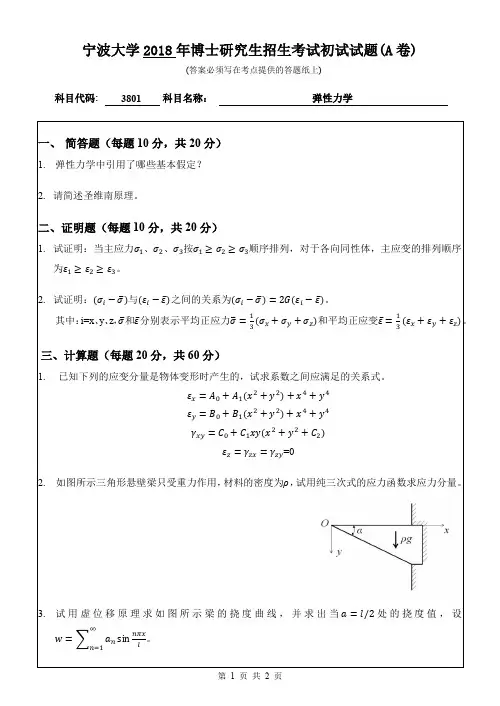

宁波大学2018年博士研究生招生考试初试试题(A卷)

(答案必须写在考点提供的答题纸上)

科目代码: 3819 科目名称:微生物学

第 1 页共1 页

宁波大学2019年博士研究生招生考试初试试题(B卷)

(答案必须写在考点提供的答题纸上)

科目代码:3819总分值:100科目名称:微生物学

一、名词解释:(每题3分,共8题,共24分)

1、MM,(—)

2、种

3、益生菌

4、子囊孢子

5、溶源细胞

6、菌相

7、鉴别培养基

8、质粒

二、简答题(每题6分,共6题,共36分)

1、写出革兰氏染色的实验过程及简单的染色机制。

2、什么叫环境样品的微生物群落结构?结合传统与现代技术研究微生物群落结构的方法有哪些?

3、什么叫溶氧浓度?在稳定供氧量情况下,在培养好氧微生物过程中其溶氧浓度的变化规律及原因。

4、简述无氧呼吸与发酵的区别。

5、如何防止菌株的衰退?

6、简述微生物遗传物质存在形式。

三、分析论述题(共3题,共40分)

1、现有一株具有一定的降胆固醇能力的乳酸菌,如何进一步通过诱变育种方法筛选一株强降解能力的突变菌株?写出实验方法及操作说明。

(12分)

2、从微生物学原理简述腌制蔬菜或发酵肉制品其亚硝酸盐的产生途径。

分别设计相关措施使产品的亚硝酸盐含量达到正常的值。

(12分)

3、论述微生物在发酵乳制品中风味物质形成中的作用。

(16分)

第1页共1页。

宁波大学2018年博士研究生招生考试初试试题(A卷)

(答案必须写在考点提供的答题纸上)

科目代码: 3820 科目名称:食品化学

第 1 页共1 页

宁波大学2019年博士研究生招生考试初试试题(A卷)

(答案必须写在考点提供的答题纸上)

科目代码:3820总分值:100科目名称:食品化学

一、名词解释(每题3分,共18分)

1.淀粉糊化

2.邻近水

3.焦糖化作用

4.亲水亲油平衡值(HLB值)

5.Esterized Starch

6.Gelation of Protein

二、简答题(每题6分,共24分)

1.为什么水果从未成熟到成熟是一个由硬变软的过程?

2.新鲜虾肉含水量高达80%左右,所含的水有哪两种存在状态?为什么虾肉被捣碎后,没有大量的水流出来?

3.为什么搅打蛋清液比搅打全蛋液,能产生更加丰富的泡沫?

4.鱼肉速冻和缓冻,哪种冻结方式对鱼肉品质的影响小?为什么?

三、论述题(共58分)

1.(10分)举2例说明酶制剂在食品加工中的应用,并说明该酶制剂在其中的功能?2.(14分)引起浓缩菠萝汁褐变的原因有哪些?如何控制浓缩菠萝汁在加工及贮藏过程中的褐变?

3.(14分)什么是吸湿等温线?吸湿等温线分为几个区?各区的水分能否被微生物利用?简述水分活度对非酶促褐变反应的影响。

4.(20分)利用所学食品化学的主要知识点,阐述食品化学理论和技术在“金华火腿”加工及贮藏过程中的作用及其对火腿肉品质影响。

(至少包含4个知识点)

第1页共1页。

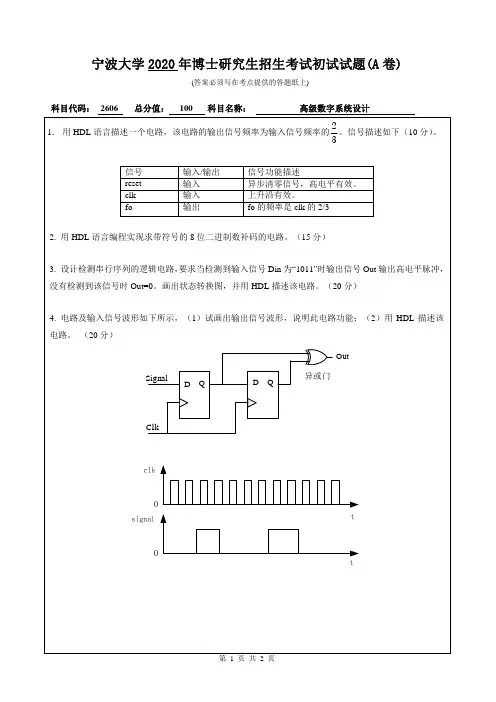

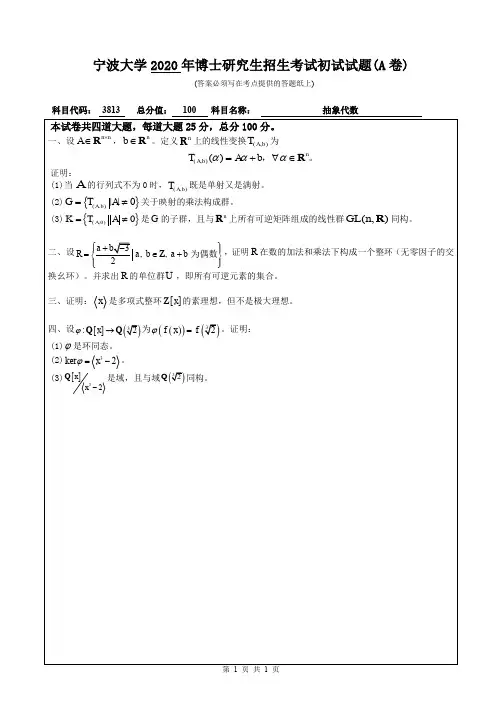

宁波大学2020年博士研究生招生考试初试试题(A卷)(答案必须写在考点提供的答题纸上)宁波大学2018年博士研究生招生考试初试试题(A卷)(答案必须写在考点提供的答题纸上)科目代码: 3820 科目名称:食品化学第 1 页共1 页考试科目:食品化学科目代码:3820适用专业:水产资源综合利用一、名字解释(40%,每题4分)1.O/W型乳浊液2.Aw3.生色基团4.过氧化值5.低甲氧基果胶(LM)6.风味阈值7.蛋白质变性作用8.淀粉老化9.食品抗氧化剂10.焦糖化作用二、问答题(60%,每题10分)1.从β-环状糊精的结构特征,说明其在食品中为何具有保色、保香、乳化的功能?2.分别说明转谷氨酰胺酶(TGase)在鱼糜制品、多聚磷酸盐在肉制品加工中的作用。

3.从蛋白质角度,说明适度热处理对食品品质的有益作用。

4.含油脂食品贮藏不当易产生哈喇味,为什么?如何防止?5.使用所学食品化学原理解释下列现象:1)热处理去除生大豆中的有害因子;2)搅打时,纯蛋清比含蛋黄的全蛋更容易起泡;3)苹果、香蕉去皮后容易褐变。

6.举二例说明食品化学理论在水产资源高值化利用中的应用。

第1页共1页考试科目: 食品化学科目代码:3820适用专业: 水产资源综合利用第1 页共1 页考试科目:食品化学科目代码:3820适用专业:水产资源综合利用一、简答题(36%,每题6分)1.与自由水相比,结合水有哪些特点?2.什么叫环状糊精?它的结构有什么特点?3.何谓淀粉老化?老化的本质是什么?4.试用所学的理论解释:1)热处理去除生大豆中的有害因子。

2)煮熟后的虾蟹壳颜色变红。

5.食品增香剂的增香机理是什么?说出二种常用的食品增香剂名称。

6.将下列英文翻译为中文:①Oxymyoglobin;②Peroxidation value;③Water activity二、问答题(64%,每题16分)1.论述游离氨基酸在肉类食品风味形成中的作用?2.说明土豆的褐变机理,并指出在土豆加工中可以通过哪些方法控制其褐变?(控制方法至少说出3点)3.火腿肉容易氧化酸败,应如何采取一些措施控制酸败的发生?(至少说出4点)4.在鱿鱼圈加工中会产生大量加工下脚料,需对其进行高值化利用,请说明研究开发思路。

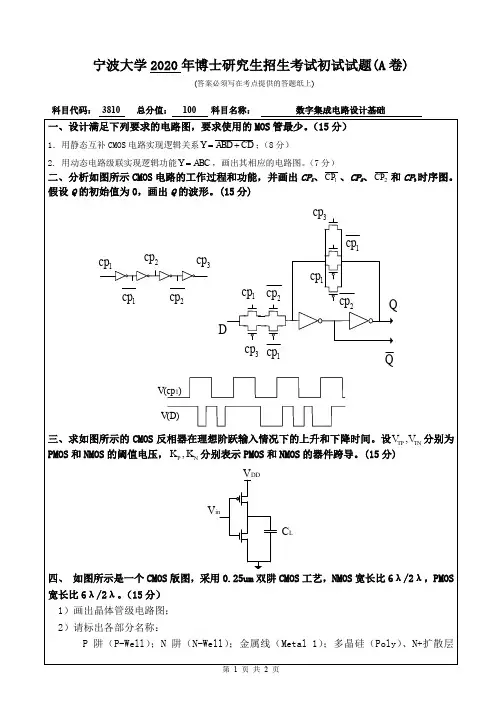

科目代码: 3810 科目名称:数字集成电路设计基础

VDD

GND IN1

IN2

IN3

IN4

OUT

科目代码: 3810 科目名称:数字集成电路设计基础

科目代码: 3810 科目名称:数字集成电路设计基础

5.说明如图5所示的静态CMOS反相器的总功耗由哪几部分组成,并列出每一项功耗的具体表达式。

(10分)

pmos

nmos

VDD

C L

图5. 静态CMOS反相器

6.分析图6所示的电路,在不同时钟CLK输入下Q0、Q1、Q2与Q3的输出状态,并将状态量

填入表1。

假设各个D触发器的初始输出状态皆为Q=0。

(10分)

图6.D触发器构成的时序逻辑电路

表1.电路输出状态表

CLK的顺

序

输入D1 Q0Q1Q2Q3

0 0 0 0 0 0

1 1

2 0

3 1

4 1

5 0

科目代码: 3810 科目名称:数字集成电路设计基础

7.试用差分串联电压开关逻辑(DCVSL)与互补传输管逻辑(CPL)实现二输入的XOR/NXOR逻

辑门,要求画出其晶体管级电路图。

(10分)

8.在图7所示电路中,已知CMOS集成施密特触发器的电源电压V DD=15V, V T+=10V,V T-=5V,

R=100KΩ, C=10μF。

试画出u c和u0的波形,并求出u0的频率以及占空比。

(10分)

图7. 施密特触发器电路

9.叙述图8所示的单管动态CMOS存储单元读与写的工作原理与工作过程。

(8分)

T C1

C2

图8. 单管动态CMOS存储单元

10.试回答下列问题:(1)在标准CMOS工艺中,NMOS衬底(阱)通常与电路中最低电位相接,

若NMOS衬底(阱)与最高电位相接,会产生什么害处? (4分)(2)MOS管有三种主要漏电流(4分)(3)试分别说明: 在65nm以下工艺,哪两种漏电流起主要作用?(4分)。