数据分配器

- 格式:doc

- 大小:68.23 KB

- 文档页数:3

数字电路-08数据选择器和数据分配器应用实验一. 实验目的1. 了解变量译码器和数据选择器的逻辑功能和具体应用。

2. 熟悉中规模组合逻辑器件功能的测试和设计方法。

二. 实验原理(1)变量译码器变量译码器有n 个输入,2n个输出,每个输出唯一地对应一组输入构成的二进制 码,当且仅当输入组合为该码时,输出呈有效电平。

中规模TTL 集成译码器有74LS139(双2输入、4输出)、74LS138(3输入、8输出)和74LS154(4输入、16输出),输出均为低电平有效,并具有低电平有效的使能控制端S —-。

变量译码器除在数字系统中起二进制译码作用外,还可实现组合逻辑函数、数据分配等功能。

74LS139的引脚图如图8-1(a )所示,片上有两个独立的2线-4线译码器,各 输出逻辑表达式为:Y ——0 =01A A S ⋅⋅、Y ——1 = 01A A S ⋅⋅、Y ——2 =01A A S ⋅⋅、Y ——3 = 01A A S ⋅⋅显然,当使能S —-为有效电平“0”时,如果译码器A 1,A 0输入的是逻辑函数的输入变量A ,B ,则Y ——i 代表了A ,B 构成的最小项m i 的反函数(最大项)。

所以,2线-4线通用译码器可附加与非门(与门)实现用标准与-或(标准或-与)表达式表示的二变量组合逻辑函数。

同理,n 线-2n 线通用译码器可实现n 变量的组合逻辑函数。

如果把译码器的使能端S 作为数据输入端,则可实现数据分配功能。

被分配的串行数字信号D i 从S 输入,当A 1,A 0为不同的二进制码时,D i 信号被分配到译码器对应的输出端Y ——i 。

比如A1A0为“11”时, D i 信号被分配到Y ——3,此时Y ——0~Y ——2输出均为高电平。

(a ) (b ) (c )图8-1 器件引脚排列(2)数据选择器数据选择器有n 位控制信号,2n 个数据输入。

每组控制码能够选择唯一的一个数据输出,类似由控制码切换的多选一开关。

数据分配器说明1系统简介ZQLS-DXFP-01和ZQLS-DXFP-02数据分配器通过和中庆联机系统或脱机系统配合完成灯屏的控制。

ZQLS-DXPF-01数据分配器用于长距离数据传输,与中庆差分接收板进行连接。

ZQLS-DXFP-02数据分配器用于短距离数据传输。

具有显示性能优异、应用结构灵活、体积小、重量轻、安装维护简便等多种特点。

可广泛应用于各种不同类型的LED灯饰亮化应用中。

2功能特点2.1结构方式灵活2.1.1ZQLS-DXFP-01和灯条之间采用隔离差分传输方式,最大传输距离100米。

2.1.2ZQLS-DXFP-02和灯条之间采用TTL电平传输方式,最大传输距离10米。

2.1.3数据分配器之间支持垂直级联和水平级联对灯屏进行扩展。

2.1.4每个扫描控制器最大控制象素点数8192点,每条灯条最大点数1024点。

2.1.5数据分配器自动识别单线单点或单线多点,无需另行设置。

2.1.6标准程序支持行控左入,每端口1024像素点方式,可通过异形处理控制任意不规则灯屏。

2.2高分辨率控制2.2.1单块数据分配器最大控制1024x8像素点2.2.2和联机系统配合最大可控制1280x1024像素点,超大屏可用多套联机一起控制2.2.3和脱机系统配合最大可控制256x256像素点2.3显示性能优异2.3.1最大256级灰度,4096级明暗对比度。

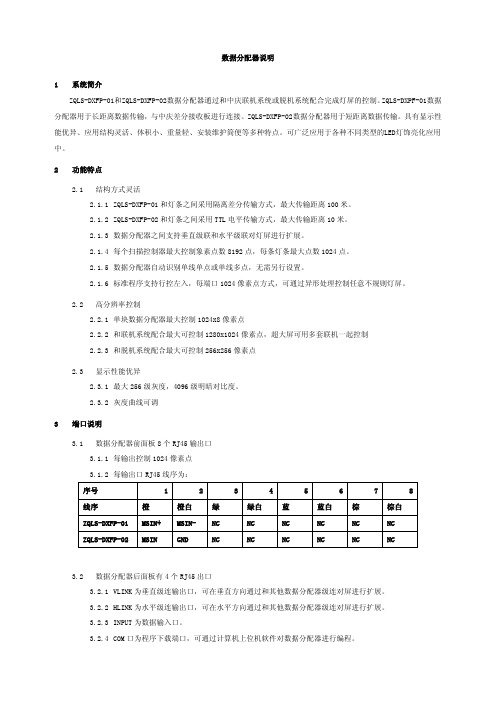

2.3.2灰度曲线可调3端口说明3.1数据分配器前面板8个RJ45输出口3.1.1每输出控制1024像素点3.1.2每输出口RJ45线序为:3.2数据分配器后面板有4个RJ45出口3.2.1VLINK为垂直级连输出口,可在垂直方向通过和其他数据分配器级连对屏进行扩展。

3.2.2HLINK为水平级连输出口,可在水平方向通过和其他数据分配器级连对屏进行扩展。

3.2.3INPUT为数据输入口。

4数据分配器BIN生成软件说明(2291 EEPROM BIN 0.1)4.1软件界面4.2软件填写说明4.2.1时钟设定4.2.1.1内部时钟,控制芯片采用的是内部时钟4.2.1.2外部时钟,选中外部时钟,点击设定,则在下面对话框填写实际使用晶振频率4.2.1.3传输分频:可选择10到30之间的任意整数值,该数值是指以芯片外部晶振频率为基准,设定数据传输速率。

数据分配是数据选择的逆过程。

根据地址信号的要求, 将一路数据分配到指定输出通道 上去的电路,称为数据分配器。

根据输出的个数不同,数据分配器可分为4 路分配器、 8 路 分配器等。

数据分配器实际上是译码器的特殊应用。

带有使能端的译码器都具有数据分配器 的功能。

一般 2-4 线译码器可作为 4 路分配器, 3-8 线译码器作为 8 路分配器, 4- 16 线译码 器作为 16 路分配器。

它们的使能端作为数据线,其扩展方法同译码器。

下图7.12 为数据分 配器示意图。

图 7.12 数据分配器

图 7.13 所示为由 3-8 译码器 74LS138 构成的 8 路数据分配器。

图中C 、B 、A 为地 址信号的输入端, Y0~Y7 为数据输出端,可从使能端G2A 、G2B 、G1 中选择一个做为 数据输入端 D 。

如 G2A 或 G2B 作为数据输入端,输出原码。

Y0 地址 输入 12

输出

Y4 ~G2A

~G2B

7

图 7.13 译码器实现数据选择器

A B C G1 1 2 3

6 4 5

Y5 Y6 Y7

Y1 Y2 Y3 11 10 9

15

14 13

1 D。

数据分配器工作原理图文分析

数据分配是数据选择的逆过程。

根据地址信号的要求,将一路数据分配到指定输出通道上去的电路,称为数据分配器。

根据输出的个数不同,数据分配器可分为4路分配器、8路分配器等。

数据分配器实际上是译码器的特殊应用。

带有使能端的译码器都具有数据分配器的功能。

一般2-4线译码器可作为4路分配器,3-8线译码器作为8路分配器,4-16线译码器作为16路分配器。

它们的使能端作为数据线,其扩展方法同译码器。

下图7.12为数据分配器示意图。

(A,B,C,………)

Y 0Y N-1

Y N-2Y 2

Y 1N 位输出

图7.12 数据分配器

图7.13所示为由3-8译码器74LS138构成的8路数据分配器。

图中C 、B 、A 为地址信号的输入端,Y0~Y7为数据输出端,可从使能端G2A 、G2B 、G1中选择一个做为数据输入端D 。

如G2A 或G2B 作为数据输入端,输出原码。

Y015Y114Y213Y312Y411Y510Y69Y7

7

A 1

B 2

C 3G16~G2A 4~G2B

5

输出

1D

地址输入

图7.13 译码器实现数据选择器。