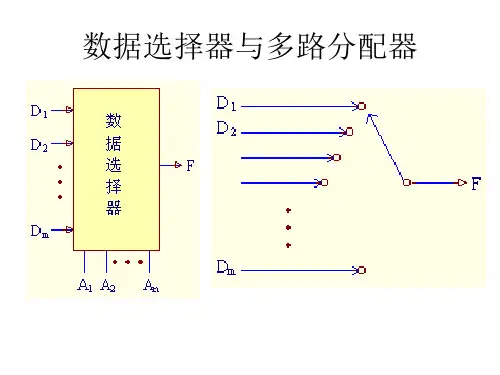

第十八讲 数据选择器与分配器

- 格式:ppt

- 大小:815.50 KB

- 文档页数:31

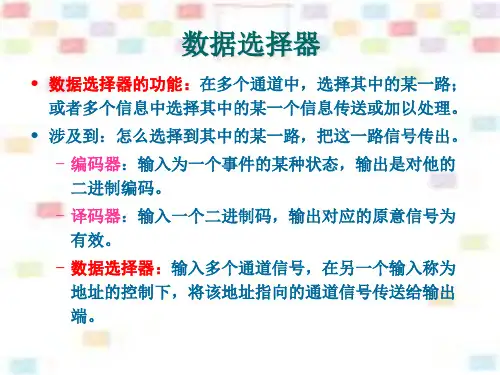

2017.0310.数字电路与系统-数据选择器分配器的理解数据选择器1.依照定义,数据选择器的核⼼在于选择⼆字上,要从⼀组输⼊信号中选择⼀个信号输出。

相当于多路到⼀路的开关,多路提供的是数据,可以假定输⼊的是D0~D7,⼋个数据,⾄于开关会打到哪个输⼊端上导致那⼀路数据输出,是有专门的控制端的。

从另⼀个⾓度来说,在光纤通信中相当于复接器,将多路低速的信号转变为⼀路⾼速的信号,怎么理解从低速到⾼速?这对于光纤传输确实是有效的,⾄少节省传输通路。

2.以视频的讲解来看,将多路低速数据变为⼀路⾼速数据就是在⼀段时间内,集中了多路数据中的所有数据。

具体怎么将多路并联数据集成⼀路串联数据?在⼀路⾼速数据的某⼀个时间段内,将时间段分成n个⼩段,每⼀⼩段时间都对应相应的低速数据信号,这样⼀来⼀路⾼速数据信号可以表征多路低速信号。

简单点讲,⼀路多速数据在单位时间内体现⼋位数据(假定输⼊的是D0~D7),⽽低速数据在单位时间内只体现⼀路数据。

从字⾯粗浅地理解来看,⼀路单位时间传送⼋位信号,⽽多路的输⼊单位时间只传输⼀位信号,明显⼀路的传输速度是快的,⽽D0~D7传输速度是慢的,速度体现在单位时间能够传输数据的数⽬上。

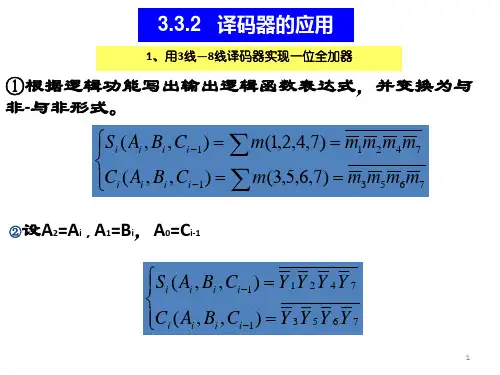

从后⾯的讲解看,数据选择器是实现了逻辑函数表达式,单⼑多掷开关在控制端的指挥下,将多路信号整合在了⼀起(多个变量相与,再进⾏下⼀步运算)多路数据选择器的基本思想就是,将多路信号整合到⼀路信号上,但是怎么整合需要有控制端,控制端能控制的选择的数⽬必须包含所有的输⼊端的数⽬,如果假定的输⼊端数⽬是D0~D7,⼋个端⼝,那么控制端必须是3位⼆进制。

3.双四选⼀的74153数据选择器,它实际上是共⽤了两个地址端(也就是控制端)。

我可以理解为两个四选⼀数据选择器集合在⼀起,“双”代表有两个四选⼀数据选择器。

从这⾥开始讲解实际的数据选择器模块。

双四选⼀74153数据选择器数据输⼊端哪⼀个被送出去,是由地址端决定的,同时在逻辑图中配备有⼀个使能端E N,这个使能端决定了数据选择器输出还是不输出,enable。

2017.0313.数字电路与系统-数据选择器分配器的理解数据分配器1.数据分配器是数据选择器的逆过程。

2.1-4路的数据分配器,这是个设计组合电路的过程。

⾸先,我们先明确1-4路的数据分配器的功能:⼀路串⾏输⼊数据,输出四路数据。

控制信号(地址信号)地址信号是和⼀路串⾏输⼊数据连在⼀起构成函数表达式么?数据⽐较器1.顾名思义,这个逻辑电路就是⽤来进⾏两个数值间的⽐较的,⽐较的结果有三种,⼤于,⼩于,等于。

每次⽐较两个数值时,总会在这三种情况中出现⼀种。

这说明逻辑电路的设计过程中要注意的问题,每⼀个逻辑电路都是由不同的输⼊变量和不同的输出变量组成,然后要明确输⼊变量有哪⼏个,输出变量有哪⼏个,同时,每⼀个输出变量的函数表达式都是由所有输⼊变量组成的,⽽这些逻辑函数的表达式很多时候就是之前常见的逻辑功能,同或,异或.......最常见的写逻辑函数表达式的⽅法就是依照真值表写标准的与或式(最⼩项表达式)。

这⾥还要说明的⼀点就是,当有多个输出时,在画逻辑图是需要共⽤所有输⼊,所有的输出在同⼀张逻辑图上表⽰出来。

2.前述的是两个⼀位的数值之间的⽐较,每⼀个都是取0或1。

接着⼜谈论到两个⼆位的数值之间的⽐较,所有的输⼊数据均是⼆进制的0或1,在计算机⾥,所有的数据均是⽤⼆进制来表⽰的,⽆论是⽂字,图⽚还是数值均是⽤⼆进制代码来表⽰的,这⾥进⾏数制上的⽐较,⼀定是计算机将⼗进制的数字转变成了⼆进制,所有的数据输⼊计算机时都要被转化成⼆进制的编码,区别在于数值被转化后,是具有权位的⼆进制数码。

3.⼀位的数值⽐较器是两个⼀位的数值在⽐较,⼆位的数值⽐较器是两个⼆位的数值在⽐较,以此类推,随着位数不断的增加,再通过真值表的⽅法来⽐较显得很⿇烦。

第⼆次理解数据⽐较器和校验器数据⽐较器1.数值⽐较器最常见的是对两个数值A和B⼤⼩进⾏⽐较,但是我们是不清楚A,B的具体数值,或者说,任意两个数值间进⾏⽐较,⽐较过后会产⽣三种结果。