- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字逻辑

College of Computer Science, SWPU

2输入 位多路复用器 输入4位多路复用器 输入 74x157真值表 真值表 1A 输入 2A 3A 4A G_L 1 0 0 S X 0 1 输出 1Y 2Y 3Y 4Y 0 0 0 1

1A 2A 3A 4A 1B 2B 3B 4B

思考:利用74x151实现逻辑函数 思考:利用74x151实现逻辑函数 74x151 F = Σ(W,X,Y,Z)(0,1,3,7,9,13,14) 降维: 降维:由4维 3维

WX YZ Y WX 00 01 11 10 0 1 1 Z 0 Z Z Z’ Z 0

00 01 11 10 00 01 11 10

数字逻辑

Y Y

College of Computer Science, SWPU

扩展数据选择器

扩展数据输入端的数目 如何实现32输入 如何实现32输入,1位多路复用器? 输入, 位多路复用器? 数据输入由8 数据输入由 32,需4片 , 片

EN A B C D0 D7

如何控制选择输入端? 如何控制选择输入端? —— 分为:高位+低位 分为:高位+ 高位+ 高位+译码器进行片选 低位接到每片的C,B,A 低位接到每片的 4片输出用或门得最终输出 片输出用或门得最终输出

1 1 1 1 1 1 1

数字逻辑

College of Computer Science, SWPU

F = Σ(W,X,Y,Z)(0,1,3,7,9,13,14)

74x151

利用74x151实现 利用74x151实现 74x151

说明:用具有n 说明:用具有n位地址 WX 输入端的多路复用器, 输入端的多路复用器, 00 01 11 10 Y 0 2 6 4 可以产生任何形式的输 1 0 Z Z 0 1 3 7 入变量数不大于n+1 5 n+1的 入变量数不大于n+1的 1 Z Z Z’ 0 组合逻辑函数。 组合逻辑函数。 VCC

College of Computer Science, SWPU

数据分配器

真值表

A 0 0 0 0 1 1 1 1

数字逻辑

B 0 0 1 1 0 0 1 1

D 0 1 0 1 0 1 0 1

W0 W1 W2 W3 0 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 1

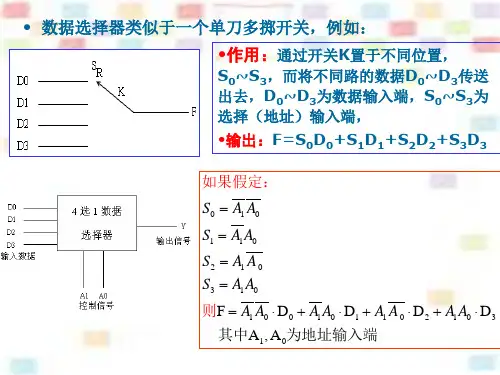

又称多路开关、多路复用器(缩写:mux) 又称多路开关、多路复用器(缩写:mux) 在选择控制信号的作用下, 在选择控制信号的作用下, 从多个输入数据中 选择其中一个作为输出。 选择其中一个作为输出。

Enable 使能 使能 Select 选择 选择 EN SEL D0 n个1位数据源 个b位数据源 位数据源 Dn-1

数字逻辑

College of Computer Science, SWPU

Y = ∑EN ⋅ mi ⋅ Di

i =0

n−1

Y

数据输出( 位 数据输出( 位 数据输出( 1位) 数据输出(b位)

8输入 位多路复用器 输入1位多路复用器 输入 74x151真值表 真值表 A B C EN_L C B A 1 0 0 0 0 0 0 0 0 X 0 0 0 0 1 1 1 1 X 0 0 1 1 0 0 1 1 X 0 1 0 1 0 1 0 1 Y 0 D0 D1 D2 D3 D4 D5 D6 D7 Y_L 1 D0’ D1’ D2’ D3’ D4’ D5’ D6’ D7’

College of Computer Science, SWPU

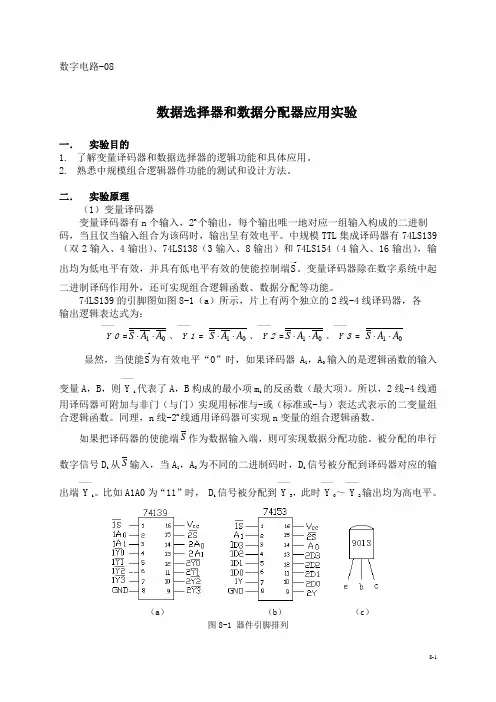

利用带使能端的二进制译码器作为多路分配器 —— 利用使能端作为数据输入端

74x138 数据输入 SRC EN_L EN_L 数据输入 SRC 地址 选择 DSTSEL0 DSTSEL1 DSTSEL2 G1 G2A G2B A B C

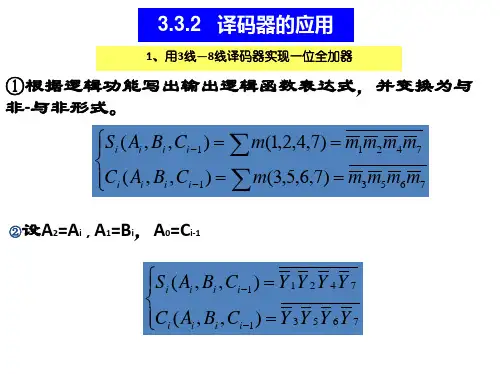

(2)真值表法 )

mi A B C 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 L 0 1 1 0 0 0 1 1

求Di的 方法

m0 m1

C=1时L=1, 时 , 故D0=C C=0时L=1, 时 , 故D1=C L=0,故 , D2=0 L=1,故 , D3=1

数据选择器(multiplexer) 数据选择器(multiplexer)

数据选择器的应用 数据选择器的应用 数据选择器的应用很广,典型应用有以下几个 方面: 作数据选择,以实现多路信号分时传送。 作数据选择,以实现多路信号分时传送。 实现组合逻辑函数。 实现组合逻辑函数。 在数据传输时实现并—串转换。 在数据传输时实现并 串转换。 串转换 产生序列信号。 产生序列信号。

数字逻辑

College of Computer Science, SWPU

数据选择器实现逻辑函数

基本原理

数据选择器的主要特点: 数据选择器的主要特点: (1)具有标准与或表达式的形式。即:Y = 具有标准与或表达式的形式。 (2)提供了地址变量的全部最小项。 提供了地址变量的全部最小项。

2 n −1 i =0 =0

比较L和Y,得:

D0 = C、D1 = C 、D2 = 0、D3 = 1

数字逻辑

College of Computer Science, SWPU

4

L

4

Y

1 2

74LS153 A1 A0 ST

D0 D1 D2 D3

画连线图

C C 0 1

数字逻辑

A B 0

College of Computer Science, SWPU

College of Computer Science, SWPU

3

(1)公式法 )

函数的标准与或表达式:

3

L = A B C + A BC + AB = m0C + m1C + m2 ⋅ 0 + m3 ⋅ 1

4选1数据选择器输出信号的表达式:

求 Di

Y = m0 D0 + m1 D1 + m2 D2 + m3 D3

数字逻辑

基本步骤

逻辑函数

1 n个地址变量的数 据选择器,不需要 增加门电路,最多 可实现n+1个变量 的函数。

L = A B C + A BC + AB

1 3个变量,选用4 选1数据选择器。

确定数据选择器

2

选用74LS153 选用

2 74LS153有两个 地址变量。

确定地址变量

数字逻辑

A1=A、A0=B 、

m0

0000 0001 0010 0011 0100 0101 0110

m1

D1=D

m5

D5=1

m2

D2=1

m6

D6=1

数字逻辑 0111

m3

D3=0

m7

College of Computer0 Science, SWPU 1111

D7=0

④画连线图

L Y 74LS151 D0 D1 D2 D3 D4 D5 D6 D7 A2 A1 A0 EN

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

DST0_L

DST7_L

利用74x139实现2 利用74x139实现2位4输出多路分配器 74x139实现

数字逻辑

College of Computer Science, SWPU

数据选择器(multiplexer) 数据选择器(multiplexer)

数字逻辑

Y Y

College of Computer Science, SWPU

用双4选 数据选择器构成 数据选择器构成8选 数据选择器 用双 选1数据选择器构成 选1数据选择器

A0 A1 A2 D0 D1 D2 D3 Y D4 D5 D6 D7

数字逻辑

College of Computer Science, SWPU

m2 m3

数字逻辑

College of Computer Science, SWPU

例

用数据选择器实现函数:

L ( A, B , C , D ) = ∑ m ( 0,3, 4,5,9,10 ,11,12 ,13 )

①选用8选1数据选择器74LS151 ②设A2=A、A1=B、A0=C ③求Di

ABCD L 1 0 0 1 1 1 0 0 D0=D’ m4 ABCD 1000 1001 1010 1011 1100 1101 1110 L 0 1 1 1 1 1 0 D4=D

Y X W

EN A B C D0 D1 D2 D3 D4 D5 D6 D7 Y Y

F

Z

数字逻辑

College of Computer Science, SWPU

D D 1 0 D 1 1 0

数字逻辑

A B C 0

College of Computer Science, SWPU

数据选择器实现逻辑函数

例:试用 选1MUX实现逻辑函数: 试用8选 实现逻辑函数: 实现逻辑函数

F = AB + AB + C

数字逻辑

College of Computer Science, SWPU

∑Dm

i

i

(3)一般情况下,Di可以当作一个变量处理。 一般情况下, 可以当作一个变量处理。 因为任何组合逻辑函数总可以用最小项之和 的标准形式构成。所以,利用数据选择器的输入 的标准形式构成。所以, Di来选择地址变量组成的最小项mi,可以实现任 何所需的组合逻辑函数。 何所需的组合逻辑函数。

College of Computer Science, SWPU