数据选择器数据分配器

- 格式:ppt

- 大小:393.50 KB

- 文档页数:13

数字电路-08数据选择器和数据分配器应用实验一. 实验目的1. 了解变量译码器和数据选择器的逻辑功能和具体应用。

2. 熟悉中规模组合逻辑器件功能的测试和设计方法。

二. 实验原理(1)变量译码器变量译码器有n 个输入,2n个输出,每个输出唯一地对应一组输入构成的二进制 码,当且仅当输入组合为该码时,输出呈有效电平。

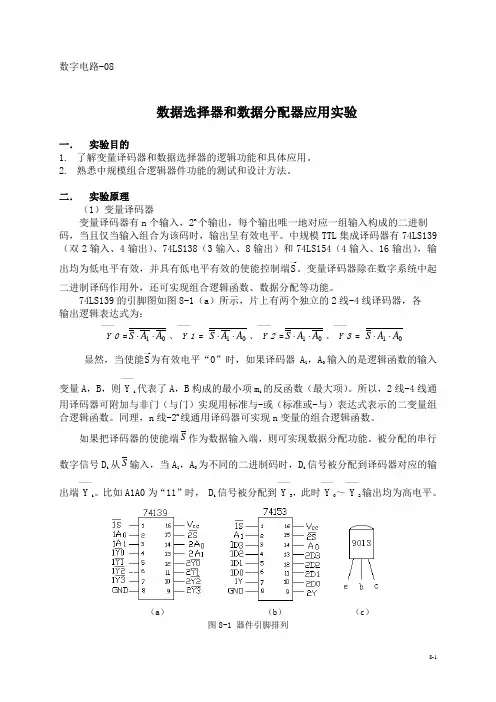

中规模TTL 集成译码器有74LS139(双2输入、4输出)、74LS138(3输入、8输出)和74LS154(4输入、16输出),输出均为低电平有效,并具有低电平有效的使能控制端S —-。

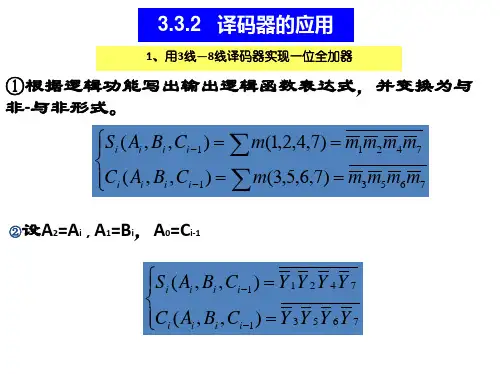

变量译码器除在数字系统中起二进制译码作用外,还可实现组合逻辑函数、数据分配等功能。

74LS139的引脚图如图8-1(a )所示,片上有两个独立的2线-4线译码器,各 输出逻辑表达式为:Y ——0 =01A A S ⋅⋅、Y ——1 = 01A A S ⋅⋅、Y ——2 =01A A S ⋅⋅、Y ——3 = 01A A S ⋅⋅显然,当使能S —-为有效电平“0”时,如果译码器A 1,A 0输入的是逻辑函数的输入变量A ,B ,则Y ——i 代表了A ,B 构成的最小项m i 的反函数(最大项)。

所以,2线-4线通用译码器可附加与非门(与门)实现用标准与-或(标准或-与)表达式表示的二变量组合逻辑函数。

同理,n 线-2n 线通用译码器可实现n 变量的组合逻辑函数。

如果把译码器的使能端S 作为数据输入端,则可实现数据分配功能。

被分配的串行数字信号D i 从S 输入,当A 1,A 0为不同的二进制码时,D i 信号被分配到译码器对应的输出端Y ——i 。

比如A1A0为“11”时, D i 信号被分配到Y ——3,此时Y ——0~Y ——2输出均为高电平。

(a ) (b ) (c )图8-1 器件引脚排列(2)数据选择器数据选择器有n 位控制信号,2n 个数据输入。

每组控制码能够选择唯一的一个数据输出,类似由控制码切换的多选一开关。

数据选择器与数据分配器的设计与仿真数据选择器与数据分配器的设计与仿真摘要:基于量⼦元胞⾃动机的双稳态特性和数字电路,本⽂探讨了4位数据选择器和4位数据分配器的设计⽅法,并利⽤QCADesigner仿真验证了其电路设计的正确性,对以后8位、16位或更⾼位的数据选择器与数据分配器具有⼀定的借鉴意义。

关键词:量⼦元胞⾃动机、数据选择器和数据分配器、QCADesigner仿真1、引⾔有研究认为,当电⼦器件的尺⼨达到70 nm 时, 由于功率耗散和相互连接等问题使得基于传统CMOS 技术的器件尺⼨的进⼀步减⼩变得不太可能[1],这就需要发展⼀种不同于传统CMOS 的器件技术来使电⼦器件能继续朝纳⽶级⽅向发展。

近年来,有些学者提出量⼦元胞⾃动机(Quantum Cellular Automaton,QCA)的结构,它通过电⼦在量⼦元胞⾃动机上占据的位置来携带⼆进制信息⽽不是通过传统的电流开关来表⽰⼆进制信息。

量⼦细胞⾃动机的结构, 在⽤分⼦实现时, 其特征尺⼨仅为⼏纳⽶,具有低功耗、⾼集成度和⽆引线集成等优点, 将是新⼀代的电⼦元件之⼀。

然⽽,基于QCA实现数字逻辑系统,均需要展开⼤量的研究⼯作。

作为基于QCA数字逻辑系统的基础,需要有完整的逻辑单元库。

迄今,虽然有⼈提出了各种加法器[2-4]、乘法器[5]和其他电路[6]的设计,但是,数据选择器和数据分配器的设计还缺乏研究。

本⽂结合QCA和数字电路相关知识和化简思想的设计了数据分配器和数据选择器,并利⽤QCADesigner仿真验证了其电路设计的正确性。

此外,此电路设计中采⽤基本QCA器件组合和相同逻辑功能电路合并的思想,具有较强的普适性,对以后的电路设计也有⼀定的借鉴意义。

2、量⼦元胞⾃动机的基本元素QCA是由基本的逻辑器件组成的,这些基本量⼦器件主要有含有两个静电⼦的标准元胞和旋转元胞,每个元胞通过内部电⼦所处的位置定义它的极性,元胞之间极性的传递或改变是依靠两元胞间电⼦的库仑作⽤和元胞内电⼦的隧穿作⽤,每个元胞中的电⼦被⾼度极化,电⼦云密度沿元胞两个垂直的对⾓分布中的⼀个⽅向分布,⼀个元胞的极化能引起临近元胞的极化,从⽽实现数据的传递。

实验四_数据选择器和数据分配器实验四数据选择器和数据分配器⼀、实验⽬的1. 掌握数据选择器和数据分配器的⼯作原理和特点;2. 熟悉数据选择器、数据分配器的管脚排列和逻辑功能;3. 熟悉数据选择器、分配器的扩展⽅法。

⼆、预习要求1. 复习有关数据选择器和数据分配器的章节;2. 按实验内容的要求,做好实验预习报告,画好实验线路图和记录表格。

三、实验设备与器件1. TDN-DS 数字逻辑电路/数字系统设计教学实验系统。

2. 74LS151和74LS138各⼀⽚。

3. 数字万⽤表,连接导线若⼲。

四、实验的原理数据选择器⼜叫多路开关,其基本功能相当于多位开关,其集成电路有“四选⼀”、“⼋选⼀”、“⼗六选⼀”等多种类型。

我们以“⼋选⼀”数据选择器74LS151为例进⾏实验论证。

数据选择器的应⽤很⼴,它可实现任何形式的逻辑函数、将并⾏码变成串⾏码和组成数码⽐较器等。

例如在计算机数字控制装置和数字通信系统中,往往要求将并⾏形式的数据转换成串⾏的形式。

若⽤数据选择器就能很容易完成这种转换。

只要将欲变换的并⾏码送到数据选择器的信号输⼊端,使组件的控制信号按⼀定的编码(如⼆进制码)顺序依次变化,则可在输出端获得串⾏码输出,如图1所⽰。

CB ASQ 0Q 1Q 2并⾏数据输⼊选通D 7D 6D 5D 4D 3D 2D 1D 0串⾏数据输出Y⼆进制计数器数据选择器图4-1 变并⾏码为串⾏码的⽰意图数据分配器实际上其逻辑功能与数据选择器相反,它的功能是使数据由⼀个输⼊端向多个输出端中的某⼀个进⾏传送,它的电路结构类似于译码器,所不同的是多了⼀个输⼊端。

若数据分配器的输⼊端恒为1,它就成了译码器。

实际上,我们可以⽤译码器集成电路充当数据分配器。

例如,⽤2-4线译码器充当四路数据分配器,3-8线译码器充当⼋路数据分配器。

具体是将译码器的译码输出充当数据分配器输出,⽽将译码器的使能输⼊充当数据分配器的数据输⼊。

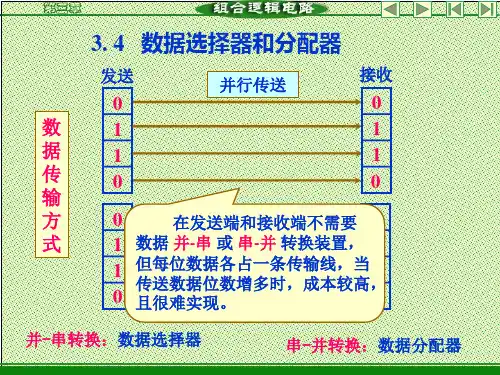

数据选择器和分配器组合起来,可实现多路分配,即在⼀条信号线上传输多路信号,图4-2即为多路信号的⽰意图。

2017.0313.数字电路与系统-数据选择器分配器的理解数据分配器1.数据分配器是数据选择器的逆过程。

2.1-4路的数据分配器,这是个设计组合电路的过程。

⾸先,我们先明确1-4路的数据分配器的功能:⼀路串⾏输⼊数据,输出四路数据。

控制信号(地址信号)地址信号是和⼀路串⾏输⼊数据连在⼀起构成函数表达式么?数据⽐较器1.顾名思义,这个逻辑电路就是⽤来进⾏两个数值间的⽐较的,⽐较的结果有三种,⼤于,⼩于,等于。

每次⽐较两个数值时,总会在这三种情况中出现⼀种。

这说明逻辑电路的设计过程中要注意的问题,每⼀个逻辑电路都是由不同的输⼊变量和不同的输出变量组成,然后要明确输⼊变量有哪⼏个,输出变量有哪⼏个,同时,每⼀个输出变量的函数表达式都是由所有输⼊变量组成的,⽽这些逻辑函数的表达式很多时候就是之前常见的逻辑功能,同或,异或.......最常见的写逻辑函数表达式的⽅法就是依照真值表写标准的与或式(最⼩项表达式)。

这⾥还要说明的⼀点就是,当有多个输出时,在画逻辑图是需要共⽤所有输⼊,所有的输出在同⼀张逻辑图上表⽰出来。

2.前述的是两个⼀位的数值之间的⽐较,每⼀个都是取0或1。

接着⼜谈论到两个⼆位的数值之间的⽐较,所有的输⼊数据均是⼆进制的0或1,在计算机⾥,所有的数据均是⽤⼆进制来表⽰的,⽆论是⽂字,图⽚还是数值均是⽤⼆进制代码来表⽰的,这⾥进⾏数制上的⽐较,⼀定是计算机将⼗进制的数字转变成了⼆进制,所有的数据输⼊计算机时都要被转化成⼆进制的编码,区别在于数值被转化后,是具有权位的⼆进制数码。

3.⼀位的数值⽐较器是两个⼀位的数值在⽐较,⼆位的数值⽐较器是两个⼆位的数值在⽐较,以此类推,随着位数不断的增加,再通过真值表的⽅法来⽐较显得很⿇烦。

第⼆次理解数据⽐较器和校验器数据⽐较器1.数值⽐较器最常见的是对两个数值A和B⼤⼩进⾏⽐较,但是我们是不清楚A,B的具体数值,或者说,任意两个数值间进⾏⽐较,⽐较过后会产⽣三种结果。