AVR单片机指令集--机器码与助记符

- 格式:doc

- 大小:118.50 KB

- 文档页数:2

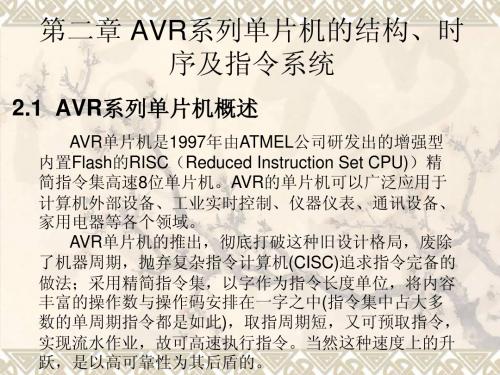

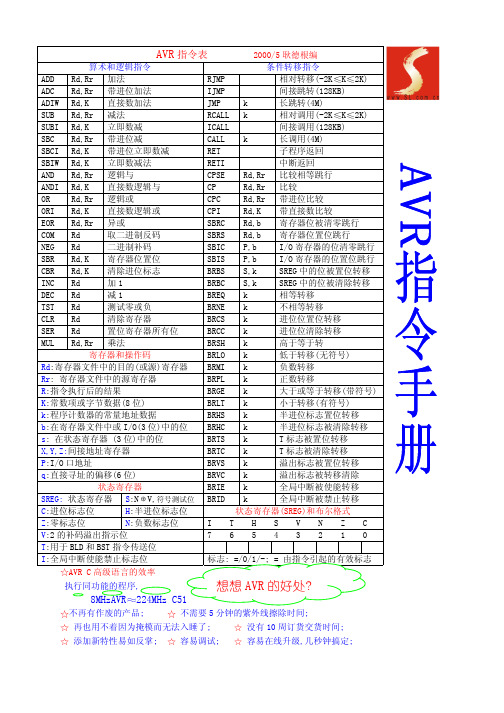

avr单片机指令集AVR单片机指令集指令集概述指令,操作数,说明,操作标志# ,时钟数算数和逻辑指令ADD Rd, Rr 无进位加法Rd ← Rd + Rr Z,C,N,V,H 1ADC Rd, Rr 带进位加法Rd ← Rd + Rr + C Z,C,N,V,H 1ADIW Rdl,K 立即数与字相加Rdh:Rdl ← Rdh:Rdl + K Z,C,N,V,S 2SUB Rd, Rr 无进位减法Rd ← Rd - Rr Z,C,N,V,H 1SUBI Rd, K 减立即数Rd ← Rd - K Z,C,N,V,H 1SBC Rd, Rr 带进位减法Rd ← Rd - Rr - C Z,C,N,V,H 1SBCI Rd, K 带进位减立即数Rd ← Rd - K - C Z,C,N,V,H 1SBIW Rdl,K 从字中减立即数Rdh:Rdl ← Rdh:Rdl - K Z,C,N,V,S 2 AND Rd, Rr 逻辑与Rd ← Rd ? Rr Z,N,V 1ANDI Rd, K 与立即数的逻辑与操作Rd ← Rd ? K Z,N,V 1OR Rd, Rr 逻辑或Rd ← Rd v Rr Z,N,V 1ORI Rd, K 与立即数的逻辑或操作Rd ← Rd v K Z,N,V 1EOR Rd, Rr 异或Rd ← Rd ⊕ Rr Z,N,V 1COM Rd 1 的补码Rd ← 0xFF ? Rd Z,C,N,V 1NEG Rd 2 的补码Rd ← 0x00 ? Rd Z,C,N,V,H 1SBR Rd,K 设置寄存器的位Rd ← Rd v K Z,N,V 1CBR Rd,K 寄存器位清零Rd ← Rd ? (0xFF - K) Z,N,V 1INC Rd 加一操作Rd ← Rd + 1 Z,N,V 1DEC Rd 减一操作Rd ← Rd ? 1 Z,N,V 1TST Rd 测试是否为零或负Rd ← Rd ? Rd Z,N,V 1CLR Rd 寄存器清零Rd ← Rd ⊕ Rd Z,N,V 1SER Rd 寄存器置位Rd ← 0xFF None 1MUL Rd, Rr 无符号数乘法R1:R0 ← Rd x Rr Z,C 2MULS Rd, Rr 有符号数乘法R1:R0 ← Rd x Rr Z,C 2MULSU Rd, Rr 有符号数与无符号数乘法R1:R0 ← Rd x Rr Z,C 2 FMUL Rd, Rr 无符号小数乘法R1:R0 ← (Rd x Rr) << 1 Z,C 2FMULS Rd, Rr 有符号小数乘法R1:R0 ← (Rd x Rr) << 1 Z,C 2FMULSU Rd, Rr 有符号小数与无符号小数乘法R1:R0 ← (Rd x Rr) << 1 Z,C 2跳转指令RJMP k 相对跳转PC ← PC + k + 1 无2IJMP 间接跳转到(Z) PC ← Z 无2RCALL k 相对子程序调用PC ← PC + k + 1 无3ICALL 间接调用(Z) PC ← Z 无3RET 子程序返回PC ← STACK 无4RETI 中断返回PC ← STACK I 4CPSE Rd,Rr 比较,相等则跳过下一条指令if (Rd = Rr) PC ← PC + 2 or 3 无1 /2 / 3CP Rd,Rr 比较Rd ? Rr Z, N,V,C,H 1CPC Rd,Rr 带进位比较Rd ? Rr ? C Z, N,V,C,H 1CPI Rd,K 与立即数比较Rd ? K Z, N,V,C,H 1SBRC Rr, b 寄存器位为"0” 则跳过下一条指令if (Rr(b)=0) PC ← PC + 2 or 3 无1 / 2 / 3SBRS Rr, b 寄存器位为"1” 则跳过下一条指令if (Rr(b)=1) PC ← PC + 2 or 3 无1 / 2 / 3SBIC P, b I/O 寄存器位为"0” 则跳过下一条指令if (P(b)=0) PC ← PC + 2 or 3 无1 / 2 / 3SBIS P, b I/O 寄存器位为"1” 则跳过下一条指令if (P(b)=1) PC ← PC + 2 or 3 无1 / 2 / 3BRBS s, k 状态寄存器位为"1” 则跳过下一条指令if (SREG(s) = 1) then PC←PC+k + 1 无1 / 2BRBC s, k 状态寄存器位为"0” 则跳过下一条指令if (SREG(s) =0) then PC←PC+k + 1 无1 / 2BREQ k 相等则跳转if (Z = 1) then PC ← PC + k + 1 无1 / 2BRNE k 不相等则跳转if (Z = 0) then PC ← PC + k + 1 无1 / 2 BRCS k 进位位为"1” 则跳转if (C = 1) then PC ← PC + k + 1 无1 / 2 BRCC k 进位位为"0” 则跳转if (C = 0) then PC ← PC + k + 1 无1 / 2 BRSH k 大于或等于则跳转if (C = 0) then PC ← PC + k + 1 无1 / 2 BRLO k 小于则跳转if (C = 1) then PC ← PC + k + 1 无1 / 2BRMI k 负则跳转if (N = 1) then PC ← PC + k + 1 无1 / 2BRPL k 正则跳转if (N = 0) then PC ← PC + k + 1 无1 / 2BRGE k 有符号数大于或等于则跳转if (N ⊕ V= 0) then PC ← PC + k + 1 无1 / 2BRLT k 有符号数负则跳转if (N ⊕ V= 1) then PC ← PC + k + 1 无1 / 2 BRHS k 半进位位为"1” 则跳转if (H = 1) then PC ← PC + k + 1 无1 / 2 BRHC k 半进位位为"0” 则跳转if (H = 0) then PC ← PC + k + 1 无1 / 2 BRTS k T 为"1” 则跳转if (T = 1) then PC ← PC + k + 1 无1 / 2 BRTC k T 为"0” 则跳转if (T = 0) then PC ← PC + k + 1 无1 / 2 BRVS k 溢出标志为"1” 则跳转if (V = 1) then PC ← PC + k + 1 无1 / 2 BRVC k 溢出标志为"0” 则跳转if (V = 0) then PC ← PC + k + 1 无1 / 2 274 ATmega8(L)2486N–AVR–07/04指令操作数说明操作标志# 时钟数BRIE k 中断使能再跳转if ( I = 1) then PC ← PC + k + 1 无1 / 2 BRID k 中断禁用再跳转if ( I = 0) then PC ← PC + k + 1 无1 / 2数据传送指令MOV Rd, Rr 寄存器间复制Rd ← Rr 无1MOVW Rd, Rr 复制寄存器字Rd+1:Rd ← Rr+1:Rr 无1LDI Rd, K 加载立即数Rd ← K 无1LD Rd, X 加载间接寻址数据Rd ← (X) 无2LD Rd, X+ 加载间接寻址数据,然后地址加一Rd ← (X), X ← X + 1 无2 LD Rd, - X 地址减一后加载间接寻址数据X ← X - 1, Rd ← (X) 无2LD Rd, Y 加载间接寻址数据Rd ← (Y) 无2LD Rd, Y+ 加载间接寻址数据,然后地址加一Rd ← (Y), Y ← Y + 1 无2 LD Rd, - Y 地址减一后加载间接寻址数据Y ← Y - 1, Rd ← (Y) 无2LDD Rd,Y+q 加载带偏移量的间接寻址数据Rd ← (Y + q) 无2LD Rd, Z 加载间接寻址数据Rd ← (Z) 无2LD Rd, Z+ 加载间接寻址数据,然后地址加一Rd ← (Z), Z ← Z+1 无2LD Rd, -Z 地址减一后加载间接寻址数据Z ← Z - 1, Rd ← (Z) 无2LDD Rd, Z+q 加载带偏移量的间接寻址数据Rd ← (Z + q) 无2 LDS Rd, k 从SRAM 加载数据Rd ← (k) 无2ST X, Rr 以间接寻址方式存储数据(X) ← Rr 无2ST X+, Rr 以间接寻址方式存储数据,然后地址加一(X) ← Rr, X ← X + 1 无2ST - X, Rr 地址减一后以间接寻址方式存储数据X ← X - 1, (X) ← Rr 无2 ST Y, Rr 加载间接寻址数据(Y) ← Rr 无2ST Y+, Rr 加载间接寻址数据,然后地址加一(Y) ← Rr, Y ← Y + 1 无2ST - Y, Rr 地址减一后加载间接寻址数据Y ← Y - 1, (Y) ← Rr 无2 STD Y+q,Rr 加载带偏移量的间接寻址数据(Y + q) ← Rr 无2ST Z, Rr 加载间接寻址数据(Z) ← Rr 无2ST Z+, Rr 加载间接寻址数据,然后地址加一(Z) ← Rr, Z ← Z + 1 无2ST -Z, Rr 地址减一后加载间接寻址数据Z ← Z - 1, (Z) ← Rr无2 STD Z+q,Rr 加载带偏移量的间接寻址数据(Z + q) ← Rr 无2STS k, Rr 从SRAM 加载数据(k) ← Rr 无2LPM 加载程序空间的数据R0 ← (Z) 无3LPM Rd, Z 加载程序空间的数据Rd ← (Z) 无3LPM Rd, Z+ 加载程序空间的数据,然后地址加一Rd ← (Z), Z ← Z+1 无3 SPM 保存程序空间的数据(Z) ← R1:R0 无-IN Rd, P 从I/O 端口读数据Rd ← P 无1OUT P, Rr 输出端口P ← R r 无1PUSH Rr 将寄存器推入堆栈STACK ← Rr 无2POP Rd 将寄存器从堆栈中弹出Rd ← STACK 无2位和位测试指令SBI P,b I/O 寄存器位置位I/O(P,b) ← 1 无2CBI P,b I/O 寄存器位清零I/O(P,b) ← 0 无2LSL Rd 逻辑左移Rd(n+1) ← Rd(n), Rd(0) ← 0 Z,C,N,V 1LSR Rd 逻辑右移Rd(n) ← Rd(n+1), Rd(7) ← 0 Z,C,N,V 1ROL Rd 带进位循环左移Rd(0)←C,Rd(n+1)← Rd(n),C←Rd(7) Z,C,N,V 1ROR Rd 带进位循环右移Rd(7)←C,Rd(n)← Rd(n+1),C←Rd(0) Z,C,N,V 1 ASR Rd 算术右移Rd(n) ← Rd(n+1), n=0..6 Z,C,N,V 1 SWAP Rd 高低半字节交换Rd(3..0)←Rd(7..4),Rd(7..4)←Rd(3..0) 无1 BSET s 标志置位SREG(s) ← 1 SREG(s) 1BCLR s 标志清零SREG(s) ← 0 SREG(s) 1BST Rr, b 从寄存器将位赋给T T ← Rr(b) T 1 BLD Rd, b 将T 赋给寄存器位Rd(b) ← T 无1 SEC 进位位置位C ← 1 C 1CLC 进位位清零C ← 0 C 1SEN 负标志位置位N ← 1 N 1CLN 负标志位清零N ← 0 N 1SEZ 零标志位置位Z ← 1 Z 1CLZ 零标志位清零Z ← 0 Z 1SEI 全局中断使能I ← 1 I 1CLI 全局中断禁用I ← 0 I 1SES 符号测试标志位置位S ← 1 S 1CLS 符号测试标志位清零S ← 0 S 1SEV 2 的补码溢出标志置位V ← 1 V 1CLV 2 的补码溢出标志清零V ← 0 V 1SET SREG 的T 置位T ← 1 T 1指令集概述275ATmega8(L)2486N–AVR–07/04指令操作数说明操作标志# 时钟数CLT SREG 的T 清零T ← 0 T 1SEH SREG 的半进位标志置位H ← 1 H 1CLH SREG 的半进位标志清零H ← 0 H 1MCU 控制指令NOP 空操作无1SLEEP 休眠( 见对睡眠功能的特殊说明) 无1WDR 复位看门狗( 见对WDR/timer 的特殊说明) 无1。

Instruction mnemonicsThe Assembler accepts mnemonic instructions from the instruction set.A summary of the instruction set mnemonics and their parameters is given here.For a detailed description of the Instruction set,refer to the AVR Data Book.Arithmetic and Logic InstructionsMnemonic Operands Description Operation Flags CyclesADD聽Rd,Rr聽Add without Carry聽Rd=Rd+Rr聽Z,C,N,V,H,S聽1ADC Rd,Rr Add with Carry Rd=Rd+Rr+CZ,C,N,V,H,S1ADIW Rd,K Add Immediate ToWordRd+1:Rd,K Z,C,N,V,S2SUB Rd,Rr Subtract without Carry Rd=Rd-Rr Z,C,N,V,H,S1 SUBI Rd,K8Subtract Immediate Rd=Rd-K8Z,C,N,V,H,S1SBC Rd,Rr Subtract with Carry Rd=Rd-Rr-CZ,C,N,V,H,S1SBCI Rd,K8Subtract with CarryImmedtiateRd=Rd-K8-CZ,C,N,V,H,S1AND Rd,Rr Logical AND Rd=Rd路Rr Z,N,V,S聽1ANDI Rd,K8Logical AND withImmediateRd=Rd路K8Z,N,V,S1OR Rd,Rr Logical OR Rd=Rd V Rr Z,N,V,S1ORI Rd,K8Logical OR withImmediateRd=Rd V K8Z,N,V,S1EOR Rd,Rr Logical Exclusive OR Rd=Rd EORRrZ,N,V,S1COM Rd One's Complement Rd=$FF-Rd Z,C,N,V,S1 NEG Rd Two's Complement Rd=$00-Rd Z,C,N,V,H,S1 SBR Rd,K8Set Bit(s)in Register Rd=Rd V K8Z,C,N,V,S1CBR Rd,K8Clear Bit(s)in Register Rd=Rd路($FF-K8)Z,C,N,V,S1INC Rd Increment Register Rd=Rd+1Z,N,V,S1 DEC Rd Decrement Register Rd=Rd-1Z,N,V,S1TST Rd Test for Zero orNegativeRd=Rd路Rd Z,C,N,V,S1CLR Rd Clear Register Rd=0Z,N,V,S1 SER Rd Set Register Rd=$FF None1SBIW Rdl,K6Subtract Immediatefrom WordRdh:Rdl=Rdh:Rdl-K6Z,C,N,V,S2MUL Rd,Rr Multiply Unsigned R1:R0=Rd*RrZ,C2MULS Rd,Rr Multiply Signed R1:R0=Rd*RrZ,C2MULSU Rd,Rr Multiply Signed withUnsignedR1:R0=Rd*RrZ,C2FMUL Rd,Rr Fractional MultiplyUnsignedR1:R0=(Rd*Rr)<<1Z,C2FMULS Rd,Rr Fractional MultiplySignedR1:R0=(Rd*Rr)<<1Z,C2FMULSU Rd,Rr Fractional MultiplySigned with UnsignedR1:R0=(Rd*Rr)<<1Z,C2聽Branch InstructionsMnemonic Operands Description Operation Flags Cycles RJMP k Relative Jump PC=PC+k+1None2IJMP None Indirect Jump to(Z)PC=Z None2EIJMP None Extended IndirectJump(Z)STACK=PC+1,PC(15:0)=Z,PC(21:16)=EINDNone2JMP k Jump聽PC=k None3RCALL k Relative CallSubroutineSTACK=PC+1,PC=PC+k+1None3/4*ICALL None Indirect Call to(Z)STACK=PC+1,PC=Z聽None3/4*EICALL None Extended IndirectCall to(Z)STACK=PC+1,PC(15:0)=Z,PC(21:16)=EINDNone4*CALL k Call Subroutine STACK=PC+2,PC=kNone4/5*RET None SubroutineReturnPC=STACK None4/5*RETI None Interrupt Return PC=STACK I4/5*CPSE Rd,Rr Compare,Skip ifequal聽if(Rd==Rr)PC=PC2or3None1/2/3CP Rd,Rr Compare Rd-Rr Z,C,N,V,H,S1CPC Rd,Rr Compare withCarryRd-Rr-C Z,C,N,V,H,S1CPI Rd,K8Compare withImmediateRd-K Z,C,N,V,H,S1SBRC Rr,b Skip if bit inregister clearedif(Rr(b)==0)PC=PC+2or3None1/2/3SBRS Rr,b Skip if bit inregister setif(Rr(b)==1)PC=PC+2or3None1/2/3SBIC P,b Skip if bit in I/Oregister clearedif(I/O(P,b)==0)PC=PC+2or3None1/2/3SBIS P,b Skip if bit in I/Oregister setif(I/O(P,b)==1)PC=PC+2or3None1/2/3BRBC s,k Branch if Statusflag clearedif(SREG(s)==0)PC=PC+k+1None1/2BRBS s,k Branch if Statusflag setif(SREG(s)==1)PC=PC+k+1None1/2BREQ k Branch if equal if(Z==1)PC=PC+k+1None1/2BRNE k Branch if notequalif(Z==0)PC=PC+k+1None1/2BRCS k Branch if carry set if(C==1)PC=PC+k+1None1/2BRCC k Branch if carryclearedif(C==0)PC=PC+k+1None1/2BRSH k Branch if same orhigherif(C==0)PC=PC+k+1None1/2BRLO k Branch if lower if(C==1)PC=PC+k+1None1/2BRMI k Branch if minus if(N==1)PC=PC+k+1None1/2BRPL k Branch if plus if(N==0)PC=PC+k+1None1/2BRGE k Branch if greaterthan or equal(signed)if(S==0)PC=PC+k+1None1/2BRLT k Branch if lessthan(signed)if(S==1)PC=PC+k+1None1/2BRHS k Branch if halfcarry flag setif(H==1)PC=PC+k+1None1/2BRHC k Branch if halfcarry flag clearedif(H==0)PC=PC+k+1None1/2BRTS k Branch if T flagsetif(T==1)PC=PC+k+1None1/2BRTC k Branch if T flagclearedif(T==0)PC=PC+k+1None1/2BRVS k Branch if overflowflag setif(V==1)PC=PC+k+1None1/2BRVC k Branch if overflowflag clearedif(V==0)PC=PC+k+1None1/2BRIE k Branch if interrupt if(I==1)PC=PC+k+None1/2enabled1BRID k Branch if interruptdisabledif(I==0)PC=PC+k+1None1/2*Cycle times for data memory accesses assume internal memory accesses,and are not valid for accesses through the external RAM interface.For the instructions CALL,ICALL,EICALL,RCALL,RET and RETI,add three cycles plus two cycles for each wait state in devices with up to16bit PC(128KB program memory).For devices with more than128KB program memory,add five cycles plus three cycles for each wait state.Data Transfer InstructionsMnemonic Operands Description Operation Flags Cycles MOV Rd,Rr Copy register Rd=Rr None1MOVW Rd,Rr Copy register pair Rd+1:Rd=Rr+1:Rr,r,d evenNone1LDI Rd,K8Load Immediate Rd=K None1 LDS Rd,k Load Direct Rd=(k)None2* LD Rd,X Load Indirect Rd=(X)None2*LD Rd,X+Load Indirect andPost-IncrementRd=(X),X=X+1None2*LD Rd,-X Load Indirect andPre-DecrementX=X-1,Rd=(X)None2*LD Rd,Y Load Indirect Rd=(Y)None2*LD Rd,Y+Load Indirect andPost-IncrementRd=(Y),Y=Y+1None2*LD Rd,-Y Load Indirect andPre-DecrementY=Y-1,Rd=(Y)None2*LDD Rd,Y+q Load Indirect withdisplacementRd=(Y+q)None2*LD Rd,Z Load Indirect聽Rd=(Z)None2*LD Rd,Z+Load Indirect andPost-IncrementRd=(Z),Z=Z+1None2*LD Rd,-Z Load Indirect and Z=Z-1,Rd=(Z)None2*Pre-DecrementLDD Rd,Z+q Load Indirect withdisplacementRd=(Z+q)None2*STS k,Rr Store Direct(k)=Rr None2* ST X,Rr Store Indirect(X)=Rr None2*ST X+,Rr Store Indirect andPost-Increment(X)=Rr,X=X+1None2*ST-X,Rr Store Indirect andPre-DecrementX=X-1,(X)=Rr None2*ST Y,Rr Store Indirect(Y)=Rr None2*ST Y+,Rr Store Indirect andPost-Increment(Y)=Rr,Y=Y+1None2ST-Y,Rr Store Indirect andPre-DecrementY=Y-1,(Y)=Rr None2ST Y+q,Rr Store Indirect withdisplacement(Y+q)=Rr None2ST Z,Rr Store Indirect(Z)=Rr None2ST Z+,Rr Store Indirect andPost-Increment(Z)=Rr,Z=Z+1None2ST-Z,Rr Store Indirect andPre-DecrementZ=Z-1,(Z)=Rr None2ST Z+q,Rr Store Indirect withdisplacement(Z+q)=Rr None2LPM None Load Program Memory R0=(Z)None3 LPM Rd,Z Load Program Memory Rd=(Z)None3LPM Rd,Z+Load Program Memory andPost-IncrementRd=(Z),Z=Z+1None3ELPM None Extended Load ProgramMemoryR0=(RAMPZ:Z)None3ELPM Rd,Z Extended Load ProgramMemoryRd=(RAMPZ:Z)None3ELPM Rd,Z+Extended Load ProgramMemory and Post IncrementRd=(RAMPZ:Z),Z=Z+1None3SPM None Store Program Memory(Z)=R1:R0None-ESPM None Extended Store ProgramMemory(RAMPZ:Z)=R1:R0None-IN Rd,P In Port Rd=P None1OUT P,Rr Out Port P=Rr None1 PUSH Rr Push register on Stack STACK=Rr None2POP Rd Pop register from Stack Rd=STACK None2*Cycle times for data memory accesses assume internal memory accesses and are not valid for accesses through the external RAM interface.For the LD,ST,LDD,STD,LDS,STS,PUSH and聽POP instructions, add one cycle plus one cycle for each wait state.Bit and Bit-test InstructionsMnemonic Operands Description Operation Flags CyclesLSL Rd Logical shift left Rd(n+1)=Rd(n),Rd(0)=0,C=Rd(7)Z,C,N,V,H,S1LSR Rd Logical shift right Rd(n)=Rd(n+1),Rd(7)=0,C=Rd(0)Z,C,N,V,S1ROL Rd Rotate leftthrough carryRd(0)=C,Rd(n+1)=Rd(n),C=Rd(7)Z,C,N,V,H,S1ROR Rd Rotate rightthrough carryRd(7)=C,Rd(n)=Rd(n+1),C=Rd(0)Z,C,N,V,S1ASR Rd Arithmetic shiftrightRd(n)=Rd(n+1),n=0,...,6Z,C,N,V,S1SWAP Rd Swap nibbles Rd(3..0)=Rd(7..4),Rd(7..4)=Rd(3..0)None1BSET聽s Set flag SREG(s)=1SREG(s)1 BCLR s Clear flag SREG(s)=0SREG(s)1SBI P,b Set bit in I/OregisterI/O(P,b)=1None2CBI P,b Clear bit in I/O I/O(P,b)=0None2registerBST Rr,b Bit store fromregister to TT=Rr(b)T1BLD Rd,b Bit load fromregister to TRd(b)=T None1SEC None Set carry flag C=1C1 CLC None Clear carry flag C=0C1 SEN None Set negative flag N=1N1CLN None Clear negativeflagN=0N1SEZ None Set zero flag Z=1Z1 CLZ None Clear zero flag Z=0Z1 SEI None Set interrupt flag I=1I1CLI None Clear interruptflagI=0I1SES None Set signed flag S=1S1 CLN None Clear signed flag S=0S1 SEV None Set overflow flag V=1V1CLV None Clear overflowflagV=0V1SET None Set T-flag T=1T1 CLT None Clear T-flag T=0T1SEH None Set half carryflagH=1H1CLH None Clear half carryflagH=0H1NOP None No operation None None1 SLEEP None Sleep See instruction manual None1 WDR None Watchdog Reset See instruction manual None1 BREAK None Execution Break See instruction manual None1The Assembler is not case sensitive.The operands have the following forms:Rd:Destination(and source)register in the register fileRr:Source register in the register fileb:Constant(0-7),can be a constant expressions:Constant(0-7),can be a constant expressionP:Constant(0-31/63),can be a constant expressionK6;Constant(0-63),can be a constant expressionK8:Constant(0-255),can be a constant expressionk:Constant,value range depending on instruction.Can be a constant expression q:Constant(0-63),can be a constant expressionRdl:聽R24,R26,R28,R30.For ADIW and SBIW instructions。

(-2K 28KB)(-2K 28KB) 执行同功能的程序 8MHzAVR 224MHz C5不再有作废的产品; 不需要5分钟的紫外线擦除时间;再也用不着因为掩模而无法入睡了;没有10周订货交货时间; 添加新特性易如反掌;容易调试;容易在线升级,几秒钟搞定;AVR指令表2000/5耿德根编数据传送指令位指令和位测试指令MOV Rd,Rr寄存器拷贝LSL Rd逻辑左移LDI Rd,K装入立即数LSR Rd逻辑右移LDS Rd,K直接从SRAM装入ROL Rd通过进位左循环LD Rd,X X变址间接装入R ROR Rd通过进位右循环LD Rd,X+X变址ASR Rd算术右移LD Rd,-X X变址SWAP s半字节交换LD Rd,Y Y变址BSET s置状态寄存器的位LD Rd,Y+Y变址BCLR s SREG中的位清除LD Rd,-Y Y变址SBI P,b置I/O寄存器的位LDD Rd,Y+q Y变址间接装入R CBI P,b清I/O寄存器的位LD Rd,Z Z变址BST Rr,b R中位到SREG中T标志LD Rd,Z+Z变址BLD Rd,b SREG中T标志到R某位LD Rd,-Z Z变址SEC置位进位标志LDD Rd,Z+q Z变址CLC清除进位标志STS K,Rr R数据直接送SRAM SEN置位负数标志ST X,Rr X变址间接装入SRAM CLN清除负数标志ST X+,Rr X变址SEZ置位零标志ST-X,Rr X变址CLZ清零标志位ST Y,Rr Y变址SEI置位全局中断标志ST Y+,Rr Y变址CLI清除全局中断标志ST-Y,Rr Y变址SES置位符号标志STD Y+q,Rr变址间接装入SRAM CLS清除符号标志ST Z,Rr Z变址SEV置位溢出标志位ST Z+,Rr Z变址CLV清除溢出标志ST-Z,Rr Z变址SET置位T标志STD Z+q,Rr Z变址CLT清除T标志LPM装入程序存储器SEH置位半进位标志IN Rd,P I/O口数据装入到R CLH清除半进位标志OUT P,Rr寄存器数据送I/O口NOP空操作PUSH Rr压寄存器到堆栈SLEEP休眠POP Rd堆栈弹出到寄存器WDR看门狗复位汇编器伪指令(伪指令前必须加“ ..” ).BYTE-- 保存寄节到变量.CSEG-- 代码段.DB-- 字节常数.EXIT-- 退出文件.DEF-- 设置寄存器的符号名.INCLUDE--包括号外的文件.DEVICE--定义被汇编的器件.LIST-- 打开列表文件生成器.DSEG-- 数据段.LISTMAC--打开宏表达式.DW-- 字常数.MACR O-- 宏开始.ENDMACRO--宏结束.NOLIST-- 关闭列表文件生成器.EQU-- 设置符号相等于一个表达式.ORG-- 设置程序起始位置.ESEG-- EPROM段.SET-- 设置一个与表达式相等的符号A VR ICE200在线仿真器双龙电子为中国大陆总代理ICE200可仿真的器件为A T90S1200/2313/2333/4433/4414/8515/4434/8535及A Ttiny10/11/12由于仿真器的电源不对外所以ICE200也支持低电压器件A T90S I/O空间定义十六进制地址名称AT90SMEG103名称AT90S1200名称AT90S8515功能(对应8515名称,*为对应MEG103)$3F($5F)SREG SREG SREG状态寄存器$3E($5E)SPH SPH堆栈指针高$3D($5D)SPL SPL堆栈指针低$3C($5C)XDIV XTAL分频控制器 *$3B($5B)RAMPZ GIMSK GIMSK通用中断屏蔽寄存器$3A($5A)EICR GIFR通用中断标态寄存器$39($59)EIMSK TIMSK TIMSK定时器/计数器中断屏敝寄存器$38($58)EIFR TIFR TIFR定时器/计数器中断标志寄存器$37($57)TIMSK定时器/计数器中断屏敝寄存器 * $36($56)TIFR定时器/计数器中断标志寄存器 * $35($55)MCUCR MCUCR MCUCR MCU通用控制寄存器$34($54)MCUSR MCU通用控制寄存器 *$33($53)TCCR0TCCR0TCCR0定时器/计数器0控制寄存器$32($52)TCNT0TCNT0TCNT0定时器/计数器0(8位)$31($51)OCR0定时器/计数器0输出比较寄存器 * $30($50)ASSR异步方式状态寄存器 *$2F($4F)TCCR1A TCCR1A定时器/计数器1控制寄存器A$2E($4E)TCCR1B TCCR1B定时器/计数器1控制寄存器B$2D($4D)TCNT1H TCNT1H定时器/计数器1高字节$2C($4C)TCNT1L TCNT1L定时器/计数器1低字节$2B($4B)OCR1AH OCR1AH定时器/计数器1输出比较寄存器A高字节$2A($4A)OCR1AL OCR1AL定时器/计数器1输出比较寄存器A低字节$29($49)OCR1BH OCR1BH定时器/计数器1输出比较寄存器B高字节$28($48)OCR1BL OCR1BL定时器/计数器1输出比较寄存器B低字节$27($47)ICR1H定时器/计数器1输入捕获寄存器高字节 * $26($46)ICR1L定时器/计数器1输入捕获寄存器低字节 * $25($45)TCCR2ICR1H T/C1输入捕获寄存器高字节$24($44)TCNT2ICR1L T/C1输入捕获寄存器低字节$23($43)OCR2定时器/计数器2输出比较寄存器 * $22($42)$21($41)WDTCR WDTCR WDTCR看门狗定时控制寄存器$20($40)$1F($3F)EEARH EEARH EPROM地址寄存器高字节$1E($3E)EEARL EEAR EEARL EPROM地址寄存器低字节$1D($3D)EEDR EEDR EEDR EPROM数据寄存器$1C($3C)EECR EECR EECR EPROM控制寄存器$1B($3B)PORTA PORTA A口数据寄存器$1A($3A)DDRA DDRA A口数据方向寄存器$19($39)PINA PINA A口输入脚$18($38)PORTB PORTB PORTB B口数据寄存器$17($37)DDRB DDRB DDRB B口数据方向寄存器$16($36)PINB PINB PINB B口输入脚$15($35)PORTC PORTC C口数据寄存器$14($34)ODRC C口数据方向寄存器$13($33)PINC C口输入脚$12($32)P0RTD PORTD PORTD D口数据寄存器$11($31)DDRD DDRD DDRD D口数据方向寄存器$10($30)PIND PIND PIND D口输入脚$0F($2F)SPOR SPOR SPI I/O数据寄存器$0E($2E)SPSR SPSR SPI状态寄存器$0D($2D)SPCR SPCR SPI控制寄存器$0C($2C)UDR UDR UART I/O数据寄存器$0B($2B)USR USR UART状态寄存器$0A($2A)UCR UCR UART控制寄存器$09($29)UBRR UBRR UART波特率寄存器$08($28)ACSR ACSR ACSR模拟比较控制和状态寄存器$07($27)ADMUX ADC多路选择寄存器 *$06($26)ADCSR ADC状态和控制寄存器 *$05($25)ADCH ADC数据寄存器高 *$04($24)ADCL ADC数据寄存器低 *$03($23)PORIE E口数据寄存器 *$02($22)DDRE E口数据方向寄存器 *$01($21)PINE E口输入脚 *$00($20)PINF F口输入脚 *复位和中断向量向量号程序地址源源中断定义1$000/RESET/RESET硬件脚和看门狗复位2$001INT0INT0外部中断请求03$002INT1INT1外部中断请求14$003TIMER1 CAPT TIMER1 CAPT定时器/计数器1捕获事件5$004TIMER1 COMPA TIMER1 COMPA定时器/计数器1比较匹配A6$005TIMER1 COMPB TIMER1 COMPB定时器/计数器1比较匹配B7$006TIMER1 OVF TIMER1 OVF定时器/计数器1溢出8$007TIMER0 OVF TIMER0 OVF定时器/计数器0溢出9$008SPI,STC SPI,STC串行传送完成10$009UART,RX UART,RX UART,RX完成11$00A UART,UDRE UART,UDRE UART数据寄存器空12$00B UART,TX UART,TX UART,TX完成13$00C ANA_COMP ANA_COMP模拟比较器OK-AVR万用串行下载开发实验板OK-AVR万用串行下载开发实验板,采用双龙电子公司的专利技术(专利号:98226094.6),是为ATMEL公司的AVR单片机特别研制的廉价的万用串行下载开发实验工具该板适用于ATMEL公司所有具有串行下载功能的AVR单片机,同时还可做AVR单片机的I/O口A/D D/A音频输出等实验本公司随机提供了ATMEL的集成模拟仿真调试软件,对初学AVR 单片机的设计者,可暂时节省购买较昂贵的实时仿真器及万用编程器的费用; OK-AVR万用串行下载开发实验板有CZ1电源及通讯下载用插座,LED电源指示,下载通讯工作指示;附AVR单片机8根下载信号线; AVR单片机四种DIP封装器件下载锁紧插座;WR划线电位器可作为模拟信号输入用,有音响器,另有用户器件扩展区,焊接你实验需要的器件;AVR集成软件包包括: AVR Assembler 1.30编译器; AVR Studio 3.00; AVR Prog;送一片AT90S1200单片机及集成软件AVR单片机数据资料OK-AVR下载开发实验板使用说明等光盘AVR单片机可下载器件:90S120090S231390S2323/90LS232390S2343/90LS234390S2333/90LS233390S4433/90LS443390S441490LS851590S4434/90LS443490S8535/90LS853590S8555ATtiny10/11/12/15MEGA103/603/161/163(适用所有串行下载信号线的AVR单片机)。

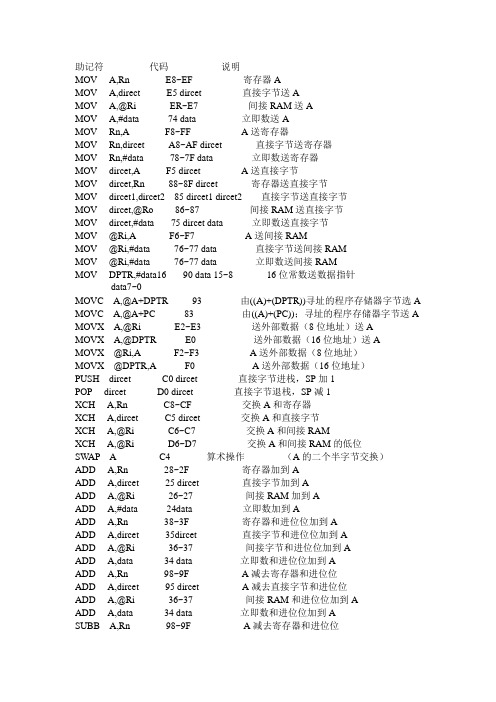

助记符代码说明MOV A,Rn E8~EF 寄存器AMOV A,direct E5 dircet 直接字节送AMOV A,@Ri ER~E7 间接RAM送AMOV A,#data 74 data 立即数送AMOV Rn,A F8~FF A送寄存器MOV Rn,dircet A8~AF dircet 直接字节送寄存器MOV Rn,#data 78~7F data 立即数送寄存器MOV dircet,A F5 dircet A送直接字节MOV dircet,Rn 88~8F dircet 寄存器送直接字节MOV dircet1,dircet2 85 dircet1 dircet2 直接字节送直接字节MOV dircet,@Ro 86~87 间接RAM送直接字节MOV dircet,#data 75 dircet data 立即数送直接字节MOV @Ri,A F6~F7 A送间接RAMMOV @Ri,#data 76~77 data 直接字节送间接RAMMOV @Ri,#data 76~77 data 立即数送间接RAMMOV DPTR,#data16 90 data 15~8 16位常数送数据指针data7~0MOVC A,@A+DPTR 93 由((A)+(DPTR))寻址的程序存储器字节选A MOVC A,@A+PC 83 由((A)+(PC));寻址的程序存储器字节送A MOVX A,@Ri E2~E3 送外部数据(8位地址)送AMOVX A,@DPTR E0 送外部数据(16位地址)送AMOVX @Ri,A F2~F3 A送外部数据(8位地址)MOVX @DPTR,A F0 A送外部数据(16位地址)PUSH dircet C0 dircet 直接字节进栈,SP加1POP dircet D0 dircet 直接字节退栈,SP减1XCH A,Rn C8~CF 交换A和寄存器XCH A,dircet C5 dircet 交换A和直接字节XCH A,@Ri C6~C7 交换A和间接RAMXCH A,@Ri D6~D7 交换A和间接RAM的低位SW AP A C4 算术操作(A的二个半字节交换)ADD A,Rn 28~2F 寄存器加到AADD A,dircet 25 dircet 直接字节加到AADD A,@Ri 26~27 间接RAM加到AADD A,#data 24data 立即数加到AADD A,Rn 38~3F 寄存器和进位位加到AADD A,dircet 35dircet 直接字节和进位位加到AADD A,@Ri 36~37 间接字节和进位位加到AADD A,data 34 data 立即数和进位位加到AADD A,Rn 98~9F A减去寄存器和进位位ADD A,dircet 95 dircet A减去直接字节和进位位ADD A,@Ri 36~37 间接RAM和进位位加到AADD A,data 34 data 立即数和进位位加到ASUBB A,Rn 98~9F A减去寄存器和进位位SUBB A,dircet 95 dircet A减去直接字节和进位位SUBB A,@Ri 96~97 A减去间接RAM和进位位SUBB A,#data 94 data A减去立即数和进位位INC A 04 A加1INC Rn 08~0F 寄存器加1INC dircet 05 dircet 直接字节加1INC @Ri 06~07 间接RAM加1DEC A 14 A减1DEC Rn 18~1F 寄存器减1DEC dircet 15 dircet 直接字节减1DEC @Ri 16~17 间接RAM减1INC DPTR A3 数据指针加1MUL AB A4 A乘以BDIV AB 84 A除以BDA A D4 A的十进制加法调整逻辑操作ANL A,Rn 58~5F 寄存器“与”到AANL A,dircet 55 dircet 直接字节“与”到AANL A,@Ri 56~57 间接RAm“与”到AANL A,#data 54 data 立即数“与”到AANL dircet A 52 dircet A“与”到直接字节ANL dircet,#data 53 dircet data 立即数“与”到直接字节ORL A,Rn 48~4F 寄存器“或”到AORL A,dircet 45 dircet 直接字节“或”到AORL A,@Ri 46~47 间接RAM“或”到AORL A,#data 44 data 立即数“或”到AORL dircet,A 42 dircet A“或”到直接字节ORL dircet,#data 43 dircet data 立即数“或”到直接字节XRL A,Rn 68~6F 寄存器“异或”到AXRL A,dircet 65 dircet 直接字节“异或”到AXRL A,@Ri 66~67 间接RAM“异或”到AXRL A,#data 64 data 立即数“异或”到AXRL dircet A 62 dircet A“异或”到直接字节XRL dircet,#data 63 dircet data 立即数“异或”到直接字节CLR A E4 清零CPL A F4 A取反RL A 23 A左环移RLC A 33 A通过进位左环移RR A 03 A右环移RRC A 13 A通过进位右环移控制程序转移ACALL addr 11 *1 addr(a7~a0) 绝对子程序调用LCALL addr 16 12 addr(15~8) 长子程序调用addr(7~0)RET 22 子程序调用返回RETI addr 11 32 中断调用返回AJMP addr 11 △1 addr(a7~a6) 绝对转移LJMP addr 16 02addr(15~8) 长转移addr(7~0)SJMP rel 80 rel 短转移,相对转移JMP @A+DPTR 73 相对于DPTR间接转移JZ rel 60 rel A为零转移JNZ rel 70 rel A为零转移CJNE A,dircet,rel B5 dircet rel 直接字节与A比较,不等则转移CJNE A,#data,rel B4 data rel 立即数与A比较,不等则转移CJNE A,Rn,#data,rel B8~BF data rel 立即数与寄存器比较,不等则转移CJNE @Ri,#data,rel B6~B7 data rel 立即数与间接RAM比较,不等则移DJNZ Rn,rel D8~DF rel 寄存器减1,不为零则转移DJNZ dircet,rel B5 dircet rel 直接字节减1,不为零则转移NOP 00 空操作*=a10a9a8l△=a10a9a80布尔变量操作CLR C C3 清零进位CLR bit C2 清零直接位SETB C D3 置位进位SETB bit D2 置位直接位CPL C B3 进位取反CPL bit B2 直接位取反ANL C,bit 82 dit 直接数“与”到进位ANL C,/bit B0 直接位的反“与”到进位ORL C,bit 72 bit 直接位“或”到进位ORL C,/bit A0 bit 直接位的反“或”到进位MOV C,bit A2 bit 直接位送进位MOV bit,C 92 bit 进位送直接位JC rel 40 rel 进位位为1转移JNC rel 50 rel 进位位为0转移JB bit,rel 20 bit rel 直接位为1相对转移JNB bit,rel 30 bit rel 直接位为0相对转移JBC bit,rel 10 bit rel 直接位为1相对转移,然后清零该位。

一个单片机所需执行指令的集合即为单片机的指令系统。

单片机使用的机器语言、汇编语言及高级语言,但不管使用是何种语言,最终还是要翻译”成为机器码,单片机才能执行之。

现在有很多半导体厂商都推出了自己的单片机,单片机种类繁多,品种数不胜数,值得注意的是不同的单片机它们的指令系统不一定相同,或不完全相同。

但不管是使用机器语言、汇编语言还是高级语言都是使用指令编写程序的。

所谓机器语言即指令的二进制编码,而汇编语言则是指令的表示符号。

在指令的表达式上也不会直接使用二进制机器码,最常用的是十六进制的形式。

但单片机并不能直接执行汇编语言和高级语言,都必须通过汇编器翻译”成为二进制机器码方能执行,但如果直接使用二进制来编写程序,那将十分不便,也很难记忆和识另h不易编写、难于辨读,极易出错,同时出错了也相当难查找。

所以现在基本上都不会直接使用机器语言来编写单片机的程序。

最好的办法就是使用易于阅读和辨认的指令符号来代替机器码,我们常称这些符号为助记符,用助记符的形式表示的单片机指令就是汇编语言,为便于记忆和阅读,助记符号通常都使用易于理解的英文单词和拼音字母来表示。

每种单片机都有自己独特的指令系统,那么指令系统是开发和生产厂商定义的,如要使用其单片机,用户就必须理解和遵循这些指令标准,要掌握某种(类)单片机,指令系统的学习是必须的。

MCS-51共有111条指令,可分为5类:[1] .数据传送类指令(共29条)[2] .算数运算类指令(共24条)[3] .逻辑运算及移位类指令(共24条)[4] .控制转移类指令(共17条)[5] .布尔变量操作类指令(共17条)一些特殊符号的意义在介绍指令系统前,我们先了解一些特殊符号的意义,这对今后程序的编写都是相当有用的。

Rn――当前选中的寄存器区的8个工作寄存器R0 —R7 (n=0-7 )。

Ri――当前选中的寄存器区中可作为地址寄存器的两个寄存器R0和R1 (i=0,1 )direct —内部数据存储单元的8位地址。

(指令中的符号标识)Rn工作寄存器R0-R7Ri工作寄存器R0和R1@Ri间接寻址的8位RAM单元地址(00H-FFH)#data88位常数#data1616位常数addr1616位目标地址,能转移或调用到64KROM的任何地方addr1111位目标地址,在下条指令的2K范围内转移或调用Rel8位偏移量,用于SJMP和所有条件转移指令,范围-128~+127 Bit片内RAM中的可寻址位和SFR的可寻址位Direct直接地址,范围片内RAM单元(00H-7FH)和80H-FFH$指本条指令的起始位置指令序号助记符指令功能字节周期对标志位的影响P OV AC CY8位立即数传送指令1MOV A,#data data→A立即数传送到累加器211000 2MOV diret,#data data→direct立即数传送到直接地址320000 3MOV@Ri,#data data→(Ri)立即数传送到间接RAM210000 4MOV Rn,#data data→Rn累加器传送到直接地址21000016位立即数传送指令5MOV DPTR,#data16data16→DPTR16位常数加载到数据指针320000内部RAM单元之间的数据传送指令6MOV direct2,direct1(direct1)→direct2直接地址传送到直接地址320000 7MOV direct,@Ri((Ri))→direct间接RAM传送到直接地址220000 8MOV direct,Rn(Rn)→direct寄存器传送到直接地址220000 9MOV@Ri,direct(direct)→(Ri)直接地址传送到间接RAM220000 10MOV Rn,direct(direct)→Rn直接地址传送到寄存器220000通过累加器的数据传送指令11MOV A,direct(direct)→A直接地址传送到累加器210000 12MOV A,@Ri((Ri))→A累加器传送到外部RAM(8地址)110000 13MOV A,Rn(Rn)→A寄存器传送到累加器110000 14MOV direct,A(A)→direct累加器传送到直接地址210000 15MOV@Ri,A(A)→(Ri)直接地址传送到直接地址110000 16MOV Rn,A(A)→Rn累加器传送到寄存器110000Ri作间址寄存器的外部RAM单元读/写指令17MOVX A,@Ri((Ri))→A外部RAM(8地址)传送到累加器120000 18MOVX@Ri,A(A)→(Ri)累加器传送到外部RAM(8地址)120000DPTR作间址寄存器的外部RAM单元读/写指令19MOVX A,@DPTR((DPTR))→A外部RAM(16地址)传送到累加器120000 20MOVX@DPTR,A(A)→(DPTR)累加器传送到外部RAM(16地址)120000程序存储器读指令组21MOVC A,@A+DPTR((A)+(DPTR))→A代码字节传送到累加器121000 22MOVC A,@A+PC((A)+(PC))→A代码字节传送到累加器121000整字节交换指令23XCH A,Rn(Rn)↔(A)寄存器和累加器交换111000 24XCH A,direct(direct)↔(A)直接地址和累加器交换211000 25XCH A,@Ri((Ri))↔(A)间接RAM和累加器交换111000半字节交换指令26XCHD A,@Ri((Ri))3~0↔(A)3~0间接RAM和累加器交换低4位字节111000累加器高低半字节交换指令27SWAP A(A)3~0↔(A)7~4累加器高、低4位交换110000堆栈操作指令组28PUSH direct(SP)+1→SP,(direct)→(SP)直接地址压入堆栈220000 29POP direct((SP))→direct,(SP)-1→SP直接地址弹出堆栈220000加法指令组30ADD A,#data(A)+data→A立即数与累加器求和211111 31ADD A,direct(A)+(direct)→A直接地址与累加器求和211111 32ADD A,@Ri(A)+((Ri))→A间接RAM与累加器求和111111 33ADD A,Rn(A)+(Rn)→A寄存器与累加器求和111111带进位加法指令组34ADDC A,#data(A)+data+(CY)→A立即数与累加器求和(带进位)211111 35ADDC A,direct(A)+(direct)+(CY)→A直接地址与累加器求和(带进位)211111 36ADDC A,@Ri(A)+((Ri))+(CY)→A间接RAM与累加器求和(带进位)111111 37ADDC A,Rn(A)+(Rn)+(CY)→A寄存器与累加器求和(带进位)111111带借位减法指令组38SUBB A,#data(A)-data-(CY)→A累加器减去立即数(带借位)211111 39SUBB A,direct(A)-(direct)-(CY)→A累加器减去直接地址(带借位)211111 40SUBB A,@Ri(A)-((Ri))-(CY)→A累加器减去间接RAM(带借位)111111 41SUBB A,Rn(A)-(Rn)-(CY)→A累加器减去寄存器(带借位)111111加1指令组42INC A(A)+1→A累加器加1111000 43INC direct(direct)+1→direct直接地址加1210000 44INC@Ri((Ri))+1→(Ri)间接RAM加1110000 45INC Rn(Rn)+1→Rn寄存器加1110000 46INC DPTR(DPTR)+1→DPTR数据指针加1120000减1指令组47DEC A(A)-1→A累加器减1111000 48DEC direct(direct)-1→direct直接地址减1210000 49DEC@Ri((Ri))-1→(Ri)间接RAM减1110000 50DEC Rn(Rn)-1→Rn寄存器减1110000乘法指令51MUL AB(A)×(B)→BA累加器和B寄存器相乘141101除法指令52DIV AB(A)/(B)→A……B累加器除以B寄存器141111十进制调整指令53DA A BCD码加减运算结果修正累加器十进制调整111011逻辑“与”运算指令组54ANL direct,A(direct)^(A)→direct累加器“与”到直接地址210000 55ANL direct,#data(direct)^data→direct立即数“与”到直接地址320000 56ANL A,#data(A)^data→A立即数“与”到累加器210000 57ANL A,direct(A)^(direct)→A直接地址“与”到累加器210000 58ANL A,@Ri(A)^((Ri))→A间接RAM“与”到累加器110000 59ANL A,Rn(A)^(Rn)→A寄存器“与”到累加器111000逻辑“或”运算指令组60ORL direct,A(direct)U(A)→direct累加器“或”到直接地址210000 61ORL direct,#data(direct)Udata→direct立即数“或”到直接地址320000 62ORL A,#data(A)Udata→A立即数“或”到累加器211000 63ORL A,direct(A)U(direct)→A直接地址“或”到累加器211000 64ORL A,@Ri(A)U((Ri))→A间接RAM“或”到累加器111000 65ORL A,Rn(A)U(Rn)→A寄存器“或”到累加器111000逻辑“异或”运算指令组66XRL direct,A(direct)○+(A)→direct累加器“异或”到直接地址220000 67XRL direct,#data(direct)○+data→direct立即数“异或”到直接地址320000 68XRL A,#data(A)○+data→A立即数“异或”到累加器211000 69XRL A,direct(A)○+(direct)→A直接地址“异或”到累加器211000 70XRL A,@Ri(A)○+((Ri))→A间接RAM“异或”到累加器111000 71XRL A,Rn(A)○+(Rn)→A寄存器“异或”到累加器111000累加器清072CLR A0→A累加器清零111000累加器取反73CPL A(A)→A累加器求反110000移位指令组74RL A An→An+1,A7→A0累加器循环左移110000 75RR A An+1→An,A0→A7累加器循环右移110000 76RLC A An→An+1,A7→CY,CY→A0带进位累加器循环左移110000 77RRC A An+1→An,CY→A7,A0→CY带进位累加器循环右移111001长转移指令64KB78LJMP addr16addr16→PC无条件长转移320000绝对转移指令2KB79AJMP addr11(PC)+2→PC,addr11→PC10~0无条件绝对转移220000短转移指令256B80SJMP rel(PC)+2→PC,(PC)+rel→PC无条件相对转移220000变址寻址转移指令81JMP@A+DPTR(A)+(DPTR)→PC相对DPTR的无条件间接转移120000累加器判零转移指令82JZ rel若(A)=0,则(PC)+2+rel→PC若(A)≠0,则(PC)+2→PC累加器为0则转移220000 83JNZ rel若(A)≠0,则(PC)+2+rel→PC若(A)=0,则(PC)+2→PC累加器为1则转移220000数值比较转移指令84CJNE A,#data,rel(A)=data,则(PC)+3→PC,0→CY(A)>data,(PC)+3+rel→PC,0→CY(A)<data,(PC)+3+rel→PC,1→CY比较立即数和累加器,不相等转移320000 85CJNE A,direct,rel(A)=(direct),则(PC)+3→PC,0→CY(A)>(direct),(PC)+3+rel→PC,0→CY(A)<(direct),(PC)+3+rel→PC,1→CY比较直接地址和累加器,不相等转移320000数值比较转移指令86CJNE Rn,#data,rel(Rn)=data,则(PC)+3→PC,0→CY(Rn)>data,(PC)+3+rel→PC,0→CY(Rn)<data,(PC)+3+rel→PC,1→CY比较寄存器和立即数,不相等转移320000 87CJNE@Ri,#data,rel((Ri))=data,则(PC)+3→PC,0→CY((Ri))>data,(PC)+3+rel→PC,0→CY((Ri))<data,(PC)+3+rel→PC,1→CY比较立即数和间接RAM,不相等转移320000减1条件转移指令88DJNZ Rn,rel(Rn)-1→Rn若(Rn)≠0,则(PC)+2+rel→PC若(Rn)=0,则(PC)+2l→PC寄存器减1,不为0则转移220000 89DJNZ direct,rel(direct)-1→direct若(direct)≠0,则(PC)+2+rel→PC若(direct)=0,则(PC)+2→PC直接地址减1,不为0则转移320000绝对调用指令90ACALL addr11(PC)+2→PC(SP)+1→SP,(PC)7~0→(SP)(SP)+1→SP,(PC)15~8→(SP)addr11→PC10~0绝对调用子程序220000长调用指令91LCALL addr16(PC)+3→PC(SP)+1→SP,(PC)7~0→(SP)(SP)+1→SP,(PC)15~8→(SP)addr16→PC10~0长调用子程序320000返回指令92RET子程序返回((SP))→PC15~8,(SP)-1→SP((SP))→PC7~0,(SP)-1→SP从子程序返回120000 93RETI中断服务子程序返回((SP))→PC15~8,(SP)-1→SP((SP))→PC7~0,(SP)-1→SP从中断服务子程序返回120000空操作指令94NOP(PC)+1→PC空操作,用于短暂延时110000位传送指令组95MOV C,bit(bit)→CY直接寻址位传送到进位位210001 96MOV bit,C(CY)→(bit)进位位位传送到直接寻址220000位置1指令组97SETB C1→CY置位进位位110001 98SETB bit1→bit置位直接寻址位210000位清0指令组99CLR C0→CY清进位位110001 100CLR bit0→bit清直接寻址位210000位逻辑“与”运算101ANL C,bit(CY)^(bit)→CY直接寻址位“与”到进位位220001 102ANL C,/bit(CY)^(/bit)→CY直接寻址位的反码“与”到进位位220001位逻辑“或”运算103ORL C,bit(CY)U(bit)→CY直接寻址位“或”到进位位220001 104ORL C,/bit(CY)U(/bit)→CY直接寻址位的反码“或”到进位位220001位取反105CPL C(/CY)→CY取反进位位110001 106CPL bit(/bit)→(bit)取反直接寻址位210001以C状态为条件的转移指令107JC rel若(CY)=1,则(PC)+2+rel→PC若(CY)≠1,则(PC)+2→PC如果进位位为1则转移220000 108JNC rel若(CY)≠1,则(PC)+2+rel→PC若(CY)=1,则(PC)+2→PC如果进位位为0则转移220000以位状态为条件的转移指令109JB bit,rel若(bit)=1,则(PC)+3+rel→PC若(bit)≠1,则(PC)+3→PC如果直接寻址位为1则转移320000 110JNB bit,rel若(bit)=0,则(PC)+3+rel→PC若(bit)≠0,则(PC)+3→PC如果直接寻址位为0则转移320000 111JBC bit,rel若(bit)=1,则(PC)+3+rel→PC,0→bit若(bit)≠1,则(PC)+3→PC直接寻址位为1则转移并清除该位320000助记符指令说明字节数周期数(数据传递类指令)MOV A,Rn寄存器传送到累加器11 MOV A,direct直接地址传送到累加器21 MOV A,@Ri累加器传送到外部RAM(8地址)11 MOV A,#data立即数传送到累加器21 MOV Rn,A累加器传送到寄存器11 MOV Rn,direct直接地址传送到寄存器22 MOV Rn,#data累加器传送到直接地址21 MOV direct,Rn寄存器传送到直接地址21 MOV direct,direct直接地址传送到直接地址32 MOV direct,A累加器传送到直接地址21 MOV direct,@Ri间接RAM传送到直接地址22 MOV direct,#data立即数传送到直接地址32 MOV@Ri,A直接地址传送到直接地址12 MOV@Ri,direct直接地址传送到间接RAM21 MOV@Ri,#data立即数传送到间接RAM22 MOV DPTR,#data1616位常数加载到数据指针31 MOVC A,@A+DPTR代码字节传送到累加器12 MOVC A,@A+PC代码字节传送到累加器12 MOVX A,@Ri外部RAM(8地址)传送到累加器12 MOVX A,@DPTR外部RAM(16地址)传送到累加器12 MOVX@Ri,A累加器传送到外部RAM(8地址)12 MOVX@DPTR,A累加器传送到外部RAM(16地址)12 PUSH direct直接地址压入堆栈22POP direct直接地址弹出堆栈22 XCH A,Rn寄存器和累加器交换11 XCH A,direct直接地址和累加器交换21 XCH A,@Ri间接RAM和累加器交换11 XCHD A,@Ri间接RAM和累加器交换低4位字节11(算术运算类指令)INC A累加器加111 INC Rn寄存器加111 INC direct直接地址加121 INC@Ri间接RAM加111 INC DPTR数据指针加112 DEC A累加器减111 DEC Rn寄存器减111 DEC direct直接地址减122 DEC@Ri间接RAM减111 MUL AB累加器和B寄存器相乘14 DIV AB累加器除以B寄存器14 DA A累加器十进制调整11 ADD A,Rn寄存器与累加器求和11 ADD A,direct直接地址与累加器求和21 ADD A,@Ri间接RAM与累加器求和11 ADD A,#data立即数与累加器求和21 ADDC A,Rn寄存器与累加器求和(带进位)11 ADDC A,direct直接地址与累加器求和(带进位)21 ADDC A,@Ri间接RAM与累加器求和(带进位)11 ADDC A,#data立即数与累加器求和(带进位)21 SUBB A,Rn累加器减去寄存器(带借位)11SUBB A,direct累加器减去直接地址(带借位)21 SUBB A,@Ri累加器减去间接RAM(带借位)11 SUBB A,#data累加器减去立即数(带借位)21(逻辑运算类指令)ANL A,Rn寄存器“与”到累加器11 ANL A,direct直接地址“与”到累加器21 ANL A,@Ri间接RAM“与”到累加器11 ANL A,#data立即数“与”到累加器21 ANL direct,A累加器“与”到直接地址21 ANL direct,#data立即数“与”到直接地址32 ORL A,Rn寄存器“或”到累加器12 ORL A,direct直接地址“或”到累加器21 ORL A,@Ri间接RAM“或”到累加器11 ORL A,#data立即数“或”到累加器21 ORL direct,A累加器“或”到直接地址21 ORL direct,#data立即数“或”到直接地址31 XRL A,Rn寄存器“异或”到累加器12 XRL A,direct直接地址“异或”到累加器21 XRL A,@Ri间接RAM“异或”到累加器11 XRL A,#data立即数“异或”到累加器21 XRL direct,A累加器“异或”到直接地址21 XRL direct,#data立即数“异或”到直接地址31 CLR A累加器清零12 CPL A累加器求反11 RL A累加器循环左移11 RLC A带进位累加器循环左移11 RR A累加器循环右移11 RRC A带进位累加器循环右移11SWAP A累加器高、低4位交换11(控制转移类指令)JMP@A+DPTR相对DPTR的无条件间接转移12 JZ rel累加器为0则转移22 JNZ rel累加器为1则转移22 CJNE A,direct,rel比较直接地址和累加器,不相等转移32 CJNE A,#data,rel比较立即数和累加器,不相等转移32 CJNE Rn,#data,rel比较寄存器和立即数,不相等转移22 CJNE@Ri,#data,rel比较立即数和间接RAM,不相等转移32 DJNZ Rn,rel寄存器减1,不为0则转移32 DJNZ direct,rel直接地址减1,不为0则转移32 NOP空操作,用于短暂延时11 ACALL add11绝对调用子程序22 LCALL add16长调用子程序32 RET从子程序返回12 RETI从中断服务子程序返回12 AJMP add11无条件绝对转移22 LJMP add16无条件长转移32 SJMP rel无条件相对转移22(布尔指令)CLR C清进位位11 CLR bit清直接寻址位21 SETB C置位进位位11 SETB bit置位直接寻址位21 CPL C取反进位位11 CPL bit取反直接寻址位21 ANL C,bit直接寻址位“与”到进位位22 ANL C,/bit直接寻址位的反码“与”到进位位22ORL C,bit直接寻址位“或”到进位位22 ORL C,/bit直接寻址位的反码“或”到进位位22 MOV C,bit直接寻址位传送到进位位21 MOV bit,C进位位位传送到直接寻址22JC rel如果进位位为1则转移22 JNC rel如果进位位为0则转移22JB bit,rel如果直接寻址位为1则转移32 JNB bit,rel如果直接寻址位为0则转移32 JBC bit,rel直接寻址位为1则转移并清除该位22(伪指令)ORG指明程序的开始位置DB定义数据表DW定义16位的地址表EQU给一个表达式或一个字符串起名DATA给一个8位的内部RAM起名XDATA给一个8位的外部RAM起名BIT给一个可位寻址的位单元起名END指出源程序到此为止(指令中的符号标识)Rn工作寄存器R0-R7Ri工作寄存器R0和R1@Ri间接寻址的8位RAM单元地址(00H-FFH)#data88位常数#data1616位常数addr1616位目标地址,能转移或调用到64KROM的任何地方addr1111位目标地址,在下条指令的2K范围内转移或调用Rel 8位偏移量,用于SJMP和所有条件转移指令,范围-128~+127Bit片内RAM中的可寻址位和SFR的可寻址位Direct直接地址,范围片内RAM单元(00H-7FH)和80H-FFH $指本条指令的起始位置。