动态时序分析VS静态时序分析

- 格式:docx

- 大小:15.84 KB

- 文档页数:1

时序分析教程范文时序分析(Timing Analysis)是指对数字电路或系统进行时间性能评估和验证的过程。

它主要关注信号在电路中的传播延迟、时钟频率、时序关系等参数,帮助设计者确保电路或系统工作在正确的时序要求下。

时序分析在数字电路的设计和验证中具有重要的作用,特别是对于高速电路和复杂系统来说更为关键。

下面是一些常用的时序分析技术和方法:1.时钟分析:时钟是数字电路中最重要的信号之一,时钟的频率和时钟偏斜对电路的性能有着直接影响。

时钟分析主要关注时钟的频率、时钟偏斜、时钟分配和时钟网络等方面。

通过时钟分析可以评估时钟网络的性能,优化时钟分配方案,减少时钟偏斜等。

2.时序约束:时序约束是指在设计过程中对电路或系统的时序要求进行规定和约束的过程。

时序约束涉及到输入信号和时钟之间的关系,以及输出信号在一些时钟边沿之后的稳态时间等要求。

正确的时序约束有助于设计者确保电路或系统可以在正确的时序要求下运行。

3.时序分析工具:时序分析工具可以帮助设计者对电路或系统进行时序分析和验证。

常用的时序分析工具包括静态时序分析工具和动态时序分析工具。

静态时序分析工具主要通过对电路的逻辑和时钟分析,检查时序约束是否满足。

动态时序分析工具则通过模拟电路行为,计算信号的传播延迟和时序关系。

4.时序优化:时序优化是指通过改变电路结构和布局,减少路径延迟、降低时钟偏斜等手段,提高电路的时序性能。

常用的时序优化技术包括逻辑编码、时钟优化、布局布线优化等。

时序优化需要结合时序分析工具进行验证,确保优化后的电路满足时序要求。

时序分析对数字电路的正确性和性能具有重要的影响,它能帮助设计者在设计和验证过程中找到潜在的问题和改进方案。

因此,时序分析是数字电路设计和验证中必不可少的一部分。

通过学习和掌握时序分析的基本原理和方法,可以提高数字电路设计的质量和效率。

转载]静态时序分析与动态时序分析原文地址:静态时序分析与动态时序分析[zz]IC时序验证用两种方法实现:一是动态时序分析,即根据电路中提取的延时参数,通过仿真软件动态的仿真电路以验证时序是否满足要求。

二是静态时序分析,即通过分析设计中所有可能的信号路径以确定时序约束是否满足时序规范。

动态时序分析的时序确认通过仿真实现,分析的结果完全依赖于验证工程师所提供的激励。

不同激励分析的路径不同,也许有些路径(比如关键路径)不能覆盖到,当设计规模很大时,动态分析所需要的时间、占用的资源也越来越大。

静态时序分析根据一定的模型从网表中创建无向图,计算路径延迟的总和,如果所有的路径都满足时序约束和规范,那么认为电路设计满足时序约束规范。

静态时序分析的方法不依赖于激励,且可以穷尽所有路径,运行速度很快,占用内存很少。

它完全克服了动态时序验证的缺陷,适合大规模的电路设计验证。

对于同步设计电路,可以借助于静态时序分析工具完成时序验证的任务。

基于NanoTime的模拟IP时序验证和模型提取2011-02-20 21:45:21| 分类:模拟知识| 标签:时序 nanotime 模拟 timing 时钟|举报|字号大中小订阅刘杰, 王国玺,夏君,孙永升,刘泰源liujie@深圳市海思半导体有限公司AbstractAnalog and Mixed-signal IPs’ sign-off and accurate timing library generation have been long time bottleneck. As the process geometries shrink to 65, 40 and 28-nanometers, so many nanometer effects impact timing. The available timing margins are diminished. It becomes necessary to generate accurateand functional timing models for the analog and mixed-signal IPs to be able to accurately integrate into SOC design flow. This paper introduced analog IP timing validation and Library extraction using NanoTime. The description based on one of our key mixed-signal SOC project with 65nm technology. The NanoTime hierarchical flow of STA/ETM and the seamless interaction with PrimeTime has been adopted. By improving the timing model accuracy and functionality, timing margins become more realistic and timing convergence becomes less complex. The accuracy of the generated timing libraries is acceptable with proved within 5% correlation comparing with dynamic simulation results of golden HSPICE.Key Words: Analog IP, Tx-STA, ETM, Timing Library, NanoTime, PrimeTime摘要模拟和混合信号IP的签核及完整可信时序模型的提取一直是业界难题。

建⽴时间(setuptime)与保持时间(holdtime)---相关内容静态时序分析:通过穷举分析每⼀条路径的延时,⽤以确定最⾼⼯作频率,检查时序约束是否满⾜,分析时钟质量。

动态时序分析:通过给定输⼊信号,模拟设计在器件实际⼯作的功能和延时情况。

1.什么是建⽴时间、保持时间? 建⽴时间指在触发器的时钟采样沿到来之前,数据保持稳定不变的时间。

保持时间指在触发器的时钟采样沿到来之后,数据保持稳定不变的时间。

因为时钟偏斜,到达DFF2为CLK2建⽴时间分析:取各组块最⼤延时计算考虑时钟到达DFF2的时钟偏斜Tskew,则建⽴时间余量为Tset_slack=Tclk-Tcq-Tco-Tsetup+Tskew,使DFF2建⽴时间不违例,需保证Tset_slack>0。

其中Tcq为DFF1的时钟端到输出延迟,为器件固定属性;Tco是组合逻辑电路的延时,可以通过优化逻辑设计改变其值,使其满⾜建⽴保持时间不违例;Tsetup为触发器固有属性,定值。

Thold为触发器固有属性,定值。

若不考虑DFF2的时钟偏斜,则建⽴时间裕量为Tset_slack=Tclk-Tcq-Tco-Tsetup。

保持时间分析:取各组块最⼩延时计算考虑时钟到达DFF2的时钟偏斜Tskew,则保持时间余量:Tskew+Thold+Thold_slack=Tcq+Tco,因此可推出Thold_slack=Tcq+Tco-Tskew-Thold,使保持时间不违例,则需Thold_slack>0。

若不考虑时钟偏斜,则Thold_slack=Tcq+Tco-Thold。

扩展:时钟抖动:两个时钟周期之间存在的差值,这种误差发⽣在时钟发⽣器内部,和晶振和PLL内部有关,布线对其没有影响。

主要表现在时钟频率上的不⼀定。

时钟偏斜:同样的时钟产⽣的多个⼦时钟信号之间的延时差异。

主要表现在时钟相位上的不确定。

影响时钟偏斜的原因:布线长度及负载,时钟偏斜⽆法避免。

静态时序分析综述报告——孙声震1.静态时序分析静态时序分析(STA)就是套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。

1.1 背景仿真技术是ASIC设计过程中应用最多的验证手段,然而,现在的单片集成系统设计正在将仿真时间推向无法容忍的极限。

在最后的门级仿真阶段,针对的是几十乃至几百万门的电路,对仿真器第一位的要求是速度和容量,因此,性能(仿真速度)和容量(能够仿真的设计规模)是验证中的关键因素。

传统上采用逻辑仿真器验证功能时序,即在验证功能的同时验证时序,它以逻辑模拟方式运行,需要输入向量作为激励。

随着规模增大,所需要的向量数量以指数增长,验证所需时间占到整个设计周期的50%,而最大的问题是难以保证足够的覆盖率。

鉴于此,这种方法已经越来越少地用于时序验证,取而代之的是静态时序分析技术。

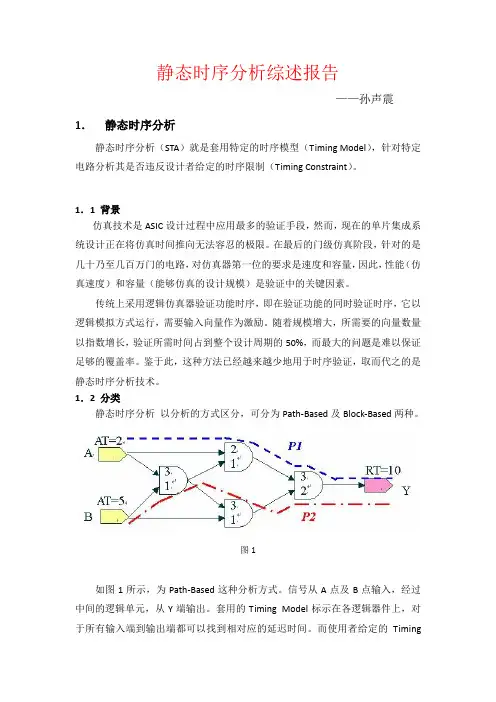

1.2 分类静态时序分析以分析的方式区分,可分为Path-Based及Block-Based两种。

图1如图1所示,为Path-Based这种分析方式。

信号从A点及B点输入,经过中间的逻辑单元,从Y端输出。

套用的Timing Model标示在各逻辑器件上,对于所有输入端到输出端都可以找到相对应的延迟时间。

而使用者给定的TimingConstraint为:1. 信号A到达电路输入端的时间点为2(AT=2,AT为Arrival Time)。

2. 信号B到达电路输入端的时间点为5(AT=5)。

3. 信号必须在时间点10之前到达输出端Y(RT=10,RT为Required Time)。

针对P1及P2 两条路径(Path)来做分析。

P1的起始点为A,信号到达时间点为2。

经过第1个逻辑器件之后,由于有2单位的延迟时间,所以信号到达这个器件输出的时间点为4(2+2)。

依此类推,信号经由P1到达输出Y的时间点为7(2+2+3)。

在和上述第三项Timing Constraint比对之后,我们可以得知对P1这个路径而言,时序(Timing)是满足使用者要求的。

数字电路中的时序分析技术在数字电路的设计中,时序分析是一项至关重要的技术,它可以帮助设计者了解信号在电路中传递的时间和顺序。

这在高速电路的设计中尤为重要,因为信号的传递时间会影响电路的性能和延迟。

时序分析可以帮助设计者进行电路的时序验证,以确保电路的稳定性、正确性和可靠性。

在设计大规模集成电路 (VLSI) 时,时序分析是必不可少的,因为这些电路中的时序关系非常复杂。

时序分析技术可以分为静态时序分析和动态时序分析两种。

静态时序分析是通过模拟电路的各种状态来计算电路的延迟,从而检测电路中的不良时序关系。

而动态时序分析则是在电路运行时检测时序问题,通常采用实时模拟的方法。

静态时序分析可以通过电路布图进行。

在布图中,每个电气元件都有一个延迟时间,这个延迟时间由电气元件的类型和参数来决定。

设计者可以使用电路布图来计算不同元件之间的延迟和电路中的信号传递时间。

动态时序分析需要采用模拟器或仿真工具。

设计者将电路的逻

辑行为转换为实际电路中的信号。

然后,仿真工具会模拟电路的

运行和信号传递,以检测电路中的不良时序关系。

时序分析技术可以帮助设计者识别并解决电路中的不良时序关系。

例如,当电路中存在多个时钟域时,设计者需要进行时钟边

缘的同步以确保顺序正确。

此外,时序分析还可以识别信号高峰、电源不稳定、传输抖动等时序问题,并提供纠正方法。

在数字电路的设计中,时序分析技术是电路稳定性和可靠性的

关键。

设计者需要深入了解电路的时序特性,并使用合适的时序

分析工具和方法来检测和解决不良时序关系。

数字IC设计经典笔试题张戎王舵蒋鹏程王福生袁波摘要本文搜集了近年来数字IC设计公司的经典笔试题目,内容涵盖FPGA、V erilogHDL编程和IC设计基础知识。

AbstractThis article includes some classical tests which have been introduced into interview by companies in digital IC designing in recent years. These tests are varied from FPGA,verlog HDL to base knowledge in IC designing.关键词FPGA VerilogHDL IC设计引言近年来,国内的IC设计公司逐渐增多,IC公司对人才的要求也不断提高,不仅反映在对相关项目经验的要求,更体现在专业笔试题目难度的增加和广度的延伸。

为参加数字IC 设计公司的笔试做准备,我们需要提前熟悉那些在笔试中出现的经典题目。

IC设计基础1:什么是同步逻辑和异步逻辑?同步逻辑是时钟之间有固定的因果关系。

异步逻辑是各时钟之间没有固定的因果关系。

同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。

改变后的状态将一直保持到下一个时钟脉冲的到来,此时无论外部输入 x 有无变化,状态表中的每个状态都是稳定的。

异步时序逻辑电路的特点:电路中除可以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件,电路中没有统一的时钟,电路状态的改变由外部输入的变化直接引起。

2:同步电路和异步电路的区别:同步电路:存储电路中所有触发器的时钟输入端都接同一个时钟脉冲源,因而所有触发器的状态的变化都与所加的时钟脉冲信号同步。

异步电路:电路没有统一的时钟,有些触发器的时钟输入端与时钟脉冲源相连,只有这些触发器的状态变化与时钟脉冲同步,而其他的触发器的状态变化不与时钟脉冲同步。

时序分析基本概念——STA概述简析

在芯片设计中,我们常用PPA(Power, Performance, Area)来衡量一块芯片的指标。

Performace直接取决于Timing参数。

由此可见,时序设计在后端设计中占有举足轻重的地位。

那今天我们就来介绍下,时序分析中的最重要概念——STA。

我们现在生活中其实存在着不少时序问题,比如以下两个例子:

•我打电话给张三,李四却接了电话

这就代表着数据传输过程中出现问题,导致芯片不工作

•我想要一辆法拉利,你却给我的是装着QQ引擎的法拉利

这就代表着芯片没有工作在正常的频率之下。

《IC芯片设计中的静态时序分析实践》读书记录一、内容概览本书详细介绍了静态时序分析的基本概念、原理、方法及其在IC芯片设计中的应用。

在阅读本书的过程中,我形成了一些对该书的理解和内容概览。

该书从静态时序分析的基本原理入手,讲解了静态时序分析在IC芯片设计流程中的地位和作用。

静态时序分析是一种通过静态的方法来分析电路时序的过程,它在芯片设计的验证阶段起到至关重要的作用,确保芯片在规定的时序约束下正确运行。

书中详细阐述了静态时序分析的具体实践方法,包括建立有效的时序分析环境、设置合理的时序约束、进行静态时序分析的工具使用等。

还介绍了静态时序分析中常见的优化技巧,如降低时序违规的风险、提高分析效率等。

在深入理解了静态时序分析的基本原理和方法后,书中还探讨了现代IC芯片设计中的挑战和问题。

随着工艺技术的发展,IC芯片的设计复杂度不断提高,静态时序分析面临着更高的挑战。

书中通过实例分析,展示了如何运用静态时序分析技术来解决这些挑战。

本书还强调了团队合作在IC芯片设计中的重要性,特别是在静态时序分析过程中。

有效的团队协作和沟通能够大大提高分析效率,减少错误的发生。

书中通过实际案例,展示了团队合作在静态时序分析中的具体应用和优势。

本书总结了静态时序分析在IC芯片设计中的应用价值和实践经验。

通过学习和实践本书中的知识和方法,读者能够掌握静态时序分析的核心技能,为未来的IC芯片设计领域做出贡献。

在阅读本书的过程中,我不仅了解了静态时序分析的基本原理和方法,还深入理解了其在现代IC芯片设计中的应用和实践。

通过对书中内容的梳理和总结,我对静态时序分析有了更加全面和深入的认识,为今后的学习和工作打下了坚实的基础。

1. 书籍简介《IC芯片设计中的静态时序分析实践》是一本专注于集成电路(IC)芯片设计领域静态时序分析的权威指南。

本书旨在帮助读者理解并掌握静态时序分析的基本原理、方法与实践应用。

静态时序分析是IC芯片设计过程中的关键环节,对于确保芯片性能、优化功耗以及避免设计缺陷具有重要意义。

时序分析(2):时序约束原理⼀、基本概念1.时序:时钟和数据的对应关系2.约束:告诉综合⼯具,我们希望时序达到什么样的标准3.违例:时序达不到需要的标准4.收敛:通过调整布局布线⽅案来达到这个标准5.静态时序分析:电路未跑起来时,延时等已知,以此分析时序6.动态时序分析:电路跑起来,如Modelsim软件(理想状态)⼆、时序分析基本模型模型分为以下四种:(注:PAD指管脚)寄存器与寄存器之间输⼊PAD与寄存器之间寄存器与输出PA D之间输⼊PAD 与输出PAD之间(太极端,不讨论)知识补充:1、全局时钟:FPGA时钟到各个寄存器的时间⾮常接近。

2、⾃分频时钟:⾛的是数据线,到各个寄存器的时间差异⾮常⼤。

三、理想状态的建⽴时间和保持时间1、建⽴时间 Time setup(1) 接收时钟上升沿前,发送数据要准备好的时间(2) Tsu = 数据锁存沿(Latch)- 数据发送沿(Lanch)= 时钟周期2、保持时间 Time hold(1) 接收时钟上升沿后,发送数据要保持住的时间(2) Th = 发送端数据变化时 - 接收端数据锁存 = 03、补充(1) D触发器本⾝也有建⽴/保持时间的概念,称之为寄存器建⽴时间门限和寄存器保持时间门限,这是⼀个固有属性,是确定的、不变的。

当理想状态时,我们讨论建⽴/保持时间就相当于讨论D触发器的这⼀固有属性。

(2) FPGA所有时序问题,根本原因都是“建⽴时间和保持时间”的问题。

(3) 解决建⽴时间不⾜的⽅法是“减少延时”,⽽解决保持时间不⾜的⽅法是“增加延时”。

4、符号说明四、建⽴时间余量和保持时间余量Lunch edge:发射沿,以 clk_pad 为基准,⼀般看成 0 时刻。

实际时间是上⼀个寄存器所⽤的时间,因此⽤ clk1,看数据到达下⼀个寄存器的 D 端⽤了多久时间,结束时间⼜是多久。

Latch edge:接收沿,以 clk_pad 为基准,⼀般看成 0+Tcyc 时刻,要求时间是下⼀个寄存器计算的时间,所以⽤ clk2,看它⾃⾝需要的到达时间和结束时间是什么时候。

摘要:本文介绍了数字集成电路设计中静态时序分析(Static Timing Analysis)和形式验证(Formal Verification)的一般方法和流程。

这两项技术提高了时序分析和验证的速度,在一定程度上缩短了数字电路设计的周期。

本文使用Synopsys 公司的PrimeTime进行静态时序分析,用Formality进行形式验证。

由于它们都是基于Tcl(Tool Command Language)的工具,本文对Tcl也作了简单的介绍。

关键词:静态时序分析形式验证 PrimeTime Formality Tcl目录第一章绪论 (1)1.1 静态时序分析1.2 时序验证技术第二章PrimeTime简介 (3)2.1 PrimeTime的特点和功能2.2 PrimeTime进行时序分析的流程2.3 静态时序分析中所使用的例子2.4 PrimeTime的用户界面第三章Tcl与pt_shell的使用 (6)3.1 Tcl中的变量3.2 命令的嵌套3.3 文本的引用3.4 PrimeTime中的对象3.4.1 对象的概念3.4.2 在PrimeTime中使用对象3.4.3 针对collection的操作3.5 属性3.6 查看命令第四章静态时序分析前的准备工作 (12)4.1 编译时序模型4.1.1 编译Stamp Model4.1.2 编译快速时序模型4.2 设置查找路径和链接路径4.3 读入设计文件4.4 链接4.5 设置操作条件和线上负载4.6 设置基本的时序约束4.6.1 对有关时钟的参数进行设置4.6.2 设置时钟-门校验4.6.3 查看对该设计所作的设置4.7 检查所设置的约束以及该设计的结构第五章静态时序分析 (18)5.1 设置端口延迟并检验时序5.2 保存以上的设置5.3 基本分析5.4 生成path timing report5.5 设置时序中的例外5.6 再次进行分析第六章 Formality简介 (22)6.1 Formality的基本特点6.2 Formality在数字设计过程中的应用6.3 Formality的功能6.4 验证流程第七章形式验证 (27)7.1 fm_shell命令7.2 一些基本概念7.2.1 Reference Design和Implementation Design7.2.2 container7.3 读入共享技术库7.4 设置Reference Design7.5 设置Implementation Design7.6 保存及恢复所作的设置7.7 验证第八章对验证失败的设计进行Debug (32)8.1 查看不匹配点的详细信息8.2 诊断程序8.3 逻辑锥8.3.1 逻辑锥的概念8.3.2 查看不匹配点的逻辑锥8.3.3 使用逻辑锥来Debug8.3.4 通过逻辑值来分析第一章 绪论我们知道,集成电路已经进入到了VLSI和ULSI的时代,电路的规模迅速上升到了几十万门以至几百万门。

计算机硬件设计中的时序分析方法时序分析是计算机硬件设计过程中非常重要的一环。

它可以帮助设计师确保系统中各个元件的工作时序满足预期的要求,从而保证系统的正确性和稳定性。

本文将介绍几种常见的时序分析方法,包括静态时序分析、动态时序分析以及时钟域分析。

一、静态时序分析静态时序分析是在不考虑信号传输延迟和时钟周期的情况下进行的时序分析。

它主要依赖于电路元件的逻辑关系和布局设计来进行分析。

在进行静态时序分析时,需要提供设计的电路原理图、信号路径以及逻辑关系等信息。

常用的静态时序分析工具包括VHDL等硬件描述语言,它们可以帮助设计师对电路进行建模、仿真和验证,从而找到潜在的时序问题。

静态时序分析可以帮助设计师发现电路中的时序冲突、时序违约和时序不确定性等问题。

通过对电路进行静态时序分析,设计师可以提前预测并解决可能出现的时序问题,从而减少后期测试的工作量和风险。

二、动态时序分析动态时序分析是指考虑信号传输延迟和时钟周期的情况下进行的时序分析。

它主要依赖于电路的时钟边沿和时钟周期等信息进行分析。

在进行动态时序分析时,需要提供设计的时钟频率、延迟模型以及电路中的时钟约束等信息。

常用的动态时序分析工具包括模拟器和时序分析器等。

动态时序分析可以帮助设计师检测电路中的时序故障、时序偏差和时序违规等问题。

通过对电路进行动态时序分析,设计师可以模拟真实的工作环境,准确评估电路的时序性能,从而提前发现并解决时序问题。

三、时钟域分析时钟域分析是指对电路中不同时钟域的信号传输进行分析。

在现代的计算机硬件设计中,通常存在多个时钟域,每个时钟域都有自己的时钟信号和时钟延迟特性。

时钟域之间的信号传输需要进行专门的时序分析,以保证信号的正确传递和同步。

时钟域分析可以帮助设计师解决时钟间的异步问题、时序冲突和时序不一致等。

通过对不同时钟域的信号传输进行分析,设计师可以确定时钟域之间的接口逻辑,优化时钟插入和同步方法,确保电路的正常工作。

静态时序分析电子科技大学詹璨铭什么是静态时序分析⏹静态时序分析STA(static timing analysis)⏹定义⏹与动态时序分析的差异怎样做静态时序分析⏹使用工具primetime (简称pt)与DC ⏹两者的兼容性⏹为什么使用primetime?Primetime与DC的兼容性⏹使用同样的工艺库和设计文件⏹许多指令一样⏹相同的算法,很多结果也一样⏹从一个synthesizable subcircuit 中,pt能捕获一个时序环境,并写成一系列的dc指令,在dc中用其为这个subcircuit定义时间约束和时序优化--值得关注⏹为dc写的dcsh格式的脚本可以翻译成在pt上用的格式。

在pt中定义为抄本(transcript)格式⏹这两个都支持用SDC(synopsys design constraints)格式指定设计规则,包括时间面积约束。

为什么用pt⏹更快效率更高⏹占用更少的内存⏹具有高级的芯片级的分析能力和高级的建模能力。

STA中的对象⏹Design -完整的设计⏹Cell(instance)-设计中使用的一个元件⏹Net -金属连线⏹Port -design 的I/O口⏹Pin -cell 的I/O口⏹Reference -是元件的参考的源定义⏹Clock -创建的时钟信号时序弧(timing arc)⏹定义:如果把电路看作是一张很大的拓扑图,那么图中的结点就是电路中的引脚(pin)。

结点与结点之间的部分,我们称作是时序弧(timing arc)。

他定义了任意两个结点之间的时序关系。

⏹最直观基本的理解:cell delay与net delay。

这两个也是计算下面时序弧的基础。

每段时序弧的延时就是把这两个值不断相加时序弧分类一:时序的延时⏹组合时序弧(combinational timing arc)⏹边沿时序弧(edge timing arc)⏹重置和清除时序弧(preset and clear timing arc)⏹三态使能/无效时序弧(three state enable/disable timing arc)时序弧分类二:时序约束⏹建立时序弧(setup timing arc)⏹保持时序弧(hold timing arc)⏹恢复时序弧(recovery timing arc)⏹清除时序弧(removal timing arc)⏹宽度时序弧(width timing arc)组合时序弧(combinationaltiming arc)⏹负函数(negative unate)⏹正函数(positive unate)⏹非函数(non-unate)calculation)--cell delay⏹是从一个逻辑门的输入到输出的延迟量⏹通过工艺库(technology library)来查找的⏹这是个2维表,查找项是输入的过渡时间(input transition),输出的电容负载(output load capacitance)没有对应的值,做一个线性的推导,计算出相应的值。

前言静态时序分析以它运行速度很快、占用内存较少,可以对芯片设计进行全面的时序功能检查,并利用时序分析的结果来优化设计等优点,很快地被用到数字集成电路设计的验证中。

然而门级仿真也由于它不可取代的地位在ASIC设计中仍有一席之地。

结合在TDS-CDMA数字基带处理芯片设计中的经验,我们可以得出这样的结论:静态时序分析和门级时序仿真是从不同的侧重点来分析电路以保证电路的时序正确,它们是相辅相成的。

现在,实验中的TDS-CDMA数字基带处理芯片已经成功流片。

本文的创新点在于,在实践中寻找到一种STA和门级仿真结合的新方法。

在保证流片成功率的基础上最大程度的节省芯片验证的时间。

关键词:静态时序分析门级时序仿真芯片随着深亚微米技术的发展,数字电路的规模已经发展到上百万门甚至上千万门。

工艺也从几十μm提高到65nm甚至45nm。

这样的电路规模做验证的时间在整个芯片的开发周期所占的比例会越来越重。

通常,在做验证的时候,我们都会采用动态验证的方法。

现在,用静态验证方法(STA Static Timing Analysis),不仅能够完成验证的工作,而且还能大大节省验证所需要的时间。

静态时序分析简称它提供了一种针对大规模门级电路进行时序验证的有效方法。

静态时序分析是相对于动态时序分析而言的。

动态时序分析时不可能产生完备的测试向量,覆盖门级网表中的每一条路径。

因此在动态时序分析中,无法暴露一些路径上可能存在的时序问题;而静态时序分析,可以方便地显示出全部路径的时序关系,因此逐步成为集成电路设计签字认可的标准。

静态时序分析工作原理本文以Synopsys公司的Prime Time SI作为时序分析的工具,介绍静态时序分析的工作原理。

Prime Time把整个设计电路打散成从主要的输入端口到电路触发器、从触发器到触发器、从触发器到主要输出端口、从主要的输出端口到主要的输出端口、四种类型的时序路径,分析不同路径的时序信息,得到建立时间(setup time)和保持时间(hold time)的计算结果。

动态时序分析VS静态时序分析(转)

2010-12-19 10:37:37| 分类:学习资料| 标签:分析验证静态路径时序|字号大中小订阅

动态时序验证是在验证功能的同时验证时序,需要输入向量作为激励。

随着规模增大,所需要的向量数量以指数增长,验证所需时间占到整个设计周期的50,且这种方法难以保证足够的覆盖率,因而对片上系统芯片设计已成为设计流程的瓶颈,所以必须有更有效的时序验证技术取代之。

动态时序仿真的优点是比较精确,而且同静态时序相比较,它适用于更多的设计类型。

但是它也存在着比较明显的缺点:

首先是分析的速度比较慢;

其次是它需要使用输入矢量,这使得它在分析的过程中有可能会遗漏一些关键路径(critical paths),因为输入矢量未必是对所有相关的路径都敏感的。

静态时序分析技术是一种穷尽分析方法,用以衡量电路性能。

它提取整个电路的所有时序路径,通过计算信号沿在路径上的延迟传播找出违背时序约束的错误,主要是检查建立时间和保持时间是否满足要求,而它们又分别通过对最大路径延迟和最小路径延迟的分析得到。

静态时序分析的方法不依赖于激励,且可以穷尽所有路径,运行速度很快,占用内存很少。

它完全克服了动态时序验证的缺陷,适合进行超大规模的片上系统电路的验证,可以节省多达20的设计时间。

因此,静态时序分析器在功能和性能上满足了全片分析的目的。