集成电路制造工艺流程图

- 格式:ppt

- 大小:5.30 MB

- 文档页数:63

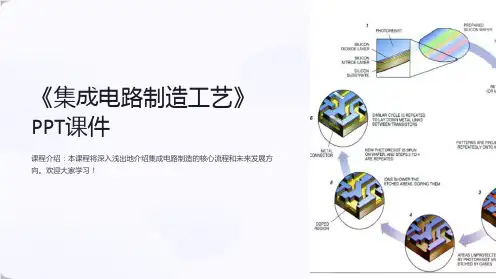

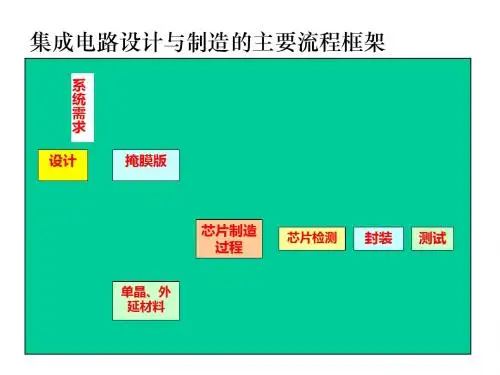

集成电路制造工艺流程概述集成电路(Integrated Circuit, IC)是由几千个甚至是数十亿个离散电子元件,如晶体管、电容、电阻等构成的电路,在特定的芯片上进行集成制造。

IC制造工艺流程主要包括晶圆制备、晶圆加工、芯片制造、封装测试等几个环节,是一个非常严谨、复杂的过程。

晶圆制备晶圆制备是IC制造的第一步。

晶圆是用硅单晶或其他半导体材料制成的薄片,作为IC芯片的基础材料。

以下是晶圆制备的流程:1.单晶生长:使用气态物质的沉积和结晶方法,使单晶硅的原料在加热、冷却的过程中逐渐成为一整块的单晶硅材料。

2.切片:将生长好的单晶硅棒利用切割机械进行切片,制成形状规整的圆片,称为晶圆。

3.抛光:将晶圆表面进行机械研磨和高温氧化处理,使表面达到极高的光滑度。

4.清洗:用去离子水等高纯度溶剂进行清洗,清除晶圆表面的污染物,确保晶圆的纯度和光洁度。

晶圆加工晶圆加工是IC制造的关键环节之一,也是最为复杂的过程。

在晶圆加工过程中,需要通过一系列的步骤将原始的晶圆加工为完成的IC芯片。

以下为晶圆加工的流程:1.光刻:通过光刻机将芯片图案转移到光刻胶上,然后使用酸洗、去除光刻胶,暴露出芯片的表面。

2.蚀刻:利用化学蚀刻技术,在IC芯片表面形成电路图案。

3.离子注入:向芯片进行掺杂,改变材料的电学性质。

4.热处理:对芯片进行高温、低温处理,使其达到设计要求的电学性能。

5.金属沉积:在芯片表面沉积一层金属,用于连接芯片各个元件。

芯片制造芯片制造是最为核心的IC制造环节,主要将晶圆加工后的芯片进行裁剪、测试、绑定等操作,使其具备实际的电学性能。

以下是IC芯片制造的流程:1.芯片测试:对芯片的性能进行测试,找出不合格的芯片并予以淘汰。

2.芯片切割:将晶圆上的芯片根据需求进行切割。

3.接线:在芯片表面安装金线,用于连接各个器件。

4.包装:将芯片放入封装盒中,并与引线焊接,形成成品IC芯片。

封装测试封装测试是IC制造的最后一步。

集成电路生产工艺流程(一)集成电路生产工艺概述集成电路生产工艺是指将所有电子元件集成在单一芯片上的生产过程。

它被广泛应用于电子设备制造业,如计算机、手机、电视等。

制造流程1.设计–集成电路设计师设计电路–使用EDA软件进行仿真与验证2.掩膜制造–制造掩膜–通过光刻技术将图案转移到硅片上3.投影光刻–使用掩膜将图案投影在硅片上–制造电路的输送4.融合–在高温下将掩膜和硅片融合–形成晶体管5.化学处理–使用化学液体进行蚀刻–将不需要的硅层去除6.金属化–在硅片表面蒸镀金属–形成线路和电极7.包装测试–切割硅片–用陶瓷或塑料封装芯片–测试芯片性能制造技术1.CMOS–基础工艺–低功耗和低噪音2.BJT–晶体管工艺–高频率和高速率3.BCD–模拟与数字工艺结合–适用于汽车、医疗和航空等领域4.MEMS–微电子机械系统–功能丰富的微型机械装置制造挑战1.芯片尺寸缩小–越来越小的芯片尺寸–需要更精密的光刻技术和更高的抗干扰能力2.成本控制–竞争日益激烈–芯片制造成本需要持续降低3.故障排除–单个芯片上有上亿个晶体管–如何排查其中的问题是一个挑战结论集成电路生产工艺是一个非常复杂的过程,需要各个流程相互合作,使用最新的技术和设备。

随着时间的推移,它将继续进化和改进,以满足越来越高的市场需求和更严格的质量控制。

制造趋势1.三维IC制造技术–将多个芯片堆叠在一起,以提高芯片效率和成本效益2.全球晶圆制造技术–分布式制造技术可帮助降低成本–全球晶圆制造可促进产业链的全球化3.自动化技术–机器学习和人工智能将推动制造工艺的自动化–减少人为干扰和错误应用领域1.通信–集成电路的高速率和低功耗等特点十分适合通信应用2.计算机–处理器、内存、存储等都需要集成电路–集成电路的不断进步也推动了计算机性能的提升3.汽车–外部环境复杂,需要集成电路来实现各种功能–集成电路技术适合于汽车电子系统的小型化和高度集成化4.医疗–集成电路技术在医疗成像、生物传感器和仿生器件等方面有广泛应用–提升了医疗设备的精度和可靠性结语随着各种工业领域的发展和需要,集成电路生产工艺将继续前进和改进。

集成电路制造工艺流程1.晶圆制造( 晶体生长-切片-边缘研磨-抛光-包裹-运输 )晶体生长(Crystal Growth)晶体生长需要高精度的自动化拉晶系统。

将石英矿石经由电弧炉提炼,盐酸氯化,并经蒸馏后,制成了高纯度的多晶硅,其纯度高达0.99999999999。

采用精炼石英矿而获得的多晶硅,加入少量的电活性“掺杂剂”,如砷、硼、磷或锑,一同放入位于高温炉中融解。

多晶硅块及掺杂剂融化以后,用一根长晶线缆作为籽晶,插入到融化的多晶硅中直至底部。

然后,旋转线缆并慢慢拉出,最后,再将其冷却结晶,就形成圆柱状的单晶硅晶棒,即硅棒。

此过程称为“长晶”。

硅棒一般长3英尺,直径有6英寸、8英寸、12英寸等不同尺寸。

硅晶棒再经过研磨、抛光和切片后,即成为制造集成电路的基本原料——晶圆。

切片(Slicing) /边缘研磨(Edge Grinding)/抛光(Surface Polishing)切片是利用特殊的内圆刀片,将硅棒切成具有精确几何尺寸的薄晶圆。

然后,对晶圆表面和边缘进行抛光、研磨并清洗,将刚切割的晶圆的锐利边缘整成圆弧形,去除粗糙的划痕和杂质,就获得近乎完美的硅晶圆。

包裹(Wrapping)/运输(Shipping)晶圆制造完成以后,还需要专业的设备对这些近乎完美的硅晶圆进行包裹和运输。

晶圆输送载体可为半导体制造商提供快速一致和可靠的晶圆取放,并提高生产力。

2.沉积外延沉积 Epitaxial Deposition在晶圆使用过程中,外延层是在半导体晶圆上沉积的第一层。

现代大多数外延生长沉积是在硅底层上利用低压化学气相沉积(LPCVD)方法生长硅薄膜。

外延层由超纯硅形成,是作为缓冲层阻止有害杂质进入硅衬底的。

过去一般是双极工艺需要使用外延层,CMOS技术不使用。

由于外延层可能会使有少量缺陷的晶圆能够被使用,所以今后可能会在300mm晶圆上更多采用。

9.晶圆检查Wafer Inspection (Particles)在晶圆制造过程中很多步骤需要进行晶圆的污染微粒检查。

集成电路制造工艺流程引言:集成电路(IC)作为现代电子技术的核心,被广泛应用于计算机、通信、消费电子等领域。

集成电路制造工艺是将原始材料经过一系列加工步骤,将电路图案和其他组件集成到单片硅芯片上的过程。

本文将详细介绍集成电路制造的工艺流程。

一、晶圆制备1.材料准备:通常采用硅作为晶圆基底材料。

硅材料需经过多次高温处理来去除杂质。

2.切割:将硅原料切割成圆片形状,厚度约为0.4毫米。

3.晶圆清洗:通过化学和物理方法清洗硅片表面。

二、晶圆表面处理1.清洗:使用化学物质去除晶圆表面的有机和无机污染物。

2.二氧化硅沉积:在晶圆表面形成一层绝缘层,以保护电路。

3.光刻:通过对光敏材料进行曝光、显影和刻蚀等步骤,将电路图案转移到晶圆表面。

三、激活剂注入1.清洗:清洗晶圆表面以去除光刻过程产生的残留物。

2.掺杂:使用离子注入设备将所需的杂质注入晶圆表面,以改变材料的导电性。

四、金属化1.金属沉积:在晶圆上沉积一层金属,通常是铝或铜,以用作导电线。

2.蚀刻:使用化学溶液去除多余的金属,只保留所需的电路。

3.封装:将晶圆裁剪成多个小片,然后分别进行封装,以提供保护和连接接口。

五、测试1.功能测试:确保电路功能正常。

2.可靠性测试:对电路进行长时间运行测试,以验证其性能和可靠性。

3.封装测试:测试封装后的芯片性能是否正常。

六、成品测试和封装1.最终测试:对芯片进行全面测试,以确保其达到预期的性能指标。

2.封装:在芯片表面添加保护层,并提供引脚用于连接到其他电子设备。

结论:本文详细介绍了集成电路制造的工艺流程,包括晶圆制备、晶圆表面处理、激活剂注入、金属化、测试和封装等环节。

每一步都是为了保证集成电路的性能和可靠性。

随着科技的不断发展,集成电路制造工艺也在不断创新,以提高集成电路的性能和功能。

集成电路制造工艺流程晶体的生长晶体切片成wafer晶圆制作功能设计à模块设计à电路设计à版图设计à制作光罩工艺流程1) 表面清洗晶圆表面附着一层大约 2um 的 Al2O3 和甘油混合液保护之 , 在制作前必须进行化学刻蚀和表面清洗。

2) 初次氧化有热氧化法生成 SiO2 缓冲层,用来减小后续中 Si3N4 对晶圆的应力氧化技术干法氧化Si( 固 ) + O2 = SiO2( 固 )湿法氧化Si( 固 ) +2H2O =SiO2( 固 ) + 2H2干法氧化通常用来形成,栅极二氧化硅膜,要求薄,界面能级和固定电荷密度低的薄膜。

干法氧化成膜速度慢于湿法。

湿法氧化通常用来形成作为器件隔离用的比较厚的二氧化硅膜。

当 SiO2 膜较薄时,膜厚与时间成正比。

SiO2 膜变厚时,膜厚与时间的平方根成正比。

因而,要形成较厚的 SiO2 膜,需要较长的氧化时间。

SiO2 膜形成的速度取决于经扩散穿过 SiO2 膜到达硅表面的 O2 及 OH 基等氧化剂的数量的多少。

湿法氧化时,因在于 OH 基在 SiO2 膜中的扩散系数比 O2 的大。

氧化反应, Si 表面向深层移动,距离为 SiO2 膜厚的 0.44 倍。

因此,不同厚度的 SiO2 膜,去除后的 Si 表面的深度也不同。

SiO2 膜为透明,通过光干涉来估计膜的厚度。

这种干涉色的周期约为 200nm ,如果预告知道是几次干涉,就能正确估计。

对其他的透明薄膜,如知道其折射率,也可用公式计算出(d SiO2) / (d ox) = (n ox) / (n SiO2) 。

SiO2 膜很薄时,看不到干涉色,但可利用 Si 的疏水性和 SiO2 的亲水性来判断 SiO2 膜是否存在。

也可用干涉膜计或椭圆仪等测出。

SiO2 和 Si 界面能级密度和固定电荷密度可由 MOS 二极管的电容特性求得。

(100) 面的 Si 的界面能级密度最低,约为 10E+10 -- 10E+11/cm – 2 .e V -1 数量级。

现代集成电路芯片制造工艺流程。

3)14nm节点FinFET工艺流程。

(后栅工艺BEOL+FEOL)3.1流程概述:晶圆材料-隔离—淀积多晶硅—芯轴—鳍硬掩膜(“侧墙”)—刻蚀形成鳍—双阱形成—制作临时辅助栅—补偿隔离—LDD注入—侧墙主隔离—漏源极形成(应变硅技术)—金属硅化物—器件与金属间介质层ILD—置换高k金属栅—钨栓—第一层金属间介质(超低K介质)IMD-1—第一层铜布线—第二层金属间介质(超低K介质)IMD-2—第二层铜布线......多层布线最上层铝布线制作压焊窗口—最上层介质钝化层(光刻压焊/测试焊盘)—测氧化硅—去胶—刻蚀硅平坦氮化硅硬掩(芯轴宽度决定后面工序的去除芯轴之外的硬掩膜—刻蚀多晶硅形成芯轴。

淀积二氧化硅隔离层(控制鳍宽度的“侧墙”硬掩控制淀积时间达到控制二氧化硅厚度—干法回,作为形成鳍,去除(刻蚀)芯轴上的氮化硅硬掩膜层—再湿法刻蚀掉芯轴多晶硅,保留“侧墙”—以“侧墙”为硬掩膜)。

6a/(图未按比例,以数(例如栅长Self各在一个“鳍”示意,以下只以O3CMP,形(如图两次曝光,二重图案法光刻刻蚀硬掩膜(刻蚀掉底,保留鳍上部阱区域,阱区域,进之后去掉,使有源分别光刻,分别进行调整阈值电压(作为后面去除多晶硅临时栅的停止层),二氧化硅,淀积氮氧化硅(硬掩刻蚀多晶硅形成临时硅栅,刻蚀后露出源、漏nmos离子注入(注入砷)和口(图离子)和口袋离子注入磷(预先非晶化掺杂)章节为采用区(掩蔽其他区,漏源和衬底连接窗口上约的之后在氮气气氛转化为低阻SC1形成低阻金(提高载流子迁移率之后淀积二氧化硅作为生长外延层凸起的,外延漏源凸起。

以便后面形成金属硅化物有充足的漏源及衬底接触孔之外的和表面的二氧化硅阻挡层,重新淀积淀积作为阻挡同时凸起。

和表面的二氧化硅阻挡层,重新淀积作为阻挡金属硅化物淀nmosTiN℃退火,形成高阻之后在氮气气转化为低℃)用漏150Å/磷将磷硅玻璃包裹密停止在多晶硅层,湿法腐蚀去)设备淀积界面氧化层功函40Å(也可用)湿法刻蚀去掉上次(也(热约退火,去除多余的鈷抛光钨平坦反应腔中通入硅烷、O3/TEOS/B(OC2H5)3/PO(OC2H5)3是用于第一层RCPECVDSiCOH(3000Å),—淀积二氧介质介CHO有机复合)和可见光处理排出有机体,最,其作用是将不同区域为氧化层——淀积阻挡层和铜种子层——电镀铜——抛光铜,形成金属第一次:淀积6000Å低温—清洗—堵住孔再在上面淀积氧化层,再光刻布线槽。