集成电路版图设计基础第4章:标准单元技术

- 格式:ppt

- 大小:296.00 KB

- 文档页数:29

集成电路原理与设计重点内容总结第一章绪论摩尔定律:(P4)集成度大约是每18个月翻一番或者集成度每三年4倍的增长规律就是世界上公认的摩尔定律。

集成度提高原因:一是特征尺寸不断缩小,大约每三年缩小一2倍;二是芯片面积不断增大,大约每三年增大1.5倍;三是器件和电路结构的不断改进。

等比例缩小定律:(种类优缺点)(P7-8)1. 恒定电场等比例缩小规律(简称CE定律)a. 器件的所有尺寸都等比例缩小K倍,电源电压也要缩小K倍,衬底掺杂浓度增大K倍,保证器件内部的电场不变。

b. 集成度提高忆倍,速度提高K倍,功耗降低K2倍。

c. 改变电源电压标准,使用不方便。

阈值电压降低,增加了泄漏功耗。

2. 恒定电压等比例缩小规律(简称CV定律)a. 保持电源电压和阈值电压不变,器件的所有几何尺寸都缩小K倍,衬底掺杂浓度增加忆倍。

b. 集成度提高忆倍,速度提高K2倍。

c. 功耗增大K倍。

内部电场强度增大,载流子漂移速度饱和,限制器件驱动电流的增加。

3. 准恒定电场等比例缩小规则(QCE)器件尺寸将缩小K倍,衬底掺杂浓度增加K(1< <K)倍,而电源电压则只变为原来的/K倍。

是CV和CE的折中。

需要高性能取接近于K,需要低功耗取接近于1。

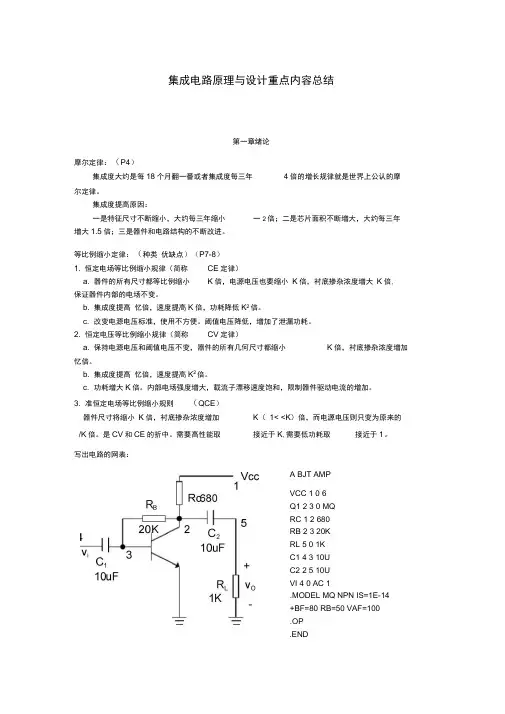

写出电路的网表:A BJT AMPVCC 1 0 6Q1 2 3 0 MQRC 1 2 680RB 2 3 20KRL 5 0 1KC1 4 3 10UC2 2 5 10UVI 4 0 AC 1.MODEL MQ NPN IS=1E-14+BF=80 RB=50 VAF=100.OP.END其中.MODEL为模型语句,用来定义BJT晶体管Q1的类型和参数。

常用器件的端口电极符号器件名称端口付号缩与Q (双极型晶体管) C (集电极),B (基极),E (发射极),S (衬底)M (MO场效应管) D (漏极),G (栅极),S (源极),B (衬底)J (结型场效应管) D (漏极),G (栅极),S (源极)B (砷化镓场效应管) D (漏极),G (栅极),S (源极)电路分析类型.OP直流工作点分析.TRAN瞬态分析• DC直流扫描分析• FOUR傅里叶分析•TF传输函数计算.MC豕特卡罗分析•SENS灵敏度分析•STEP参数扫描分析.AC交流小信号分析•WCASE最坏情况分析• NOISE噪声分析•TEMP温度设置第二章集成电路制作工艺集成电路加工过程中的薄膜:(P15)热氧化膜、电介质层、外延层、多晶硅、金属薄膜。

第四章逻辑模拟§1.逻辑模拟原理•逻辑模拟是在计算机上建立数字电路模型并使该模型运行的一种过程,这里“运行”的意思是针对某一外加的输入序列激励,计算模型电路中随时间变化的各个响应的信号值。

逻辑模拟的主要用途①评价新的设计。

逻辑设计者首要的任务是检验逻辑的正确性,在满足逻辑功能的基础上,根据时间关系、信号传播特性或通过模拟获得有关电路的竞争、冒险和电路振荡条件的资料。

②分析故障。

用一个给定的测试序列分析可监测的故障,包括在规定的故障条件下的电路工作特性,以及对于给定的测试序列可获得怎样的故障分辨率等等。

冒险•对于单个逻辑信号,由于延迟的原因,组合电路可能产生瞬态错误或尖峰脉冲,称为冒险。

竞争•对于多路信号,在若干信号同时改变时会引起竞争。

在竞争的条件下,电路的动作取决于信号变化的实际次序。

逻辑模拟的分级•逻辑模拟可分为三级:“门”级;“功能”级和“寄存器”级。

•门级模拟与功能级模拟主要用于检查逻辑设计的正确性和故障分析;寄存器级模拟主要用于检查指令操作时间表。

门级模拟•门级模拟的基本部件包含与门、或门、非门、与非门及或非门等,门级模拟也包含一些触发器等基本寄存部件,是数字电路中最低一级的逻辑元件的模拟。

门级模拟一般在逻辑设计基本完成以后进行,主要目的是检查逻辑和时序的正确性。

功能级模拟•功能级模拟允许一些功能块作为模拟的基本部件,包括加法器、计数器、编译码器等,模拟的主要目的是检查逻辑的正确性。

功能级模拟要求功能部件内部的逻辑电路是详细的和准确无误的。

寄存器级模拟•寄存器级模拟不需要详细的逻辑细节,只要编译操作表或用寄存器传输语言描述即可进行模拟。

寄存器级模拟主要是检查所设计的各条指令的流程及其在相关寄存器中传输的情况。

所以寄存器级模拟主要用于检查指令操作表的正确性。

逻辑模拟系统可用精确性、有效性、通用性来评价①精确性指信号值与时间的关系必须严格对应于实际电路所呈现的关系;②有效性指模拟过程有效而成本低;③通用性指程序能够处理各种各样的逻辑电路。

集成电路设计基础总结《集成电路设计基础》分为两大部分。

第一部分介绍集成电路的制造材料、基本制造工艺、无源和有源器件相关的工艺流程、MOSFET特性、采用SPICE的集成电路模拟、集成电路版图设计、集成电路的测试与封装、第二部分介绍CMOS 基本电路、静态恢复逻辑电路、静态传输逻辑电路、动态恢复逻辑时序电路、模拟集成电路与模数混合电路。

本书介绍了集成电路设计的基础内容,直观、严密地阐述了各种集成电路设计的基本原理和概念;同时,由浅入深地提供了大量设计实例供读者学习。

全书共分9章,第1章对集成电路的发展、分类、设计与制造作了概述。

第2章介绍半导体物理基础。

第3章介绍半导体器件模型。

第4章介绍集成电路制造、版图设计和封装。

第5章介绍模拟单元与变换电路。

第6章介绍数字单元电路设计。

第7章介绍ASIC/SoC系统设计。

第8章介绍集成电路测试与可测试性设计。

第9章介绍集成电路设计工具,并以LCD 控制器作为设计实例。

《集成电路设计基础》作为集成电路设计的基础教材,注重相关理论、结论和知识的应用,可供与集成电路设计领域相关的各电类专业的高年级本科生和研究生使用,也可供这一领域的工程技术人员自学和参考。

本书前面部分主要是对集成电路发展概况的介绍,然后是对半导体的介绍,mos模型的介绍,集成工艺介绍。

详细章节如下:第1章绪论第2章半导体物理基础第3章半导体器件模型第5章模拟单元与变换电路第6章数字单元电路第7章 ASIC/SoC系统设计第8章集成电路测试与可测试性设计第9章集成电路设计工具与设计实例本书是一本优秀的模拟集成电路分析与设计教材,它以直观的角度、严密的思维逻辑,阐述了各种模拟电路的基本原理和概念,同时还讨论了该领域中出现的新问题及新的技术发展。

全书论述清晰,重点突出,实用性强,将理论与实际结合,提供了大量现代工业中的设计实例,介绍了许多实用的设计技巧,是从事这一领域的工程技术人员必备的参考书。

虽然在许多应用上,数字电路确实已经取代了大量模拟电路。