版图设计和制作工艺

- 格式:doc

- 大小:151.50 KB

- 文档页数:8

针对SOI 集成传感器芯片结构的特殊性,同时考虑到芯片成品率和器件的可靠性,根据已经开发的普通压阻工艺规则、考虑到光刻和键合设备能力、同时为保证加速度传感器件结构布线的需求制定了集成传感器芯片的工艺规则。

为保证结构加工的成品率,加速度传感器弹性支撑悬臂梁的厚度设计为30um 。

考虑到整个器件的尺寸、加速度传感器的量程等诸多因素,加速度传感器支撑悬臂梁的宽度必须比较小;但为保证在一条弹性悬臂梁的宽度范围内并排放下两个压阻和六条金属导线,同时又要将图形尺寸设计的足够大,以尽可能减少加工偏差对图形尺寸影响的比例,以获得较高的成品率和可靠性。

综合考虑以上因素,布线的工艺规则以5um 为最小图形线宽和间隔、压阻图形面引线孔覆盖最小为2um 、双面光刻和对准键合的图形覆盖最小为4um ,其他还要求器件的焊盘最小间距大于100um 、焊盘面积大于100100um um 、硅片划片槽宽度为200um 。

MEMS 光刻掩模版介绍光刻技术是一种将掩模版的图形转移到衬底表面的图形复制技术,即利用光源选择性照射光刻胶层使其化学性质发生改变,然后显影去除相应的光刻胶得到相应图形的过程。

光刻得到的图形一般作为后续工艺的掩模,进一步对光刻暴露的位置进行选择性刻蚀、注入或者淀积等。

MEMS 掩模版是一块单面附有金属铬层的厚度为c 的石英玻璃平板,掩模图案构造于铬层中。

光刻掩模版的制作是MEMS 器件加工流程的开始。

一般对掩模版的设计要求为:图形的尺寸要准确;图形边缘应光洁,陡直和无毛刺;图形黑白对比要深,图形内无针孔,图形外无黑点;整套版中的各块能一一套准;底版要牢固、耐磨;各图形区内应有掩蔽作用,图形区外应完全透过紫外光或对光吸收极少。

根据制定的集成传感器的工艺规则,结合需要的MEMS 器件结构,就可以开始进行MEMS 掩模版的版图设计。

版图是一组具有一定对应关系的图形,它与器件的结构、所用的加工工艺密切相关,每层版图都对应于不同的工艺步骤。

版图工艺课程设计一、课程目标知识目标:1. 学生能理解版图工艺的基本概念,掌握版画制作的步骤和技巧。

2. 学生能了解版画的历史发展,认识到版画在艺术领域的价值。

3. 学生掌握至少两种版画制作方法,并能够运用所学知识创作出自己的版画作品。

技能目标:1. 学生能够独立完成版画作品的构思、设计和制作过程,提高动手操作能力。

2. 学生通过版画创作,培养观察力、想象力和创造力,提高审美素养。

3. 学生能够运用版画技法,表达自己的思想感情,提高艺术表现力。

情感态度价值观目标:1. 学生通过学习版图工艺,培养对传统文化的尊重和热爱,增强民族自豪感。

2. 学生在版画创作过程中,学会合作与分享,培养团队精神和沟通能力。

3. 学生通过版画作品的创作与展示,增强自信心,树立正确的审美观念。

课程性质:本课程旨在让学生了解和掌握版画的基本知识、技巧和创作方法,培养他们的动手能力、观察力、想象力和创造力。

学生特点:六年级学生具有一定的手工制作基础和审美能力,对新鲜事物充满好奇心,善于表达自己的观点。

教学要求:结合学生特点,注重实践操作,鼓励学生大胆尝试,激发创作潜能,提高学生的艺术素养和综合素质。

在教学过程中,关注学生的个体差异,因材施教,确保每个学生都能在课程中收获成长。

通过课程目标的分解,使学生在学习过程中达到预期的学习成果,为后续的教学设计和评估提供依据。

二、教学内容1. 版图工艺基础知识:版画的定义、分类及其历史发展,版画的基本制作工具和材料。

2. 版画制作技巧:介绍木版画、纸版画两种制作方法,包括刻板、印刷、色彩搭配等技巧。

3. 版画创作实践:引导学生进行版画创作,包括构思、设计、制作和展示等环节。

4. 艺术鉴赏与评价:分析经典版画作品,学会从形式、内容、技法等方面进行鉴赏和评价。

教学大纲安排:第一课时:版图工艺基础知识学习,了解版画的起源、发展及分类。

第二课时:版画制作工具和材料认识,学习木版画制作技巧。

第三课时:木版画创作实践,指导学生完成木版画作品。

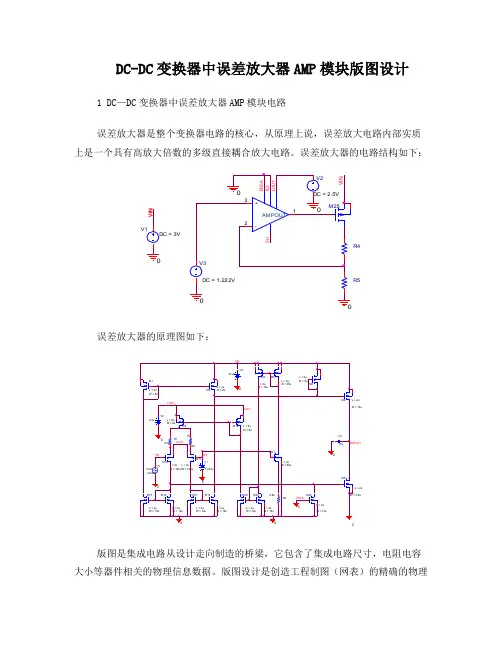

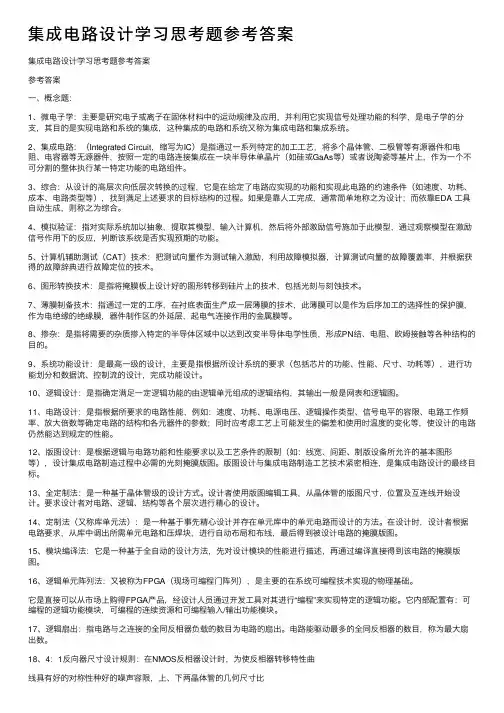

DC-DC 变换器中误差放大器AMP 模块版图设计1 DC —DC 变换器中误差放大器AMP 模块电路误差放大器是整个变换器电路的核心,从原理上说,误差放大电路内部实质上是一个具有高放大倍数的多级直接耦合放大电路。

误差放大器的电路结构如下:V I NR40V1DC = 3VR5误差放大器的原理图如下:L = 2u版图是集成电路从设计走向制造的桥梁,它包含了集成电路尺寸,电阻电容大小等器件相关的物理信息数据。

版图设计是创造工程制图(网表)的精确的物理描述过程,即定义各工艺层图形的形状,尺寸以及不同工艺层的相对位置的过程。

其设计目标有以下三方面:1. 满足电路功能,性能指标,质量要求;2. 尽可能节省面积,以提高集成度,降低成本;3. 尽可能缩短连线,以减少复杂度,缩短延时,改善可能性。

下面是我对误差放大器AMP模块版图设计及仿真的过程。

2DC—DC变换器中误差放大器AMP模块版图设计及仿真2.1版图设计的前仿真2.1.1替换及其他基本设置此次版图所用工艺为MOSIS/ORBIT 1.2u SCNA。

(设置替换路径为:C:\program files\Tanner EDA\Tanner Tools v13.1\L-Edit andLVS\Tech\Mosis\morbn12)替换设置后,将设置-设计-technology下的technology to micro map 改为:1 Lambda=microns。

2.1.2版图的基本绘制下面为常用的CMOS工艺版图与工艺的关系:(1)N阱:做N阱的封闭图形处,窗口注入形成P管的衬底(2).有源区:做晶体管的区域(G,D,S,B区),封闭图形处是氮化硅掩蔽层,该处不会长场氧化层(3).多晶硅:做硅栅和多晶硅连线。

封闭图形处,保留多晶硅。

(4).有源区注入:P+,N+区。

做源漏及阱或衬底连接区的注入(5).接触孔:多晶硅,扩散区和金属线1接触端子。

(6).金属线1:做金属连线,封闭图形处保留铝(7).通孔:两层金属连线之间连接的端子(8).金属线2:做金属连线,封闭图形处保留铝①NMOS与PMOS的绘制绘制NMOS要用到的图层有Active、N Select、Poly、Active Contact、Metal1,而PMOS管的版图绘制需要用到N Well、Active、P Select、Poly、Active Contact、Metal1,其中Poly的长度就是晶体管的L,Active的高度就是晶体管的W。

集成电路设计学习思考题参考答案集成电路设计学习思考题参考答案参考答案⼀、概念题:1、微电⼦学:主要是研究电⼦或离⼦在固体材料中的运动规律及应⽤,并利⽤它实现信号处理功能的科学,是电⼦学的分⽀,其⽬的是实现电路和系统的集成,这种集成的电路和系统⼜称为集成电路和集成系统。

2、集成电路:(Integrated Circuit,缩写为IC)是指通过⼀系列特定的加⼯⼯艺,将多个晶体管、⼆极管等有源器件和电阻、电容器等⽆源器件,按照⼀定的电路连接集成在⼀块半导体单晶⽚(如硅或GaAs等)或者说陶瓷等基⽚上,作为⼀个不可分割的整体执⾏某⼀特定功能的电路组件。

3、综合:从设计的⾼层次向低层次转换的过程,它是在给定了电路应实现的功能和实现此电路的约速条件(如速度、功耗、成本、电路类型等),找到满⾜上述要求的⽬标结构的过程。

如果是靠⼈⼯完成,通常简单地称之为设计;⽽依靠EDA ⼯具⾃动⽣成,则称之为综合。

4、模拟验证:指对实际系统加以抽象,提取其模型,输⼊计算机,然后将外部激励信号施加于此模型,通过观察模型在激励信号作⽤下的反应,判断该系统是否实现预期的功能。

5、计算机辅助测试(CAT)技术:把测试向量作为测试输⼊激励,利⽤故障模拟器,计算测试向量的故障覆盖率,并根据获得的故障辞典进⾏故障定位的技术。

6、图形转换技术:是指将掩膜板上设计好的图形转移到硅⽚上的技术,包括光刻与刻蚀技术。

7、薄膜制备技术:指通过⼀定的⼯序,在衬底表⾯⽣产成⼀层薄膜的技术,此薄膜可以是作为后序加⼯的选择性的保护膜,作为电绝缘的绝缘膜,器件制作区的外延层,起电⽓连接作⽤的⾦属膜等。

8、掺杂:是指将需要的杂质掺⼊特定的半导体区域中以达到改变半导体电学性质,形成PN结、电阻、欧姆接触等各种结构的⽬的。

9、系统功能设计:是最⾼⼀级的设计,主要是指根据所设计系统的要求(包括芯⽚的功能、性能、尺⼨、功耗等),进⾏功能划分和数据流、控制流的设计,完成功能设计。

集成电路版图设计什么是集成电路版图设计?所谓的集成电路版图设计是根据逻辑与电路功能和性能要求以及工业水平要求来设计芯片制造时光刻用的掩模版图,实现IC设计的最终输出其中版图是一组相互套合的图形,各层版图表示不同的工艺步骤,每层版图用不同的图案表示。

DRS和LVS开始前需要做哪些准备?DRC开始前需要准备好版图文件和DRC规则文件,LVS开始前需要准备好版图文件、电路图文件和runset文件为什么需要进行版图数据处理?在形成整体的版图并通过DRC、LVS的验证后,版图设计过程就完成了,但这个时候的版图GDS数据还不能拿去制作掩模版,还需要对GDS数据进行处理。

该版图GDS数据中的层次跟最终模板的层次并不是完全一致的,该版图GDS 数据还需要进行工艺涨缩处理,以满足掩模版制作需求。

集成电路设计流程:功能要求、电路设计、电路仿真、版图设计、版图验证、后仿及优化。

光刻工艺流程:底膜处理、涂胶、前烘、曝光、显影、坚膜、显影检测、刻蚀、去胶、最终检验。

工艺要求:特征尺寸、集成度、晶圆尺寸工艺文件夹包含:技术文件、显示文件DRC步骤:建立DRC运行目录、修改规则文件、导出gds2文件、编译规则文件、执行DRC检查、DRC结构分析狗骨电阻的优点:能够控制电流走向,使电阻误差减小。

集成电路发展的趋势是什么?制程工艺越来越精细、集成度越来越高、电路功能越来越强大、越来越趋向于智能化集成电路中的电阻分为哪几种?有扩散电阻、多晶硅电阻、阱电阻简述为什么尽可能多地设计阱接触?能大大减小寄生电阻的阻值,有效抑制闩锁。

在绘制PMOS版图时,为什么在接触区域进行SN注入?SN注入降低了接触电阻,接触孔容易刻蚀,形成欧姆接触。

简述什么是闩锁效应?闩锁效应是CMOS工艺所特有的寄生效应,严重会导致电路的失效,甚至烧毁芯片。

什么是保护环,保护环的主要作用?能抑制闩锁效应的设计方式就是保护环作用: 1.阻碍少子保护环 2.载流子注入类型为少子 3.保护类型为少子 4.电位保持PN结反偏 5.起分流作用。

一、0.18 RF 工艺版图设计技巧by 河马绘制版图前,格点统一到0.005um,不在万不得已的情况下除了连接线都以pcell的形式提交你绘制的版图,禁止flatten. 模块尽量方形或长方形,不要太狭长。

互相借鉴,统一到最好的风格。

模拟部分:1:不要像以前那样为了省面积,把同源或同漏的无关的两个管子的源或漏迭起来。

finger 的除外。

2:同一个地方往上打via, via尽量从同一处直线往上叠加,不要错开。

注意别遗漏某层via,否则查起来会比较难。

3: MET1除了连接有源区和poly,尽量不要走线,尽量用MET2和MET3走线,MET2竖为主横为辅,MET3尽量只走横。

MET4,MET5少量使用,主要到最后走VDD,VSS,MET6主要用于电感电容和RF的走线。

4:相邻层次的MET交迭区域在可变动的情况下越小越好。

5:MET1禁止从gate和电阻上跨过。

MET2最好也不要跨。

6:信号连接点在各支路的汇合位置。

7:源和衬底相连的尽量不用MET1直接连。

两个的接点其实远点对噪声的干扰小。

8:MIM电容选择性地可以加在一些不敏感的电路上以节省面积。

差分对管上禁止盖MIM 电容。

9:大的功能模块间要做多圈隔离。

(如:VSS-VDD-VSS)10:不要把面积问题放在首位,首先要考虑性能。

但是要匹配的电路或器件,如电流镜和输入对管等距离越近越好。

11:需要在不同PWELL的N管可以公用一个DNW,用NWELL隔离成小格子。

RF部分:1:模块的输入和输出必须用MET6走线,布线尽量用MET5,MET4.再往下最好别走线。

2:MIM电容下,RF电阻上不要有任何其他东西3:走线就近原则,两点之间的连线不要舍近求远,尽量选取最短路径。

走线以水平、垂直以及45度斜线为主。

4:相同的电路画一份然后拷贝,做到走线方式,长度,位置都完全一样。

5:有些电容和电阻可以合并在一个DNW里,画前仔细推敲,以便让相关器件靠得尽量近,也节省了面积。

针对SOI 集成传感器芯片结构的特殊性,同时考虑到芯片成品率和器件的可靠性,根据已经开发的普通压阻工艺规则、考虑到光刻和键合设备能力、同时为保证加速度传感器件结构布线的需求制定了集成传感器芯片的工艺规则。

为保证结构加工的成品率,加速度传感器弹性支撑悬臂梁的厚度设计为30um 。

考虑到整个器件的尺寸、加速度传感器的量程等诸多因素,加速度传感器支撑悬臂梁的宽度必须比较小;但为保证在一条弹性悬臂梁的宽度范围内并排放下两个压阻和六条金属导线,同时又要将图形尺寸设计的足够大,以尽可能减少加工偏差对图形尺寸影响的比例,以获得较高的成品率和可靠性。

综合考虑以上因素,布线的工艺规则以5um 为最小图形线宽和间隔、压阻图形面引线孔覆盖最小为2um 、双面光刻和对准键合的图形覆盖最小为4um ,其他还要求器件的焊盘最小间距大于100um 、焊盘面积大于100100um um 、硅片划片槽宽度为200um 。

MEMS 光刻掩模版介绍

光刻技术是一种将掩模版的图形转移到衬底表面的图形复制技术,即利用光源选择性照射光刻胶层使其化学性质发生改变,然后显影去除相应的光刻胶得到相应图形的过程。

光刻得到的图形一般作为后续工艺的掩模,进一步对光刻暴露的位置进行选择性刻蚀、注入或者淀积等。

MEMS 掩模版是一块单面附有金属铬层的厚度为c 的石英玻璃平板,掩模图案构造于铬层中。

光刻掩模版的制作是MEMS 器件加工流程的开始。

一般对掩模版的设计要求为:图形的尺寸要准确;图形边缘应光洁,陡直和无毛刺;图形黑白对比要深,图形内无针孔,图形外无黑点;整套版中的各块能一一套准;底版要牢固、耐磨;各图形区内应有掩蔽作用,图形区外应完全透过紫外光或对光吸收极少。

根据制定的集成传感器的工艺规则,结合需要的MEMS 器件结构,就可以开始进行MEMS 掩模版的版图设计。

版图是一组具有一定对应关系的图形,它与器件的结构、所用的加工工艺密切相关,每层版图都对应于不同的工艺步骤。

在加工过程中,各层版图利用十字对准标记进行光刻对准,以保证对准精度。

MEMS 掩模版的制作是根据设计完成的版图来进行的。

集成传感器的版图设计说明

课题工艺流程设计首先必须考虑集成传感器的结构要求,由于集成传感器需要集成两种不同的传感器,因此在工艺流程设计中不但要求考虑单个传感器的制作,还要考虑各个传感器的工艺兼容性,同时根据三种传感器的结构尽量安排兼容性的工艺步骤,以减少工艺流程的复杂性和成本。

集成传感器中可以兼容的工艺步骤包括:在器件正面分布的两种传感器浮雕式敏感电阻的制作;在器件背面的加速度传感器质量块和支撑膜的制作;加速度传感器支撑基底的制作等。

同时课题工艺流程设计还必须考虑器件结构的可加工性、成品率和一致性的要求,以适应器件进一步工程化的需求。

因此在芯片工艺的研发过程中,从工艺原理和器件工作原理和结构特点出发,对器件工艺要求、指标进行了综合分析,经过工艺流程和版图设计的优化,确定了三轴加速度和温度集成传感器的工艺流程。

集成传感器采用SOI硅片,整个工艺流程公用8块掩模版,分别为P+欧姆接触版(M1)、敏感电阻版(M2)、背腔版1(M3)、背腔版2(M4)、引线孔版(M5)、金属引线版(M6)、正面穿透版(M7)和玻璃金属电极版(M8)。

其中P+欧姆接触版(M1)实现集成传感器中敏感电阻与金属引线的欧姆接触区,以及温度传感器温敏电阻的硼离子掺杂;敏感电阻版(M2)是负版,实现集成传感器中各个浮雕式敏感电阻;背腔版1(M3)和背腔版2(M4)用来实现加速度传感器质量块和悬臂梁;引线孔版(M5)实现敏感电阻与金属引线的接触孔定义;金属引线版(M6)用来完成器件间各个部分的电信号的互联,以形成完整的电路;正面穿透版(M7)用来形成加速度传感器的四个支撑悬臂梁;

本集成传感器利用Tanner L-Edit设计软件进行版图设计,版图设计完成后,即可交付用于制作光刻掩模版。

集成传感器的工艺流程

(1)使用HF溶液,清洗硅片。

(2)硅片的压敏电阻P-区硼掺杂至需要的浓度,具体过程为:硅片表面进

行热氧化工艺(厚度

500A)以提高离子注入均匀性;SOI硅片的器

件层进行硼离子注入,获得p型掺杂,注入能量为80keV,注入剂量为142

310cm-

⨯;注入杂质再分布的阱推(drive-in)扩散退火过程,退火温度1100℃,时间为1.5小时。

为了保证所需要的杂质浓度,同时

保证在整个SOI 器件层中的杂质浓度均匀分布,注入过程采用氮气环境。

(3) 在金属接触区硼离子注入,形成P+区域,其具体过程为:利用P+欧

姆接触版,光刻M1区;再次硼离子注入,注入剂量为1621.510cm -⨯,注入能量为80keV ,以形成低阻的欧姆接触区和温度传感器的温敏电阻区,扩散退火的过程则利用下一步工艺步骤中的热氧化制备2SiO 层的工艺条件来完成,2SiO 热氧化的工艺条件:温度1000℃,时间60分钟。

(4) 利用P-敏感电阻版,光刻形成M2电阻图形;感应耦合等离子刻蚀技

术(ICP )刻蚀其余区域的Si 器件层至2SiO 绝缘层,以形成集成传感器的浮雕式电阻,刻蚀厚度为1.65um 。

然后通过热氧化工艺制备一层厚度为0

4000A 的2SiO 层,然后在这层2SiO 膜上面,使用低压化学气相沉积(LPCVD )工艺交错制备两层034Si N (1100A)和一层

02SiO (2500A)复合薄膜,

作为接下来两次KOH 湿法腐蚀形成加速度质量块运动间隙腐蚀的掩模层,其中的热氧化工艺制作的2SiO 层还可以作为34Si N 薄膜的应力缓冲层。

2SiO 热氧化工艺的条件:温度

1000℃,时间60分钟,这步热氧化工艺不但能利用硼离子杂质分凝提高电阻值以保证器件输出幅度,而且不影响杂质分布保证器件温度特性,同时能激活P+注入区。

(5) 利用背腔版1,背面光刻,刻蚀背面第一层2SiO 和34Si N ,形成M3

区(加速度传感器的悬臂梁区)的第一次KOH 腐蚀的掩模层;然后利用背腔版2,再次背面光刻,刻蚀背面第二层2SiO 和34Si N ,形成M4区(加速度传感器质量块的运动间隙区)的第二次KOH 腐蚀的掩模层;34Si N 和2SiO 复合薄膜刻蚀过程中,RIE 刻蚀背面34Si N 层,BHF 溶液刻蚀背面2SiO 层。

(6) 背面第一次KOH 各向异性腐蚀,形成集成传感器的背腔:硅膜支撑

的加速度传感器活动质量块,背面腐蚀的深度为420um 。

(7) 34H PO 腐蚀背面一层34Si N 层,温度为150℃;BHF 腐蚀背面这层34

Si N 下面的2SiO 层,然后进行背面第二次KOH 各向异性腐蚀,形成质量块与键合玻璃之间的运动间隙为 4.404r um 。

(8) 利用引线孔版,正面光刻M5区,刻蚀正面2SiO 和34Si N 膜。

(9) 在硅片正面物理气相沉积00

(PVD)Ti/Al(1000A/15000A)层;利用金属

引线版,正面光刻M6金属图形,ICP 刻蚀金属形成器件的金属引线;最后在500℃条件下进行合金化过程。

(10) 利用正面穿透版,光刻M7区,ICP 深刻蚀加速度传感器的支撑硅膜,

以形成加速度传感器四个单臂支撑悬臂梁结构。

(11) 硅/玻璃静电结合。

(12) 采用金刚石刀片沿事先保留的划片槽对整个圆片进行划片,形成单

个管芯。

(13) 为进一步释放、缓解集成传感器芯片在加工过程中的残余应力(包

括:机械应力、薄膜内应力、热应力等),采用低温退火工艺进行处理,温度180℃,持续时间为48小时。

最后采用陶瓷材料双列直插形式管壳进行封装。