集成电路工艺和版图设计 参考

- 格式:ppt

- 大小:5.48 MB

- 文档页数:89

第9章集成电路版图设计实例【习题答案】1.版图设计关于数字地和模拟地的考虑事项是什么?答:一般的模拟集成电路中,通常既有数字信号又有模拟信号,数字信号和模拟信号之间容易发生干扰。

在版图设计过程中,还要考虑地噪声对电路的影响。

即在整体版图的设计中,需着重考虑电路噪声问题,按照尽量降低噪声的原则进行电路的整体布局。

首先,在总体版图的布局上,尽量将数字部分远离模拟部分,如果总体电路中模拟部分偏多,则在版图设计中将数字部分放在靠边的位置,而且把模拟部分中最容易被数字干扰的部分放到离数字部分最远的位置,同时在数字部分和模拟部分中间用接地的衬底接触来进行隔离,反之亦然。

其次,采用隔离环设计,对每个单元模块都用一层接地的衬底接触,一层接电源的N阱构成的隔离环来进行隔离。

对于整个模拟部分和数字也分别采用相同的隔离环隔离,数字电路的隔离环可以吸收数字电路的衬底噪声,从而可以减少通过衬底串扰到模拟电路的衬底噪声。

隔离环包的层数越多,理论上吸收衬底噪声效果越好。

但是要避免数字电路的p隔离环紧靠模拟电路的p型隔离环,因为在这种情况下数字地的噪声会串扰到模拟地。

从而使模拟地受到干扰。

最后,除了数字模块之外的其它单元模块尽量将距离缩短,这样一方面能尽量地减少互连线经过别的区域引入噪声,同时也能降低引线过长引起电压信号的衰减。

2.总结自己的版图设计技巧和经验。

3. 共质心MOS管设计时的注意事项是什么?答:低精度要求可采用一维共质心,高精度要求必须采用二维共质心。

共质心设计时需保证MO管的对称性和电流通路的对称性。

4. 静电保护的种类以及版图设计注意事项。

答:常用的二极管式的静电保护分为两种方式,一种是用MOS晶体管连接成二极管形式的静电保护,一种利用CMOS工艺中二极管的静电保护。

在MOS型静电保护版图设计中,主要考虑以下几点:●MOS管要分成多个管,叉指结构,以便形成多支路共同放电。

●因为放电瞬间流经MOS管的电流特别大,构成整个放电通路的任何导线的宽度一定要有足够保证,而且CMOS工艺对于每个接触孔能通过的电流密度还有要求,因此还要保证放电通路导线上孔的数目应尽量多。

第三章集成电路版图设计每一个电路都可以做的很完美,对应的版图也可以画的很艺术,需要的是耐心和细心,当然这需要知识,至少我这么认为。

3.1认识设计规则(design rule)什么是设计规则?根据实际工艺水平(包括光刻精度、刻蚀能力、对准容差等)和成品率要求,给出的一组同一工艺层及不同工艺层之间几何尺寸的限制,主要包括线宽、间距、覆盖、露头、凹口、面积等规则,分别给出它们的最小值,以防止掩膜图形的断裂、连接和一些不良物理效应的出现。

芯片上每个器件以及互连线都占有有限的面积。

它们的几何图形形状由电路设计者来确定。

(从图形如何精确地光刻到芯片上出发,可以确定一些对几何图形的最小尺寸限制规则,这些规则被称为设计规则)制定设计规则的目的:使芯片尺寸在尽可能小的前提下,避免线条宽度的偏差和不同层版套准偏差可能带来的问题,尽可能地提高电路制备的成品率。

设计规则中的主要内容:Design Rule通常包括相同层和不同层之间的下列规定:最小线宽 Minimum Width最小间距 Minimum Spacing最小延伸 Minimum Extension最小包围 Minimum Enclosure 最小覆盖 Minimum Overlay集成电路版图设计规则通常由集成电路生产线给出,版图设计者必须严格遵守!!!3.2模拟集成电路版图设计中遵从的法则3.2.1电容的匹配对于IC layout工程师来说正确地构造电容能够达到其它任何集成元件所不能达到的匹配程度。

下面是一些IC版图设计中电容匹配的重要规则。

1)遵循三个匹配原则:它们应该具有相同方向、相同的电容类型以及尽可能的靠近。

这些规则能够有效的减少工艺误差以确保模拟器件的功能。

2)使用单位电容来构造需要匹配的电容,所有需要匹配的电容都应该使用这些单位电容来组成,并且这些电容应该被并联,而不是串联。

3)使用正方块电容,并且四个角最好能够切成45度角。

周长变化是导致不匹配的最主要的随机因素,周长和面积的比值越小,就越容易达到高精度的匹配。

《集成电路工艺与版图设计》课堂作业班级:电子科学与技术01班姓名:曾海学号:201031722、3、4输入异或门版图设计如下:一、二输入异或门:(1)原理图:<2>L-edit中进行设计的如下二输入或非门版图<3>提取后在T-SPICE中进行参数及输入输出设置如下:VA A GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off=0)VB B GND BIT ({0010} pw=20N lt=10N ht=10N on=5 off=0)Vdd Vdd GND 5.tran 10N 100N.print tran v(OUT) v(A) v(B)<4>在W-EDIT中得到仿真波形图:二、三输入或非门<1>三输入异或门版图<3>参数及输入输出设置VA A GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off=0) VB B GND BIT ({0010} pw=20N lt=10N ht=10N on=5 off=0)Vdd Vdd GND 5.tran 10N 100N.print tran v(OUT) v(A) v(B)<3>仿真图三、四输入或非门<1>版图设计<2>参数及输入输设置Vdd Vdd GND 5VA A GND BIT ({1001} pw=20N lt=10N ht=10N o n=5 off=0)VB B GND BIT ({1010} pw=20N lt=10N ht=10N o n=5 off=0)VC C GND BIT ({1011} pw=20N lt=10N ht=10N o n=5 off=0)VD D GND BIT ({1011} pw=20N lt=10N ht=10N o n=5 off=0).tran 20N 100N.print tran v(OUT) v(A) v(B) v(C) v(D)<3>仿真图4、版图设计总结(1)本次设计中,由仿真图可以看出,仿真波形不是标准的方波图形,而是有相应的误差,可能是由于版图的设计中,布线或器件的放置不合理导致的。

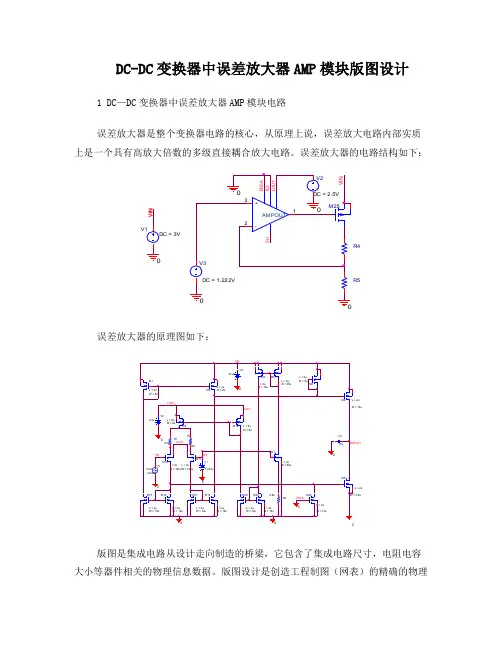

DC-DC 变换器中误差放大器AMP 模块版图设计1 DC —DC 变换器中误差放大器AMP 模块电路误差放大器是整个变换器电路的核心,从原理上说,误差放大电路内部实质上是一个具有高放大倍数的多级直接耦合放大电路。

误差放大器的电路结构如下:V I NR40V1DC = 3VR5误差放大器的原理图如下:L = 2u版图是集成电路从设计走向制造的桥梁,它包含了集成电路尺寸,电阻电容大小等器件相关的物理信息数据。

版图设计是创造工程制图(网表)的精确的物理描述过程,即定义各工艺层图形的形状,尺寸以及不同工艺层的相对位置的过程。

其设计目标有以下三方面:1. 满足电路功能,性能指标,质量要求;2. 尽可能节省面积,以提高集成度,降低成本;3. 尽可能缩短连线,以减少复杂度,缩短延时,改善可能性。

下面是我对误差放大器AMP模块版图设计及仿真的过程。

2DC—DC变换器中误差放大器AMP模块版图设计及仿真2.1版图设计的前仿真2.1.1替换及其他基本设置此次版图所用工艺为MOSIS/ORBIT 1.2u SCNA。

(设置替换路径为:C:\program files\Tanner EDA\Tanner Tools v13.1\L-Edit andLVS\Tech\Mosis\morbn12)替换设置后,将设置-设计-technology下的technology to micro map 改为:1 Lambda=microns。

2.1.2版图的基本绘制下面为常用的CMOS工艺版图与工艺的关系:(1)N阱:做N阱的封闭图形处,窗口注入形成P管的衬底(2).有源区:做晶体管的区域(G,D,S,B区),封闭图形处是氮化硅掩蔽层,该处不会长场氧化层(3).多晶硅:做硅栅和多晶硅连线。

封闭图形处,保留多晶硅。

(4).有源区注入:P+,N+区。

做源漏及阱或衬底连接区的注入(5).接触孔:多晶硅,扩散区和金属线1接触端子。

(6).金属线1:做金属连线,封闭图形处保留铝(7).通孔:两层金属连线之间连接的端子(8).金属线2:做金属连线,封闭图形处保留铝①NMOS与PMOS的绘制绘制NMOS要用到的图层有Active、N Select、Poly、Active Contact、Metal1,而PMOS管的版图绘制需要用到N Well、Active、P Select、Poly、Active Contact、Metal1,其中Poly的长度就是晶体管的L,Active的高度就是晶体管的W。

集成电路版图与⼯艺课程设计之⽤CMOS实现Y=AB+C电路与版图1 绪论1.1 设计背景集成电路设计(Integrated circuit design, IC design),亦可称之为超⼤规模集成电路设计(VLSI design),是指以集成电路、超⼤规模集成电路为⽬标的设计流程。

集成电路设计涉及对电⼦器件(例如晶体管、电阻器、电容器等)、器件间互连线模型的建⽴。

所有的器件和互连线都需安置在⼀块半导体衬底材料之上,这些组件通过半导体器件制造⼯艺(例如光刻等)安置在单⼀的硅衬底上,从⽽形成电路。

近些年来,集成电路技术发展迅猛,促使半导体技术不断地发展,半导体技术正在进⼊将整个系统整合在单⼀晶⽚上的时代。

故对VLSI的版图设计的要求也越来越⾼。

Tanner软件可提供完整的集成电路设计环境,帮助初学者进⼊VLSI设计领域。

本设计采⽤Tanner Tools Pro ⼯具,对逻辑为Y=AB+C进⾏电路设计与仿真、版图设计与仿真,在报告中给出电路图、版图与仿真结果。

1.2 设计⽬标设计⽬标逻辑:Y=AB+C⽤CMOS⼯艺设计逻辑为Y=AB+C的电路和版图。

因为CMOS是天然的反逻辑输出,所以需要先设计出逻辑为/Y=/(AB+C)的电路,再将输出接⼊⼀个CMOS反相器实现逻辑功能。

设计电路图(Schematic)时,N⽹络A与B串联且与C并联,P⽹络A与B并联且与C串联,在N和P⽹络的交界节点接⼊反相器后引出输出Y。

设计版图(Layout)时,在P型衬底(P-Sub)上进⾏制作,所以N-MOS管可以直接掺杂制作,⽽P-MOS管需要先制作⼀个N阱(N-Well),并在N阱⾥制作P-MOS管。

整个设计⽐较简单,仅仅使⽤单层⾦属布线(Meteal)。

导出电路和版图⽹表(spice)⽂件,⽤Tspice软件进⾏仿真波形,分析电路和版图是否设计正确性以及其性能如何。

在LVS验证中匹配电路原理图和版图逻辑和尺⼨匹配性,完成整个设计过程。

集成电路版图设计习题答案第2章 集成电路制造工艺【习题答案】1.硅片制备主要包括(直拉法)、(磁控直拉法)和(悬浮区熔法)等三种方法。

2.简述外延工艺的用途。

答:外延工艺的应用很多。

外延硅片可以用来制作双极型晶体管,衬底为重掺杂的硅单晶(n +),在衬底上外延十几个微米的低掺杂的外延层(n ),双极型晶体管(NPN )制作在外延层上,其中b 为基极,e 为发射极,c 为集电极。

在外延硅片上制作双极型晶体管具有高的集电结电压,低的集电极串联电阻,性能优良。

使用外延硅片可以解决增大功率和提高频率对集电区电阻要求上的矛盾。

图 外延硅片上的双极型晶体管集成电路制造中,各元件之间必须进行电学隔离。

利用外延技术的PN 结隔离是早期双极型集成电路常采用的电隔离方法。

利用外延硅片制备CMOS 集成电路芯片可以避免闩锁效应,避免硅表面氧化物的淀积,而且硅片表面更光滑,损伤小,芯片成品率高。

外延工艺已经成为超大规模CMOS 集成电路中的标准工艺。

3.简述二氧化硅薄膜在集成电路中的用途。

答:二氧化硅是集成电路工艺中使用最多的介质薄膜,其在集成电路中的应用也非常广泛。

二氧化硅薄膜的作用包括:器件的组成部分、离子注入掩蔽膜、金属互连层之间的绝缘介质、隔离工艺中的绝缘介质、钝化保护膜。

4.为什么氧化工艺通常采用干氧、湿氧相结合的方式?答:干氧氧化就是将干燥纯净的氧气直接通入到高温反应炉内,氧气与硅表面的原子反应生成二氧化硅。

其特点:二氧化硅结构致密、均匀性和重复性好、针孔密度小、掩蔽能力强、与光刻胶粘附良好不易脱胶;生长速率慢、易龟裂不宜生长厚的二氧化硅。

湿氧氧化就是使氧气先通过加热的高纯去离子水(95℃),氧气中携带一定量的水汽,使氧化气氛既含有氧,又含有水汽。

因此湿氧氧化兼有干氧氧化和en +SiO 2n -Si 外延层 n +Si 衬底水汽氧化的作用,氧化速率和二氧化硅质量介于二者之间。

实际热氧化工艺通常采用干、湿氧交替的方式进行。