IC版图设计_第三章

- 格式:ppt

- 大小:2.71 MB

- 文档页数:125

目录第1章绪论 (1)1.1版图设计基础知识 (1)1.1.1 版图设计方法 (1)1.1.2 版图设计规则 (1)1.2标准单元版图设计 (2)第2章:D触发器介绍 (6)2.1 D触发器简介 (6)2.2维持阻塞式边沿D触发器 (6)2.3真单相时钟(TSPC)动态D触发器 (7)第3章 0.35um工艺基于TSPC原理的D触发器设计 (9)3.1电路原理图设计 (9)3.2 创建 D触发器版图 (10)3.3设计规则的验证及结果 (11)第4章课程设计总结 (13)参考文献 (14)第1章绪论1.1版图设计基础知识集成电路从60年代开始,经历了小规模集成,中规模集成,大规模集成,到目前的超大规模集成。

单个芯片上已经可以制作含几百万个晶体管的一个完整的数字系统或数模混合的电子系统。

在整个设计过程中,版图(layout)设计或者称作物理设计(physical design)是其中重要的一环。

他是把每个原件的电路表示转换成集合表示,同时,元件间连接的线网也被转换成几何连线图形。

对于复杂的版图设计,一般把版图设计分成若干个子步骤进行:划分为了将处理问题的规模缩小,通常把整个电路划分成若干个模块。

版图规划和布局是为了每个模块和整个芯片选择一个好的布图方案。

布线完成模块间的互连,并进一步优化布线结果。

压缩是布线完成后的优化处理过程,他试图进一步减小芯片的面积。

1.1.1 版图设计方法可以从不同角度对版图设计方法进行分类。

如果按设计自动化程度来分,可将版图设计方法分成手工设计和自动设计2大类。

如果按照对布局布线位置的限制和布局模块的限制来分,则可把设计方法分成全定制(fullcustom)和半定制(semicustom)2大类。

而对于全定制设计模式,目前有3种CAD工具服务于他:几何图形的交互图形编辑、符号法和积木块自动布图。

对于两极运算放大器版图设计的例子,采用的是Tanner公司的LEdit软件。

这是一种广泛使用在微机上的交互图形编辑器。

第1篇引言:集成电路(IC)设计是一项复杂而精细的工作,要求设计者具备深厚的理论知识、丰富的实践经验以及出色的逻辑思维能力。

为了帮助您了解自己在IC设计领域的智力水平,我们特别设计了以下智力测试题。

请您认真作答,完成后可对自己的设计能力有一个初步的认识。

第一部分:基础知识1. 选择题- 下列哪个选项不是IC设计中所使用的制造工艺?A. CMOSB. TTLC. ECLD. LED2. 填空题- 在IC设计中,版图(Layout)是电路的__________,而原理图(Schematic)则是电路的__________。

3. 简答题- 简述CMOS工艺的基本原理。

第二部分:逻辑分析与设计1. 选择题- 下列哪个电路可以实现逻辑与功能?A. OR门B. AND门C. NOT门D. XOR门- 在组合逻辑电路中,如果某一输入变量经过不同途径传输后,到达电路中某一汇合点的时间有先有后,这种现象称为__________。

3. 简答题- 解释竞争与冒险现象,并说明如何消除它们。

第三部分:版图设计1. 选择题- 下列哪个工具常用于IC版图设计?A. Altium DesignerB. CadenceC. OrCADD. Pro/ENGINEER2. 填空题- 在版图设计中,为了防止寄生效应,通常需要将__________与__________保持一定的距离。

3. 简答题- 简述版图设计中的规则检查(DRC)和设计规则约束(DRC)。

第四部分:IC制造1. 选择题- 下列哪个步骤是IC制造过程中的关键步骤?A. 光刻B. 化学气相沉积C. 离子注入D. 刻蚀- 在IC制造中,__________是将电路图形转移到硅片上的关键步骤。

3. 简答题- 简述IC制造过程中可能遇到的问题及解决方法。

第五部分:模拟IC设计1. 选择题- 下列哪个电路属于模拟电路?A. 741运算放大器B. 555定时器C. 74LS00D. 74HC002. 填空题- 在模拟IC设计中,__________是放大信号的关键元件。

数字集成电路设计实验报告组长:李金玮14061114组员:陈久春14045101黄思佳14045102孔燕婷14045103王雨嫣14045104杨阳14045105张淼140451062016.11.10一.设计目的:1.通过本次实验,熟悉Cadence 软件的特点并掌握其使用流程和设计方法;2.了解集成电路工艺的制作流程、简单集成器件的工艺步骤、集成器件区域的层次关系,与此同时进一步了解集成电路版图设计的λ准则以及各个图层的含义和设计规则;3.掌握数字电路的基本单元CMOS 的版图,并利用CMOS 的版图设计简单的门电路,然后对其进行基本的DRC 检查;4. 掌握BC F +A =的掩模板设计与绘制。

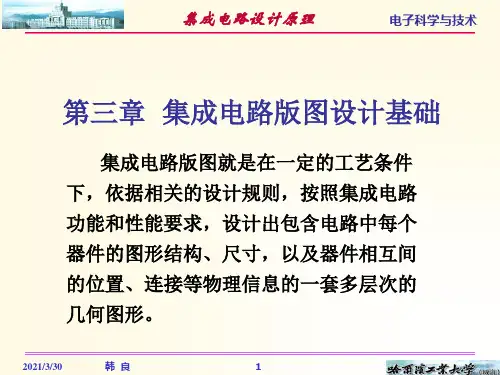

二.设计原理:1、版图设计的目标:版图 (layout ) 是集成电路从设计走向制造的桥梁,它包含了集成电路尺寸、各层拓扑定义等器件相关的物理信息数据。

版图设计是创建工程制图(网表)的精确的物理描述过程,即定义各工艺层图形的形状、尺寸以及不同工艺层的相对位置的过程。

其设计目标有以下三方面:① 满足电路功能、性能指标、质量要求;② 尽可能节省面积,以提高集成度,降低成本;③ 尽可能缩短连线,以减少复杂度,缩短延时,改善可能性。

2、版图设计的内容:①布局:安排各个晶体管、基本单元、复杂单元在芯片上的位置。

②布线:设计走线,实现管间、门间、单元间的互连。

③尺寸确定:确定晶体管尺寸(W 、L )、互连尺寸(连线宽度)以及晶体管与互连之间的相对尺寸等。

④版图编辑(Layout Editor ):规定各个工艺层上图形的形状、尺寸和位置。

⑤布局布线(Place and route ):给出版图的整体规划和各图形间的连接。

⑥版图检查(Layout Check ):设计规则检验(DRC,Design Rule Check)、电气规则检查(ERC,Electrical Rule Check)、版图与电路图一致性检验(LVS,Layout Versus Schematic )。

第三章集成电路版图设计每一个电路都可以做的很完美,对应的版图也可以画的很艺术,需要的是耐心和细心,当然这需要知识,至少我这么认为。

3.1认识设计规则(design rule)什么是设计规则?根据实际工艺水平(包括光刻精度、刻蚀能力、对准容差等)和成品率要求,给出的一组同一工艺层及不同工艺层之间几何尺寸的限制,主要包括线宽、间距、覆盖、露头、凹口、面积等规则,分别给出它们的最小值,以防止掩膜图形的断裂、连接和一些不良物理效应的出现。

芯片上每个器件以及互连线都占有有限的面积。

它们的几何图形形状由电路设计者来确定。

(从图形如何精确地光刻到芯片上出发,可以确定一些对几何图形的最小尺寸限制规则,这些规则被称为设计规则)制定设计规则的目的:使芯片尺寸在尽可能小的前提下,避免线条宽度的偏差和不同层版套准偏差可能带来的问题,尽可能地提高电路制备的成品率。

设计规则中的主要内容:Design Rule通常包括相同层和不同层之间的下列规定:最小线宽Minimum Width最小间距Minimum Spacing最小延伸Minimum Extension最小包围Minimum Enclosure最小覆盖Minimum Overlay集成电路版图设计规则通常由集成电路生产线给出,版图设计者必须严格遵守!!!3.2模拟集成电路版图设计中遵从的法则3.2.1电容的匹配对于IC layout工程师来说正确地构造电容能够达到其它任何集成元件所不能达到的匹配程度。

下面是一些IC版图设计中电容匹配的重要规则。

1)遵循三个匹配原则:它们应该具有相同方向、相同的电容类型以及尽可能的靠近。

这些规则能够有效的减少工艺误差以确保模拟器件的功能。

2)使用单位电容来构造需要匹配的电容,所有需要匹配的电容都应该使用这些单位电容来组成,并且这些电容应该被并联,而不是串联。

3)使用正方块电容,并且四个角最好能够切成45度角。

周长变化是导致不匹配的最主要的随机因素,周长和面积的比值越小,就越容易达到高精度的匹配。

一、电过应力1.ESD静电泄放(简称ESD,electrostaticdischarge )是由静电引起的一种电过应力形式,在版图设计时,一般对易损的焊盘增加特殊的保护结构来使ESD失效降至最低。

ESD是芯片制造和使用过程中最易造成芯片损坏的因素之一。

ESD产生的主要途径人体接触:带静电的人手触摸芯片机器接触:制造过程中,与机器接触自产生电荷:已封装芯片在组合或运输过程中产生电荷人体在某种环境中可以存放1.5KV~2KV的静电压,这样高的电压可产生1.3A的峰值电流,如果施以未保护的芯片的PAD上,将有可能击穿MOSFET的源漏通道或多晶硅栅。

常规IC一般要求可以承受2KV的静态电压,某些特殊IC要求承受20KV HBM的静电电压。

电压引起的破坏:介质击穿:击穿典型MOSFET的栅介质,导致栅和衬底短路。

结击穿:如果管脚连接着扩散区,那么在栅氧化层击穿之前还可能发生雪崩击穿电流引起的破坏:—薄膜层发生破裂—极大的电流密度可使金属连线移动并穿过接触,使PN结短路在集成电路版图设计中,所有的易损管脚必须有与PAD连接的ESD保护结构。

—只与MOS的栅或淀积电容电极连接的管脚极易受ESD损坏,所以在芯片的I/O PAD需特别注意ESD保护—连接到相对小扩散区的关键也容易出现ESD诱发的结损害,版图设计者一般会给这些管脚都增加ESD保护器件。

—一些特殊的管脚可以抗ESD,因此可以不加防护。

典型的功率管的管脚会与大的扩散区连接,这类管脚可以不加ESD保护电路。

2.电迁移:集成电路中电迁移是由极高的电流密度引起的缓慢的损耗现象,移动的载流子对静止的金属原子的影响引起了金属的逐渐移位。

铝的电流密度接近5X105A/cm2时,电迁移现象变得很明显。

由于金属层厚度很薄,所以在亚微米工艺中最小线宽的金属在几毫安的电流下就会出现电迁移。

电迁移引起金属原子逐渐移出,形成空隙,这使得连线的有效横截面积减小引起连线剩余部分的电流密度增大,电迁移现象更加明显并逐渐结合,最终切断连线,导致断路。

IC模拟版图课程设计一、课程目标知识目标:1. 学生能理解IC版图的基本概念,掌握版图设计的基本原理。

2. 学生能够运用所学知识,进行简单的IC模拟版图设计。

3. 学生了解版图中常见的电路元件及其符号,掌握其连接方式和布局规则。

技能目标:1. 学生能够运用专业软件进行IC模拟版图的设计与绘制。

2. 学生掌握版图设计中常见的调试方法,具备分析和解决问题的能力。

3. 学生通过实际操作,提高团队协作能力和沟通能力。

情感态度价值观目标:1. 学生培养对电子科技的兴趣,增强对IC行业的认知。

2. 学生在实践过程中,树立正确的工程观念,注重细节,追求精益求精。

3. 学生通过课程学习,培养良好的学习习惯和团队合作精神。

课程性质:本课程为实践性较强的课程,结合理论教学,使学生能够将所学知识应用于实际操作中。

学生特点:学生具备一定的电子基础知识,对IC设计有一定了解,但对版图设计较为陌生。

教学要求:教师应注重理论与实践相结合,以学生为中心,引导他们主动探究、积极实践,提高学生的动手能力和创新能力。

在教学过程中,关注学生的个体差异,提供有针对性的指导。

通过课程学习,使学生达到上述设定的知识、技能和情感态度价值观目标。

二、教学内容1. 版图设计基础理论:- 版图基本概念、版图设计流程及规范。

- 版图中常见的电路元件、符号及其连接方式。

- 版图布局规则及注意事项。

2. 版图设计实践操作:- 使用专业软件进行版图设计的基本操作。

- 简单IC模拟版图的设计与绘制。

- 版图设计中常见问题的调试与解决。

3. 教学案例分析:- 分析典型IC模拟版图案例,了解版图设计的实际应用。

- 学习优秀版图设计技巧,提高自身设计水平。

教学内容安排与进度:第一周:版图设计基础理论、软件操作介绍。

第二周:版图中常见电路元件及其连接方式、布局规则。

第三周:实际操作练习,进行简单IC模拟版图设计。

第四周:版图设计案例分析,总结经验,提高设计能力。

教材章节及内容:第一章:版图设计基础1.1 版图基本概念1.2 版图设计流程及规范1.3 版图中常见的电路元件及符号第二章:版图设计实践2.1 专业软件操作2.2 简单IC模拟版图设计2.3 版图调试与问题解决第三章:教学案例分析3.1 典型IC模拟版图案例3.2 优秀版图设计技巧教学内容确保科学性和系统性,结合实际教学需求,注重理论与实践相结合,使学生能够循序渐进地掌握版图设计相关知识。

目录目录 (1)第一章绪论 (1)1.1 版图设计 (1)1.1.1设计流程 (1)1.1.2设计步骤 (1)1.1.3 设计规则及验证 (1)1.2 标准单元版图设计 (2)1.2.1标准单元版图设计简介及历史 (2)1.2.2标准单元版图设计的意义 (2)第二章触发器介绍 (4)2.1 触发器简介 (4)2.2 主从D触发器的工作原理 (4)第三章0.35um工艺主从D触发器的设计 (6)3.1主从D触发器电路图的设计步骤及电路图 (6)3.1.1 设计步骤 (6)3.1.2 电路图 (6)3.2主从D触发器版图的设计步骤及电路图 (7)3.2.1 设计步骤 (7)3.2.2 版图 (7)3.3 DRC和LVS验证方法和结果 (8)第四章CMOS SRAM 单元介绍 (9)4.1 CMOS SRAM单元介绍 (9)4.1.1 CMOS SRAM单元原理 (9)4.1.2 CMOS SRAM单元的工作原理 (9)4.1.3 CMOS SRAM 单元的设计方法 (9)4.2 单个CMOS SRAM电路原理图 (10)第五章CMOS SRAM单元0.35um工艺版图设计 (12)5.1 单个CMOS SRAM 单元 (12)5.1.1单个CMOS SRAM 单元的设计步骤及电路图 (12)5.1.2 单个CMOS SRAM 单元的版图 (13)5.2 DRC和LVS验证方法和结果 (14)5.3 2位×8位CMOS SRAM阵列版图的设计步骤及DRC验证 (15)心得体会 (16)参考文献 (17)第一章绪论1.1 版图设计版图设计是一组相互套合的图形,各层版图相应不同的工艺步骤,每层版图用不同的图案来表示,版图与所制备的工艺密切相关。

1.1.1设计流程版图设计是创建工程制图的精确的物理描述的过程,而这一物理描述遵守由制造工艺、设计流程以及仿真显示为可行的性能要求所带来的一系列约束。

1.1.2设计步骤具体设计步骤如下:系统设计,逻辑设计,电路图设计,版图设计,版图后仿真验证。