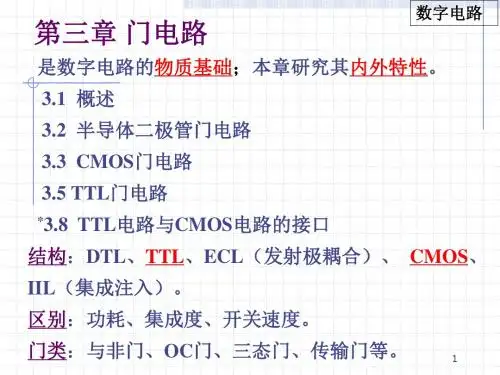

数字电路精简第3章门电路

- 格式:ppt

- 大小:3.18 MB

- 文档页数:10

路。

简称门电路。

5V一、TTL 与非门图3-1 典型TTL 与非门电路3.2 TTL 集成门电路•数字集成电路中应用最广的为TTL 电路(Transister-Transister-Logic 的缩写)•由若干晶体三极管、二极管和电阻组成,TTL 集成电路有54/74系列 ①输出高电平UOH 和输出低电平UOL 。

•输出高电平U OH:至少有一个输入端接低电平时的输出电平。

•输出低电平U OL:输入全为高电平时的输出电平。

• 电压传输特性的截止区的输出电压UOH=3.6V,饱和区的输出电压UOL=0.3V。

一般产品规定U OH≥2.4V、U OL<0.4V时即为合格。

二、TTL与非门的特性参数③开门电平U ON 和关门电平U OFF 。

开门电平U ON 是保证输出电平达到额定低电平(0.3V )时,所允许输入高电平的最低值,表示使与非门开通的最小输入电平。

通常U ON =1.4V ,一般产品规定U ON ≤1.8V 。

关门电平U OFF 是保证输出电平为额定高电平(2.7V 左右)时,允许输入低电平的最大值,表示与非门关断所允许的最大输入电平。

通常U OFF ≈1V ,一般产品要求U OFF ≥0.8V 。

5). 扇入系数Ni和扇出系数N O 是指与非门的输入端数目。

扇入系数Ni是指与非门输出端连接同类门的个数。

反扇出系数NO映了与非门的带负载能力。

6)输入短路电流I IS 。

当与非门的一个输入端接地而其余输入端悬空时,流过接地输入端的电流称为输入短路电流。

7)8)平均功耗P 指在空载条件下工作时所消耗的电功率。

三、TTL门电路的改进 74LS系列 性能比较好的门电路应该是工作速度既快,功耗又小的门电路。

因此,通常用功耗和传输延迟时间的乘积(简称功耗—延迟积或pd积)来评价门电路性能的优劣。

74LS系列又称低功耗肖特基系列。

74LS系列是功耗延迟积较小的系列(一般t pd<5 ns,功耗仅有2 mW) 并得到广泛应用。

数字电子技术基础第三章习题答案3-1 如图3-63a~d所示4个TTL门电路,A、B端输入的波形如图e所示,试分别画出F1、F2、F3和F4的波形图。

略3-2 电路如图3-64a所示,输入A、B的电压波形如图3-64b所示,试画出各个门电路输出端的电压波形。

略3-3 在图3-7所示的正逻辑与门和图3-8所示的正逻辑或门电路中,若改用负逻辑,试列出它们的逻辑真值表,并说明F和A、B之间是什么逻辑关系。

答:(1)图3-7负逻辑真值表F与A、B之间相当于正逻辑的“或”操作。

(2)图3-8负逻辑真值表F与A、B之间相当于正逻辑的“与”操作。

3-4 试说明能否将与非门、或非门、异或门当做反相器使用?如果可以,各输入端应如何连接?答:三种门经过处理以后均可以实现反相器功能。

(1)与非门: 将多余输入端接至高电平或与另一端并联;(2)或非门:将多余输入端接至低电平或与另一端并联;(3) 异或门:将另一个输入端接高电平。

3-5 为了实现图3-65所示的各TTL 门电路输出端所示的逻辑关系,请合理地将多余的输入端进行处理。

答:a )多余输入端可以悬空,但建议接高电平或与另两个输入端的一端相连;b)多余输入端接低电平或与另两个输入端的一端相连;c) 未用与门的两个输入端至少一端接低电平,另一端可以悬空、接高电平或接低电平;d )未用或门的两个输入端悬空或都接高电平。

3-6 如要实现图3-66所示各TTL 门电路输出端所示的逻辑关系,请分析电路输入端的连接是否正确?若不正确,请予以改正。

答:a )不正确。

输入电阻过小,相当于接低电平,因此将Ω50提高到至少2K Ω。

b) 不正确。

第三脚V CC 应该接低电平。

c )不正确。

万用表一般内阻大于2K Ω,从而使输出结果0。

因此多余输入端应接低电平,万用表只能测量A 或B 的输入电压。

3-7 (修改原题,图中横向电阻改为6k Ω,纵向电阻改为3.5 k Ω,β=30改为β=80) 为了提高TTL 与非门的带负载能力,可在其输出端接一个NPN 晶体管,组成如图3-67所示的开关电路。