SPI接口设计与实现

- 格式:docx

- 大小:38.72 KB

- 文档页数:3

SPI 串行外设接口总线,最早由Motorola提出,出现在其M68系列单片机中,由于其简单实用,又不牵涉到专利问题,因此许多厂家的设备都支持该接口,广泛应用于外设控制领域。

SPI接口是一种事实标准,并没有标准协议,大部分厂家都是参照Motorola的SPI接口定义来设计的。

但正因为没有确切的版本协议,不同家产品的SPI接口在技术上存在一定的差别,容易引起歧义,有的甚至无法直接互连(需要软件进行必要的修改)。

虽然SPI接口的内容非常简单,但本文仍将就其中的一些容易忽视的问题进行讨论。

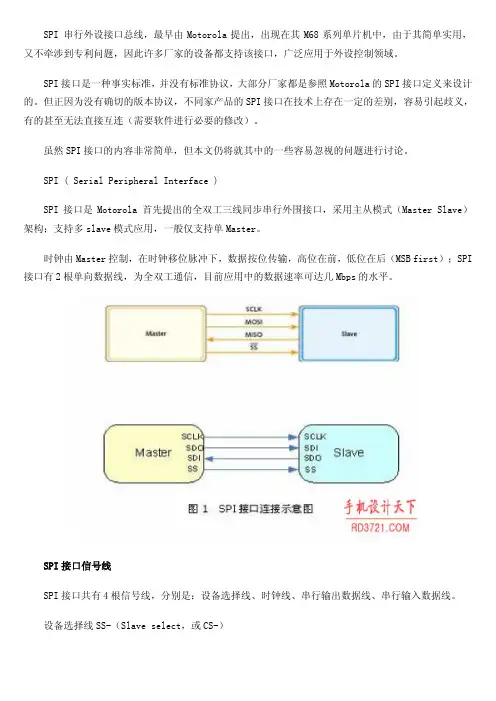

SPI ( Serial Peripheral Interface )SPI接口是Motorola 首先提出的全双工三线同步串行外围接口,采用主从模式(Master Slave)架构;支持多slave模式应用,一般仅支持单Master。

时钟由Master控制,在时钟移位脉冲下,数据按位传输,高位在前,低位在后(MSB first);SPI 接口有2根单向数据线,为全双工通信,目前应用中的数据速率可达几Mbps的水平。

SPI接口信号线SPI接口共有4根信号线,分别是:设备选择线、时钟线、串行输出数据线、串行输入数据线。

设备选择线SS-(Slave select,或CS-)SS-线用于选择激活某Slave设备,低有效,由Master驱动输出。

只有当SS-信号线为低电平时,对应Slave设备的SPI接口才处于工作状态。

SCLK:同步时钟信号线,SCLK用来同步主从设备的数据传输,由Master驱动输出,Slave设备按SCK的步调接收或发送数据。

串行数据线:SPI接口数据线是单向的,共有两根数据线,分别承担Master到Slave、Slave到Master的数据传输;但是不同厂家的数据线命名有差别。

Motorola的经典命名是MOSI和MISO,这是站在信号线的角度来命名的。

MOSI:When master, out line; when slave, in lineMISO:When master, in line; when slave, out line比如MOSI,该线上数据一定是Master流向Slave的。

SPI接口存储芯片测试系统的设计与实现摘要:近年来,社会进步迅速,随着网络技术和嵌入式技术的迅猛发展,嵌入式系统已成为继PC 和Internet 之后,IT 界新的技术热点。

利用嵌入式技术实现远程监控和视频数据传输已经得到了广泛的应用,为了实现这些应用,数据传输是很重要的环节。

为了减轻数字逻辑电路数据处理的压力和便于数据交换,会用到很多起承上启下枢纽作用的芯片,而与这些芯片进行连接的接口技术大多是采用SPI 接口技术。

在很多高档单片机中,高效率高速的SPI 串行接口技术作为一种标准配置,已经应用于数据交换和扩展外设。

在嵌入式数据传输中,对于波特率、数据格式等有着严格限制的工业控制中,通用串口不再适用,必须对串口进行重新开发。

关键词:SPI接口存储芯片测试系统;设计;实现引言数字电位器亦称数控可编程电阻器,是一种代替传统机械电位器(模拟电位器)的新型CMOS 数字、模拟混合信号处理的集成电路。

数字电位器也可作为普通电阻使用,但现在更多的作为数字可调电位器使用。

数字电位器采用数控方式调节电阻值,具有使用灵活、调节精度高、无触点、低噪音等显著优点。

数字电位器有数字输入控制,产生一个模拟量的输出,依据数字电位器的不同,抽头电流最大值可以从几百微安到几个毫安。

1数字电位器的特性参数数字电位器的电参数分为两类,直流参数和交流参数。

直流参数主要包括理论电阻值、变阻器差分非线性偏差、变阻器积分线性度、电刷阻抗、电位器非线性误差、电位器积分非线性偏差、满幅偏差、零阻值偏差、高输入电平、低输入电平、电源静态电流、电源工作电流、电源灵敏度等。

交流参数包括建立时间、最高工作速率、时钟信号的高持续时间、时钟信号的低持续时间、控制脚下降沿到时钟信号第一个上升沿的时间等重要指标,这些都是考核数字电位器性能的关键参数。

数字电位器一般有两种工作模式:电位器模式和模拟电阻器模式。

模拟电阻器模式时,电位器就类似于一个普通的两端电阻,利用电刷端的滑动实现不同的电阻值。

SPI接⼝串⾏外设接⼝(Serial Peripheral Interface)是⼀种同步外设接⼝,它可以使单⽚机与各种外围设备以串⾏⽅式进⾏通信以交换信息。

SPI最早是Motorola公司提出的全双⼯三线同步串⾏外围接⼝,采⽤主从模式(Master—Slave)架构,⽀持⼀个或多个Slave设备,由于其简单实⽤、性能优异,因此许多⼚家的设备都⽀持该接⼝,⼴泛应⽤于单⽚机和外设模块之间的连接。

SPI接⼝只需4条线:串⾏时钟线(SCK)、主机输⼊/从机输出数据线(MISO)、主机输出/从机输⼈数据线(MOSI)和低电平有效的从机选择线(SS)。

(1)MISO:主设备输⼊/从设备输出引脚。

该引脚在从模式下发送数据,在主模式下接收数据。

(2)MOSI:主设备输出/从设备输⼊引脚。

该引脚在主模式下发送数据,在从模式下接收数据。

(3)SCK:串⼝时钟,作为主设备的输出,从设备的输⼊。

(4)SS:从设备选择。

这是⼀个可选的引脚,⽤来选择主/从设备。

它的功能是⽤来作为⽚选引脚,让主设备可以单独地与特定从设备通信,避免数据线上的冲突。

SPI是⼀个环形总线结构,MOSI引脚相互连接,MISO引脚相互连接,数据在主和从之间串⾏地传输(MSB位在前),具体如下图所⽰。

SPI有主从两种⼯作模式,在主模式下,SPI为其他节点的CLK引脚提供串⾏时钟,数据从MOSI引脚输出,从MISO引脚输⼊。

在从模式下,数据从MISO引脚移出并由MOSI引脚移⼊,CLK引脚作为串⾏移位时钟的输⼊。

LPC824⽚内设计有SPI接⼝,具体的引脚取决于开关矩阵SWM的配置。

LPC824的SPI接⼝具有以下特点:•直接⽀持1⾄16位的数据发送。

软件⽀持更⼤的帧。

•主机和从机操作。

•⽆需读取输⼊数据即可将数据发送⾄从机,这在设置SPI存储器的时候很有⽤。

•控制信息还可与数据⼀同写⼊,这样便实现了极为丰富的操作,包括任意长度的帧。

•最多4个从机选择输⼊/输出,极性可选且使⽤灵活。

CPLD 实现SPI 接口1 实现原理CPLD 实现SPI 接口模块,通过对寄存器的操作,实现SPI 接口功能,对外部SPI 设备进行访问。

CPLD 内部SPI 模块逻辑框图如下所示。

CLK_DIVRX_SHIFT_REGSTATUS LOGICspi_clkspi_cs spi_dospi_tx_data_we_pulsereset_n spi_tx_data spi_rx_data spi_clk_div spi_rx_data_rd_pulsespi_dispi_tx_data_we_busy spi_rx_data_rd_ready spi_data_tx_we_overflow spi_data_rx_rd_nop spi_data_rx_rd_overtime cpld_clkCONTROL LOGICCOUNT LOGIC通过对主时钟分频,得到的SPI 接口时钟,其分频值可通过spi_clk_div 值设定,最小为6分频,当设置分频值低于6分频时,默认6分频。

SPI 接口的片选信号spi_cs 在写数据传输寄存器spi_tx_data 时,通过自动产生写脉冲spi_tx_data_we_pulse ,逻辑综合生成。

spi_rx_data_rd_pulse 在读取接收数据spi_rx_data 的数据时自动产生。

spi_di 和spi_do 分别由数据移位寄存器通过数据移位产生和接收。

spi_clk 由内部分频时钟和传输状态逻辑综合输出,在有数据时输出,无数据时保持高电平。

状态逻辑spi_tx_data_we_busy 信号分别表示数据正在传输,无法写入spi_tx_data 寄存器; spi_rx_data_rd_ready 信号表示数据接收完成,可读取spi_rx_data 寄存器的值。

错误状态逻辑spi_data_tx_we_overflow 信号表示在spi_tx_data 寄存器中写入了待传输值后,还未传输就又写入新的传输数据,表示写数据溢出。

SPI 接口的设计第二章介绍了模数转换器的可编程控制架构,其中可编程控制功能的实现需要分成两部分:一部分为SPI 接口电路,以及其根据内部寄存器存储的数据产生的控制信号;另一部分是具体的电路受控模块。

本章将介绍接口与数字逻辑电路的设计,包括应用于本模数转换器的SPI 接口与数字逻辑电路的设计、综合以及仿真验证。

3.1 数据通信接口 3.1.1 串行通信基本的通信方式有两种:并行通信和串行通信。

并行通信是指数据以成组的方式,在多条并行信道上同时进行传输。

串行通信指要传送的数据或信息按一定的格式编码,然后在单根线上,按位的先后顺序进行传送。

接收数据时,每次从单根线上按位接收信息,再把它们拼成一个字符,送给CPU (Central Processing Unit )做进一步的处理。

收发双方必须保持字符同步,以使接收方能从接收的数据比特流中正确区分出与发送方相同的一个一个字符。

串行通信只需要一条传输信道,易于实现,是目前主要采用的一种通信方式,它具有通信线少以及传送距离远等优点。

串行通信时,按数据的传送的方向可以分为单工、半双工和全双工等三种方式。

(1)单工(Simplex ):数据线仅能向一个方向传输数据,两个设备进行通信时,一边只能发送数据,另一边只能接收数据。

(2)半双工(Half Duplex ):数据可在两个设备间向任一个方向传输,但因为只有一根传输线,故同一时间内只能向一个方向传输数据,不能同时收发。

(3)全双工(Full Duplex ):对数据的两个传输方向采用不同的通路,可以同时发送和接收数据,串行通信有两种基本工作方式:异步方式和同步方式。

采用异步方式(Asynchronous )时,数据发送的格式如图3-1所示。

不发送数据时,数据信号线呈现高电平,处于空闲状态。

当有数据要发送时,数据信号线变成低电平,并持续一位的时间,用于表示字符的开始,称为起始位。

起始位之后,在信号线上依次出现待发送的每一位字符数据,最低有效位0D 最先出现。

十二SPI总线接口的verilog的实现1.实验目的项目中使用的许多器件需要SPI接口进行配置,比如PLL:ADF4350,AD:AD9627,VGA:AD8372等,本实验根据SPI协议,编写了一个简单的SPI读写程序,可以进行32位数据的读写,可以设置SPI SCLK相对于主时钟的分频比。

2.实验原理SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。

外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。

SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOST和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。

SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。

也是所有基于SPI的设备共有的,它们是SDI(数据输入),SDO(数据输出),SCK(时钟),CS(片选)。

(1)MOSI –主设备数据输出,从设备数据输入(2)MISO –主设备数据输入,从设备数据输出(3)SCLK –时钟信号,由主设备产生(4)CS –从设备使能信号,由主设备控制其中CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操作才有效。

这就允许在同一总线上连接多个SPI设备成为可能。

接下来就是负责通讯的3根线了。

通讯是通过数据交换完成的,这里先要知道SPI是串行通讯协议,也就是说数据是一位一位的传输的。

这就是SCK时钟线存在的原因,由SCK 提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。

数据输出通过 SDO线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取。

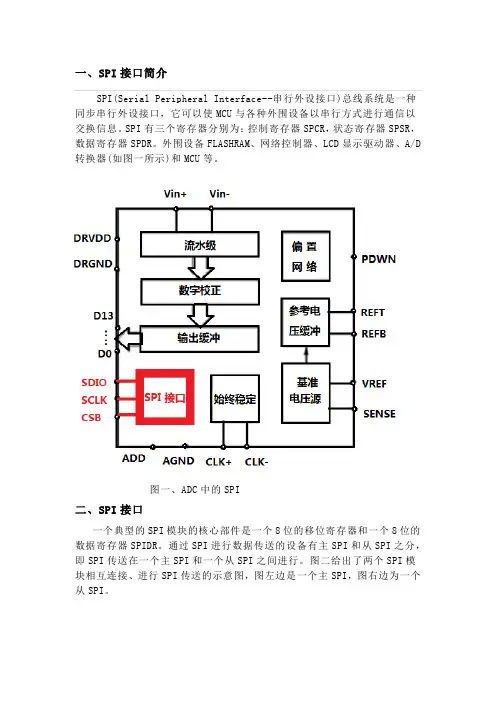

一、SPI接口简介SPI(Serial Peripheral Interface--串行外设接口)总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。

SPI有三个寄存器分别为:控制寄存器SPCR,状态寄存器SPSR,数据寄存器SPDR。

外围设备FLASHRAM、网络控制器、LCD显示驱动器、A/D 转换器(如图一所示)和MCU等。

图一、ADC中的SPI二、SPI接口一个典型的SPI模块的核心部件是一个8位的移位寄存器和一个8位的数据寄存器SPIDR。

通过SPI进行数据传送的设备有主SPI和从SPI之分,即SPI传送在一个主SPI和一个从SPI之间进行。

图二给出了两个SPI模块相互连接、进行SPI传送的示意图,图左边是一个主SPI,图右边为一个从SPI。

图二、典型SPI示意图在AN-877应用笔记中,对spi的接口定义与典型spi接口有所不同,AN-877使用一根线SDIO代替了典型SPI的MISO和MOSI,SS接口用CSB代替。

图三和图四分别是双线模式下单器件控制(主从一对一)和双线模式下多器件控制(主从一对多)。

图三:主从一对一控制图四:主从一对多控制但是原理都一样。

主从机之间一般由3个引脚组成:串行时钟引脚(SCLK)、串行数据输入/输出引脚(SDIO)、片选引脚(CSB)。

1、引脚数据输入/输出(SDIO):该引脚用作数据的输入/输出,用作输入还是用作输出具体取决于所发送的指令(读或写)以及时序帧中的相对位置(指令周期或数据周期)。

在读或写的第一个阶段,该引脚用作输入,将信息传递到内部状态机。

如果该命令为读命令,状态机把该引脚(SDIO)变为输出,然后该引脚将数据回传给外部控制器。

如果该命令为写命令,该引脚始终用作输入。

串行时钟(SCLK):SCLK由外部控制器提供,时钟频率最高为25MHZ。

所有数据的输入输出都是与SCLK同步的。

输入数据在SCLK的上升沿有效,输出数据在SCLK的下降沿有效。

![MAX7219及单片机的SPI接口设计[教育]](https://uimg.taocdn.com/a6f5c109a200a6c30c22590102020740be1ecde2.webp)

串行显示驱动器PS7219及单片机的SPI接口设计在单片机的应用系统中,为了便于人们观察和监视单片机的运行情况,常常需要用显示器显示运行的中间结果及状态等等。

因此显示器往往是单片机系统必不可少的外部设备之一。

常用的显示器有很多种,其中LED(发光二极管显示器)是应用较多的一种,它特别适用于强光和光线极弱的场合。

要使LED显示,必须提供段选码和位选码。

传统的硬件译码显示接口广泛采用由中央处理器CPU(如:Intel 8031)扩展I/O口(如:8255),然后再使用逻辑门驱动芯片(如7407等)驱动相应的位码和段码。

这种设计,芯片间连线十分复杂,系统工作可靠性不高,已越来越不适应单片机系统集成化、小型化的发展要求。

特别是系统并行扩展I/O,其缺点十分明显(1)连线太多,系统连线复杂,印制板布线不方便;(2)并行总线上挂靠的器件太多,系统工作的稳定性和可靠性低;(3)体积较大,集成度不高。

正是由于上述原因,近年来,各厂家相继开发出了集成度较高、驱动能力较强、驱动位数较多、功能齐全的LED显示驱动器。

本文介绍一种低价位、高性能的多位LED显示驱动器PS7219芯片,以及它与单片机89C51具体的SPI接口设计与应用软件。

1PS7219简介PS7219是一种新型的串行接口的8位数字静态显示芯片。

它是由武汉力源公司新推出的24脚双列直插式芯片,采用流行的同步串行外设接口(SPI),可与任何一种单片机方便接口,并可同时驱动8位LED (或64只独立LED),其引脚图如图1所示。

PS7219内部具有15×8RAM功能控制寄存器,可方便选址,对每位数字可单独控制、刷新、不需重写整个显示器。

显示数字亮度可由数字进行控制,每位具有闪烁使能控制位。

当引脚CON(13脚)置高电平,可禁止所有显示,达到降低功耗的效果,但同时并不影响对控制寄存器的修改。

PS7219还有一个掉电模式、一个允许用户从1位数显示到8位数显示选择的扫描界限寄存器和一个强迫所有LED接通的测试模式。

一种3线制半双工SPI接口设计

串行外围设备接口SPI(serial peripheralinterface)技术是Motorola 公司推出的一种微处理器、微控制器及其外设间的一种全/半双工同步串行数据接口标准,具有衔接线少、传输效率高等特点,因其硬件功能很强,与SPI有关的软件就相当容易,使CPU有更多的时光处理其他事务。

SPI接口普通采纳4条衔接线:串行时钟线(SCK)、主机输出/从机输入数据线(MOSI)、主机输入/从机输出数据线(MISO)和低电平使能的从机挑选线(SS),有的还带有中断信号线(INT),半双工或单向模式则不需要主机输出/从机输入数据线(MOSI)。

为了在削减引脚的基础上完成主从机的双向通讯,本文采纳半双工机制实现了一种3线制双向SPI 总线模块,即通过使能信号实现数据传输的方向控制,因此将主机输出/从机输入(MOSI)线和主机输入/从机输出线(MISO)线合并为一条双向信号线。

该模块是某芯片中的接口模块,其作用是实现基带芯片对射频芯片的控制以及数据交换,而且为了便于和射频集成,该模块终于以硬IP形式实现。

1 SPI总线协议

射频芯片的SPI接口具有两个主要特征:Slave工作模式和半双工方式通讯。

SPI接口信号描述如表1。

接口时序要求如下:

1)输出时序

当SEN为高电平常,SPI接口处于输出状态。

每次数据传输开头于SCK 信号的升高沿。

数据传输过程中,数据由SCK信号控制,并遵循下列规章:数据传输时,低位在前,高位在后;每个输出数据位在SCK下降沿采样;当本帧数据输出达到24 bit时,结束数据输出;当本帧数

第1页共4页。

S PI 总线接口的FPG A 设计与实现 杨承富1,徐志军2(1.解放军理工大学通信工程学院研究生2队,江苏南京210007;2.解放军理工大学通信工程学院电子信息工程系)摘 要:文中介绍了采用Alter ea 公司F LEX 10K 型的F PG A 器件实现串行外设接口(SPI)的原理与过程,给出了逻辑框图以及部分V erilog代码。

用此种方法实现的接口与专用接口芯片相比,具有使用灵活,系统配置方便的优点。

关键词:串行外设接口;现场可编程门阵列;V erilog 硬件描述语言中图分类号:T P336文献标识码:A 文章编号:0032-1289(2004)02-0072-05Design and Implemen t SPI Bus Interface with FPGAYAN G Cheng -fu 1,X U Zhi -jun 2(1.Postg raduate T ea m 2ICE,P L AU S T,Na njing 210007,China;2.Depar tment of Eelc tro nic Info r ma tio n Eng nee ring ICE,PL A U ST )Abstract :The theo ry and the wa y of im plementing a SPI interface w ith FPGA areintroduced,and the blo ck diag ram a nd som e Verilog code are presented.The chip implemented in this way has mo re agility and is m ore conv enient to co nfigure than others.Key words :SPI interface ;FPGA ;Verilog HDL串行外设接口SPI(Serial Peripheral Interface)是Mo to ro la 公司推出的一种同步串行接口。

板级通信总线之SPI及其Verilog实现打算写⼏篇专题,系统总结下常⽤的⽚上总线、现场总线,就先从最常⽤的SPI开始吧。

1. SPI是⼲什么的?除了SPI还有那些其它电路板及的通讯总线?有何差别?相信接触过MCU的同学对SPI都不陌⽣,详细定义就不罗嗦了。

SPI常⽤的场合包括ADC读写、存储芯⽚读写、MCU间通讯等等。

可以⼀主多从(通过⽚选来选择Slave),也可以做成菊花链等等形式的拓扑。

与SPI类似的总线还有IIC、UART等,甚⾄还有很多单根线的总线,原理都是基于简单的串⾏通信,区别在于收发时序和连接拓扑。

要熟练使⽤这些总线,关键在于理解其时序图,在此基础上创造各种变种的总线形式也不是难事(当然为了设计的通⽤性不建议这么做)。

以下维基百科的SPI词条介绍⾮常全⾯,推荐阅读。

2. SPI是什么样的?在此借⽤⼀张维基百科上的图,SPI通常有4根线,SS⽤于选定当前通信的slave,SCLK为通信的基准时钟,采样/发送都在时钟边沿执⾏,MOSI、MISO为串⾏的数据线。

以下是⼀个典型的SPI时序图,Master和Slave均在时钟上升沿采样,下降沿发送数据。

数据从最⾼位(MSB)开始发送。

需要注意图中所有的时序关系都要被满⾜,包括CS下降沿到第1个时钟上升沿间隔(t sclk_su)、数据的建⽴时间(t SU)、保持时间(t HD)等等。

通常这些参数由具体的器件决定,如果不满⾜则有通信失败的风险。

3. 如何使⽤SPI?SPI有哪⼏种配置模式(相位、极性)?根据SPI时钟信号的空闲状态、是上升沿采样还是下降沿采样,SPI有四种模式。

CPOL=0表⽰时钟空闲时为低电平,反之为⾼电平;CPHA=0表⽰时钟信号第⼀个边沿是采样边沿,反之表⽰第2个边沿是采样边沿。

对于带SPI接⼝的MCU⽽⾔,通常可由软件配置CPOL(Clock Polarity)、CPHA(Clock Phase),以适应和不同类型器件的通信。

STM32 SPI接口的简单实现通常SPI通过4个引脚与外部器件相连:・MISO:主设备输入/从设备输出引脚。

该引脚在从模式下发送数据,在主模式下接收数据。

・MOSI:主设备输出/从设备输入引脚。

该引脚在主模式下发送数据,在从模式下接收数据。

・SCK:串口时钟,作为主设备的输出,从设备的输入・NSS:从设备选择。

这是一个可选的引脚,用来选择主/从设备。

它的功能是用来作为“片选引脚”,让主设备可以单独地与特定从设备通讯,避免数据线上的冲突。

从设备的NSS引脚可以由主设备的一个标准I/O引脚来驱动。

一旦被使能(SSOE位),NSS引脚也可以作为输出引脚,并在SPI处于主模式时拉低;此时,所有的SPI设备,如果它们的NSS引脚连接到主设备的NSS引脚,则会检测到低电平,如果它们被设置为NSS硬件模式,就会自动进入从设备状态。

当配置为主设备、NSS配置为输入引脚(MSTR=1, SSOE=0)时,如果NSS被拉低,则这个SPI 设备进入主模式失败状态:即MSTR位被自动清除,此设备进入从模式。

时钟信号的相位和极性SPI_CR寄存器的CPOL和CPHA位,能够组合成四种可能的时序关系。

CPOL(时钟极性)位控制在没有数据传输时时钟的空闲状态电平,此位对主模式和从模式下的设备都有效。

如果CPOL被清‘ 0’,SCK引脚在空闲状态保持低电平;如果CPOL 被置’ 1’,SCK引脚在空闲状态保持高电平。

如果CPHA (时钟相位)位被置‘ 1’,SCK时钟的第二个边沿(CPOL位为0时就是下降沿,CPOL位为‘ 1’时就是上升沿)进行数据位的采样,数据在第二个时钟边沿被锁存。

如果CPHA位被清‘ 0’,SCK时钟的第一边沿(CPOL位为‘ 0’时就是下降沿,CPOL位为‘ 1’时就是上升沿)进行数据位采样,数据在第一个时钟边沿被锁存。

CPOL时钟极性和CPHA时钟相位的组合选择数据捕捉的时钟边沿。

图212显示了SPI传输的4种CPHA和CPOL位组合。

CRC校验在SPI接口设计中的实现强小燕;史兴强;刘梦影【摘要】串行外设接口(SPI,serial peripheral interface)以其高速的传输性能和灵活简单的配置,广泛应用于扩展外设及其数据交换.由于串行通信传输的不确定性以及干扰等原因,通信经常会出现异常情况.为提高SPI通信传输的可靠性,在SPI接口设计中增加循环冗余校验(CRC,cyclic Redundancy Check)功能.运用硬件描述语言Verilog HDL设计并实现了具有CRC校验功能的SPI接口.仿真结果表明,该SPI 接口不仅可以高速高效地工作于多种工作模式,且CRC校验功能能够保证通信传输的可靠性.【期刊名称】《电子与封装》【年(卷),期】2018(018)011【总页数】6页(P30-35)【关键词】CRC;串行;SPI;可靠性【作者】强小燕;史兴强;刘梦影【作者单位】中科芯集成电路股份有限公司,江苏无锡214072;中科芯集成电路股份有限公司,江苏无锡214072;中科芯集成电路股份有限公司,江苏无锡214072【正文语种】中文【中图分类】TN4021 引言为适应复杂的通信环境和高速的通信速率要求,能够快速可靠地完成大量数据交换的数据总线是极其重要的,因此设计一个高效可靠的通信接口就十分重要。

SPI接口技术是一种高速高效的串行接口技术[1],其接口连线简单、配置灵活、传输效率高[2],广泛应用于扩展外设和进行数据交换[3]。

随机噪声和干扰等因素存在于串行通信传输中,可能导致数据传输错误。

通过采用硬件措施进而加强通信传输的可靠性可检测这类错误,或在设计中增加校验功能,通过该方法检测数据在传输过程中是否发生错误[4]。

CRC是由分组线性码的分支而来[5],该算法简单易实现,能够同时检测和抗干扰,是一种高效可靠的差错校验法[6]。

该方法导致数据的冗余量增加,发送端不仅发送数据,最后还需将CRC码发送给接收端。

SPI接口设计与实现

SPI(SerialPeripheralInterface)总线是一种同步串行外设接口,它

可以使MCU与各种外围设备以串行方式进行通信以交换信息。

SPI总线应用广泛,已经成为很多器件的标准配置,可以直接和各个厂家生产的

多种标准外围器件直接接口。

其它常用的串行接口还有I2C、UART这

两种接口,这三种接口互有优缺点。

与I2C接口相比,SPI接口速度更快、协议更简单、并且是全双工的,但连线也相对多一些。

与UART接口相比,SPI更灵活,因为其使用主设备的时钟进行同步,所以两个比特之间

的时间间隔可以是任意的。

在点对点的通信中,SPI接口不需要进行寻

址操作,且为全双工通信,显得简单高效。

1SPI总线工作原理

SPI总线一般以主/从模式工作,通常有一个主设备和一个或多个从设备,数据传输由主机控制,典型SPI结构框图如图1所示。

SPI总线包含四条信号线,分别是sclk、miso、mosi和cs,其中,sclk为数据传输时钟,由主机产生;miso是从机输出,主机输入数据线;mosi是主机输出,

从机输入数据线;cs是从设备片选信号,由主机控制,当连接多个从设备时,通过该信号选择不同的从设备。

SPI总线是按字节发送数据的,主机和从机内部都包含一个8位串行移位寄存器,在时钟信号控制下,寄存

器内的数据由高到低输出至各自的数据线,8个时钟后,两个寄存器内的数据就被交换了。

如果只进行写操作,主机只需忽略接收到的字节;反之,若主机要读取从机的一个字节,就必须发送一个空字节来引发从机

的传输。

当主机发送一个连续的数据流时,可以进行多字节传输,在这

种传输方式下,从机的片选端必须在整个传输过程中保持低电平。

根据串行同步时钟极性和相位不同,SPI有四种工作方式。

时钟极性(CPOL)为0时,同步时钟的空闲状态为低电平,为1时,同步时钟的空闲

状态为高电平。

时钟相位(CPHA)为0时,在同步时钟的第一个跳变沿采

样数据,为1时,在同步时钟的第二个跳变沿采样数据。

因为主设备时

钟极性和相位都是以从设备为基准的,所以主设备时钟极性的配置和从设备时钟极性的配置是相反的。

SPI工作原理:以寄存器CPOL=1、CPHA=0为例,当要传输数据时,主机控制cs信号有效,sclk管脚输出时钟信号,在时钟上升沿,主机将需要发送的数据锁存在mosi线上,同时从miso线上读取从机发送的数据;在时钟下降沿,从机将需要发送的数据锁存在miso线上,同时从mosi 线上读取主机发送的数据,完成一次数据交换后,SPI总线重新回到空闲状态,等待下一次通信的发起。

2SPI总线硬件设计和软件实现

某项目的控制器硬件采用ARM+CPLD的技术方案,其中ARM为主控器,主要实现流程控制等,CPLD为从控制器。

ARM与CPLD之间主要通过SPI 接口进行通信,CPLD根据ARM发送的命令产生各模块的控制逻辑,完成一百多路IO控制,并且实现从一路UART接口到20路半双工RS485接口的收发切换。

ARM与CPLD之间的硬件接口如图2所示。

特别的,在ARM和CPLD之间设计了一个中断信号,用来提示SPI主机ARM,SPI从机CPLD有数据需要读取,请求发起SPI通信。

当CPLD作为SPI接口从机使用时,需要在CPLD中实现sclk下降沿检测、SPI控制模块。

2.1sclk下降沿检测因为ARM在sclk的上升沿读取CPLD输出的数据,所以CPLD必须在sclk的下降沿发数,上升沿时数据稳定。

同时为了在一个sclk时钟周期只接收或发送一个比特的数据,需要使该信号仅保持一个clk周期,该信号的产生方式如图3所示。

在clk信号驱动下,当该下降沿检测信号有效时(定为高电平有效),CPLD采集miso线上的数据,并将需要发送的数据输出至mosi。

2.2SPI控制模块如图4为从机软件设计流程图。

CPLD在系统上电后进入idle状态,idle表示空闲状态,当CPLD有数据需要传输时,通过int向ARM发送中断信号;当检测到cs信号有效时,进入spi数据传输状态;同步sclk信号,在下降沿,首先发送数据信息字节,通过数据信息字节通知ARM这次总共需要发送几个字节的数据,然后依次发送后续数

据,直到数据传输完成。

在上升沿,接收ARM发送的数据,并按字节存入RAM。

3SPI接口软件的设计仿真

对该项目SPI控制程序进行了仿真,其仿真波形如图5所示。

这个SPI 接口每次只有8bit,8bit代表地址还是数据由用户自己的协议来定,每启动一次接口模块,无论是主设备还是从设备都会写出一个数据和接收一个数据。

接收数据流程是:当cs下降沿到来时启动SPI接收控制模块,每个sclk下降沿读取1bit数据,ovalid有效时(高)读取odata数据(8bit)。

发送流程是:先确定从设备要写出的数据,再给主设备中断信号,主设备响应中断,启动一个读取流程,就可以读取从设备的一个

8bit数据。

4结语

SPI接口设计与实现。