spi_和接口设计

- 格式:doc

- 大小:814.00 KB

- 文档页数:20

基于FPGA的SPI4.2接口设计孙世国陈帅陈倩张恒威北京航天飞行控制中心 100094摘要:本文介绍了一种FPGA和IPX2805之间的SPI4.2接口模块设计的方法,对硬件设计进行了说明,着重阐述了FPGA内部SPI4.2接口模块设计。

该设计简单、高效,解决了商用芯片不能满足高速转发的系统要求的问题。

方案在Altera的Stratix II器件上得到了验证。

关键词:FPGA,IPX2805,SPI4.2The SPI4.2 Interface Module Design Based on FPGASUN SHIGUO CHEN SHUAI CHEN QIAN ZHANG HENGWEIBeijing Aerospace Control Center 100094Abstract:To design SPI4.2 interface module, a method based on FPGA and IPX2805 interface chip is described in this paper, including circuit design diagram . The design is simple and high efficiency.It satisfies the system require of high-speed transmit that is can not satisfied by business chip. The objective is achieved in the Stratix II of Altera.Key words:FPGA,IPX2805,SPI4.21.引言SPI-4.2(System Packet Interface)是OIF(Optical Internetworking Forum)定义的局部高速总线标准,用于PHY层芯片到链路层芯片的10Gbps信号传输。

电路设计中的通信接口通信接口设计的基本原理和方法通信接口在电路设计中起着至关重要的作用,它负责连接各种电子设备和系统,实现数据传输和通信功能。

本文将介绍通信接口设计的基本原理和方法,以帮助读者更好地理解和应用于实际电路设计中。

一、通信接口的基本原理通信接口的设计基于通信原理和电路设计的基本原理。

通信原理主要包括信号传输、编码和解码、调制和解调等基本概念。

电路设计的基本原理包括电路的连接、信号放大、滤波和保护等方面。

通信接口的基本原理主要有以下几个方面:1. 信号传输:通信接口设计需要考虑信号的传输方式,如串行传输和并行传输。

串行传输适用于长距离传输和高速传输,而并行传输适用于短距离传输和低速传输。

2. 信号编码和解码:通信接口需要对信号进行编码和解码,以确保数据的准确传输。

常用的编码方式有二进制编码和差分编码等。

3. 调制和解调:通信接口设计需要考虑信号的调制和解调方式,以实现数据的传输和接收。

调制方式有幅度调制、频率调制和相位调制等。

4. 噪声和干扰抑制:通信接口设计需要考虑信号的抗干扰能力,采取适当的抗干扰措施,如滤波和屏蔽等,以提高系统的信号质量和可靠性。

5. 电源和地线设计:通信接口设计还需要考虑电源和地线的设计,保证系统的电源稳定和地线的良好连接,以提供可靠的电源和信号环境。

二、通信接口设计的方法通信接口设计涉及到多个方面的考虑和技术,下面介绍几种常用的通信接口设计方法:1. 标准接口设计:通信接口设计可以参考各种标准接口规范,如USB、UART、SPI、I2C等接口标准。

这些标准接口规范提供了通信接口的连接方式、信号电平、通信协议等详细要求,使得接口设计更加规范和统一。

2. 数据传输速率匹配:通信接口设计需要根据连接的设备或系统之间的数据传输速率进行匹配。

如果传输速率不匹配,可能导致数据传输错误或数据丢失。

3. 信号电平匹配:通信接口设计需要考虑信号电平的匹配,以保证数据的正确传输。

SPI 串行外设接口总线,最早由Motorola提出,出现在其M68系列单片机中,由于其简单实用,又不牵涉到专利问题,因此许多厂家的设备都支持该接口,广泛应用于外设控制领域。

SPI接口是一种事实标准,并没有标准协议,大部分厂家都是参照Motorola的SPI接口定义来设计的。

但正因为没有确切的版本协议,不同家产品的SPI接口在技术上存在一定的差别,容易引起歧义,有的甚至无法直接互连(需要软件进行必要的修改)。

虽然SPI接口的内容非常简单,但本文仍将就其中的一些容易忽视的问题进行讨论。

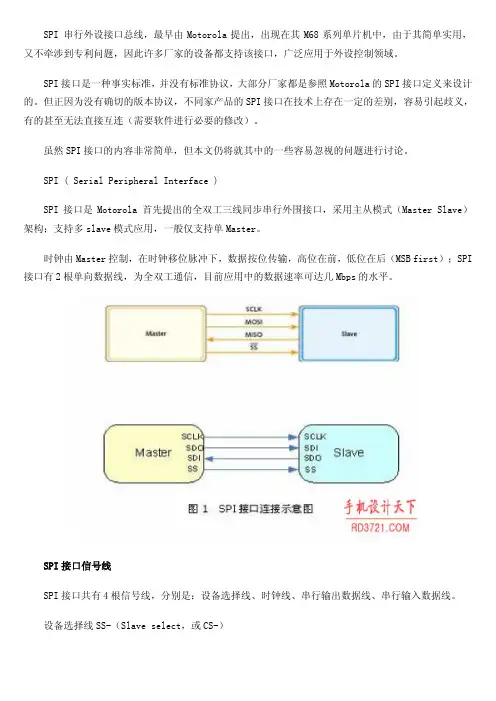

SPI ( Serial Peripheral Interface )SPI接口是Motorola 首先提出的全双工三线同步串行外围接口,采用主从模式(Master Slave)架构;支持多slave模式应用,一般仅支持单Master。

时钟由Master控制,在时钟移位脉冲下,数据按位传输,高位在前,低位在后(MSB first);SPI 接口有2根单向数据线,为全双工通信,目前应用中的数据速率可达几Mbps的水平。

SPI接口信号线SPI接口共有4根信号线,分别是:设备选择线、时钟线、串行输出数据线、串行输入数据线。

设备选择线SS-(Slave select,或CS-)SS-线用于选择激活某Slave设备,低有效,由Master驱动输出。

只有当SS-信号线为低电平时,对应Slave设备的SPI接口才处于工作状态。

SCLK:同步时钟信号线,SCLK用来同步主从设备的数据传输,由Master驱动输出,Slave设备按SCK的步调接收或发送数据。

串行数据线:SPI接口数据线是单向的,共有两根数据线,分别承担Master到Slave、Slave到Master的数据传输;但是不同厂家的数据线命名有差别。

Motorola的经典命名是MOSI和MISO,这是站在信号线的角度来命名的。

MOSI:When master, out line; when slave, in lineMISO:When master, in line; when slave, out line比如MOSI,该线上数据一定是Master流向Slave的。

SPI、I2C、UART三种串⾏总线协议的区别和SPI接⼝介绍(转)SPI、I2C、UART三种串⾏总线协议的区别第⼀个区别当然是名字:SPI(Serial Peripheral Interface:串⾏外设接⼝);I2C(INTER IC BUS)UART(Universal Asynchronous Receiver Transmitter:通⽤异步收发器)第⼆,区别在电⽓信号线上:SPI总线由三条信号线组成:串⾏时钟(SCLK)、串⾏数据输出(SDO)、串⾏数据输⼊(SDI)。

SPI总线可以实现多个SPI设备互相连接。

提供SPI串⾏时钟的SPI设备为SPI主机或主设备(Master),其他设备为SPI从机或从设备(Slave)。

主从设备间可以实现全双⼯通信,当有多个从设备时,还可以增加⼀条从设备选择线。

如果⽤通⽤IO⼝模拟SPI总线,必须要有⼀个输出⼝(SDO),⼀个输⼊⼝(SDI),另⼀个⼝则视实现的设备类型⽽定,如果要实现主从设备,则需输⼊输出⼝,若只实现主设备,则需输出⼝即可,若只实现从设备,则只需输⼊⼝即可。

I2C总线是双向、两线(SCL、SDA)、串⾏、多主控(multi-master)接⼝标准,具有总线仲裁机制,⾮常适合在器件之间进⾏近距离、⾮经常性的数据通信。

在它的协议体系中,传输数据时都会带上⽬的设备的设备地址,因此可以实现设备组⽹。

如果⽤通⽤IO⼝模拟I2C总线,并实现双向传输,则需⼀个输⼊输出⼝(SDA),另外还需⼀个输出⼝(SCL)。

(注:I2C资料了解得⽐较少,这⾥的描述可能很不完备)UART总线是异步串⼝,因此⼀般⽐前两种同步串⼝的结构要复杂很多,⼀般由波特率产⽣器(产⽣的波特率等于传输波特率的16倍)、UART接收器、UART发送器组成,硬件上由两根线,⼀根⽤于发送,⼀根⽤于接收。

显然,如果⽤通⽤IO⼝模拟UART总线,则需⼀个输⼊⼝,⼀个输出⼝。

第三,从第⼆点明显可以看出,SPI和UART可以实现全双⼯,但I2C不⾏;第四,看看⽜⼈们的意见吧!wudanyu:I2C线更少,我觉得⽐UART、SPI更为强⼤,但是技术上也更加⿇烦些,因为I2C需要有双向IO的⽀持,⽽且使⽤上拉电阻,我觉得抗⼲扰能⼒较弱,⼀般⽤于同⼀板卡上芯⽚之间的通信,较少⽤于远距离通信。

SPI总线简介及原理2009-12-29 10:52SPI(Serial Peripheral Interface)是一种串行同步通讯协议,由一个主设备和一个或多个从设备组成,主设备启动一个与从设备的同步通讯,从而完成数据的交换。

SPI 接口由SDI(串行数据输入),SDO(串行数据输出),SCK(串行移位时钟),CS(从使能信号)四种信号构成,CS 决定了唯一的与主设备通信的从设备,如没有CS 信号,则只能存在一个从设备,主设备通过产生移位时钟来发起通讯。

通讯时,数据由SDO 输出,SDI 输入,数据在时钟的上升或下降沿由SDO 输出,在紧接着的下降或上升沿由SDI 读入,这样经过8/16 次时钟的改变,完成8/16 位数据的传输。

SPI通信该总线通信基于主-从配置。

它有以下4个信号:MOSI:主出/从入MISO:主入/从出SCK:串行时钟SS:从属选择芯片上“从属选择”(slave-select)的引脚数决定了可连到总线上的器件数量。

在SPI传输中,数据是同步进行发送和接收的。

数据传输的时钟基于来自主处理器的时钟脉冲,摩托罗拉没有定义任何通用SPI的时钟规范。

然而,最常用的时钟设置基于时钟极性(CPOL)和时钟相位(CPHA)两个参数,CPOL定义SPI串行时钟的活动状态,而CPHA定义相对于SO-数据位的时钟相位。

CPOL和CPHA的设置决定了数据取样的时钟沿。

数据方向和通信速度SPI传输串行数据时首先传输最高位。

波特率可以高达5Mbps,具体速度大小取决于SPI硬件。

例如,Xicor公司的SPI串行器件传输速度能达到5MHz。

SPI总线接口及时序SPI总线包括1根串行同步时钟信号线以及2根数据线。

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

如果 CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。

SPI接口存储芯片测试系统的设计与实现摘要:近年来,社会进步迅速,随着网络技术和嵌入式技术的迅猛发展,嵌入式系统已成为继PC 和Internet 之后,IT 界新的技术热点。

利用嵌入式技术实现远程监控和视频数据传输已经得到了广泛的应用,为了实现这些应用,数据传输是很重要的环节。

为了减轻数字逻辑电路数据处理的压力和便于数据交换,会用到很多起承上启下枢纽作用的芯片,而与这些芯片进行连接的接口技术大多是采用SPI 接口技术。

在很多高档单片机中,高效率高速的SPI 串行接口技术作为一种标准配置,已经应用于数据交换和扩展外设。

在嵌入式数据传输中,对于波特率、数据格式等有着严格限制的工业控制中,通用串口不再适用,必须对串口进行重新开发。

关键词:SPI接口存储芯片测试系统;设计;实现引言数字电位器亦称数控可编程电阻器,是一种代替传统机械电位器(模拟电位器)的新型CMOS 数字、模拟混合信号处理的集成电路。

数字电位器也可作为普通电阻使用,但现在更多的作为数字可调电位器使用。

数字电位器采用数控方式调节电阻值,具有使用灵活、调节精度高、无触点、低噪音等显著优点。

数字电位器有数字输入控制,产生一个模拟量的输出,依据数字电位器的不同,抽头电流最大值可以从几百微安到几个毫安。

1数字电位器的特性参数数字电位器的电参数分为两类,直流参数和交流参数。

直流参数主要包括理论电阻值、变阻器差分非线性偏差、变阻器积分线性度、电刷阻抗、电位器非线性误差、电位器积分非线性偏差、满幅偏差、零阻值偏差、高输入电平、低输入电平、电源静态电流、电源工作电流、电源灵敏度等。

交流参数包括建立时间、最高工作速率、时钟信号的高持续时间、时钟信号的低持续时间、控制脚下降沿到时钟信号第一个上升沿的时间等重要指标,这些都是考核数字电位器性能的关键参数。

数字电位器一般有两种工作模式:电位器模式和模拟电阻器模式。

模拟电阻器模式时,电位器就类似于一个普通的两端电阻,利用电刷端的滑动实现不同的电阻值。

SPI总线规范SPI是英文Serial Peripheral Interface的缩写,中文意思是串行外围设备接口,SPI是Motorola公司推出的一种同步串行通讯方式,是一种三线同步总线,因其硬件功能很强,与SPI有关的软件就相当简单,使CPU有更多的时间处理其他事务。

SPI概述SPI:高速同步串行口。

3~4线接口,收发独立、可同步进行.SPI,是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。

是Motorola首先在其MC68HCXX系列处理器上定义的。

PI接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

SPI,是一种高速的,全双工,同步的通信总线并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议,比如AT91RM9200.SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。

外围设置FLASHRAM、网络控制器、LCD 显示驱动器、A/D转换器和MCU等。

SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT或INT、有的SP 接口芯片没有主机输出/从机输入数据线MOSI)。

SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)也是所有基于SPI的设备共有的,它们是SDI(数据输入),SDO(数据输出)SCK(时钟),CS(片选)。

(1)SDO–主设备数据输出,从设备数据输入(2)SDI–主设备数据输入,从设备数据输出(3)SCLK–时钟信号,由主设备产生(4)CS–从设备使能信号,由主设备控制其中CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操作才有效。

SPI接⼝串⾏外设接⼝(Serial Peripheral Interface)是⼀种同步外设接⼝,它可以使单⽚机与各种外围设备以串⾏⽅式进⾏通信以交换信息。

SPI最早是Motorola公司提出的全双⼯三线同步串⾏外围接⼝,采⽤主从模式(Master—Slave)架构,⽀持⼀个或多个Slave设备,由于其简单实⽤、性能优异,因此许多⼚家的设备都⽀持该接⼝,⼴泛应⽤于单⽚机和外设模块之间的连接。

SPI接⼝只需4条线:串⾏时钟线(SCK)、主机输⼊/从机输出数据线(MISO)、主机输出/从机输⼈数据线(MOSI)和低电平有效的从机选择线(SS)。

(1)MISO:主设备输⼊/从设备输出引脚。

该引脚在从模式下发送数据,在主模式下接收数据。

(2)MOSI:主设备输出/从设备输⼊引脚。

该引脚在主模式下发送数据,在从模式下接收数据。

(3)SCK:串⼝时钟,作为主设备的输出,从设备的输⼊。

(4)SS:从设备选择。

这是⼀个可选的引脚,⽤来选择主/从设备。

它的功能是⽤来作为⽚选引脚,让主设备可以单独地与特定从设备通信,避免数据线上的冲突。

SPI是⼀个环形总线结构,MOSI引脚相互连接,MISO引脚相互连接,数据在主和从之间串⾏地传输(MSB位在前),具体如下图所⽰。

SPI有主从两种⼯作模式,在主模式下,SPI为其他节点的CLK引脚提供串⾏时钟,数据从MOSI引脚输出,从MISO引脚输⼊。

在从模式下,数据从MISO引脚移出并由MOSI引脚移⼊,CLK引脚作为串⾏移位时钟的输⼊。

LPC824⽚内设计有SPI接⼝,具体的引脚取决于开关矩阵SWM的配置。

LPC824的SPI接⼝具有以下特点:•直接⽀持1⾄16位的数据发送。

软件⽀持更⼤的帧。

•主机和从机操作。

•⽆需读取输⼊数据即可将数据发送⾄从机,这在设置SPI存储器的时候很有⽤。

•控制信息还可与数据⼀同写⼊,这样便实现了极为丰富的操作,包括任意长度的帧。

•最多4个从机选择输⼊/输出,极性可选且使⽤灵活。

SPI 接口的设计第二章介绍了模数转换器的可编程控制架构,其中可编程控制功能的实现需要分成两部分:一部分为SPI 接口电路,以及其根据内部寄存器存储的数据产生的控制信号;另一部分是具体的电路受控模块。

本章将介绍接口与数字逻辑电路的设计,包括应用于本模数转换器的SPI 接口与数字逻辑电路的设计、综合以及仿真验证。

3.1 数据通信接口 3.1.1 串行通信基本的通信方式有两种:并行通信和串行通信。

并行通信是指数据以成组的方式,在多条并行信道上同时进行传输。

串行通信指要传送的数据或信息按一定的格式编码,然后在单根线上,按位的先后顺序进行传送。

接收数据时,每次从单根线上按位接收信息,再把它们拼成一个字符,送给CPU (Central Processing Unit )做进一步的处理。

收发双方必须保持字符同步,以使接收方能从接收的数据比特流中正确区分出与发送方相同的一个一个字符。

串行通信只需要一条传输信道,易于实现,是目前主要采用的一种通信方式,它具有通信线少以及传送距离远等优点。

串行通信时,按数据的传送的方向可以分为单工、半双工和全双工等三种方式。

(1)单工(Simplex ):数据线仅能向一个方向传输数据,两个设备进行通信时,一边只能发送数据,另一边只能接收数据。

(2)半双工(Half Duplex ):数据可在两个设备间向任一个方向传输,但因为只有一根传输线,故同一时间内只能向一个方向传输数据,不能同时收发。

(3)全双工(Full Duplex ):对数据的两个传输方向采用不同的通路,可以同时发送和接收数据,串行通信有两种基本工作方式:异步方式和同步方式。

采用异步方式(Asynchronous )时,数据发送的格式如图3-1所示。

不发送数据时,数据信号线呈现高电平,处于空闲状态。

当有数据要发送时,数据信号线变成低电平,并持续一位的时间,用于表示字符的开始,称为起始位。

起始位之后,在信号线上依次出现待发送的每一位字符数据,最低有效位0D 最先出现。

一、SPI接口简介SPI(Serial Peripheral Interface--串行外设接口)总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。

SPI有三个寄存器分别为:控制寄存器SPCR,状态寄存器SPSR,数据寄存器SPDR。

外围设备FLASHRAM、网络控制器、LCD显示驱动器、A/D 转换器(如图一所示)和MCU等。

图一、ADC中的SPI二、SPI接口一个典型的SPI模块的核心部件是一个8位的移位寄存器和一个8位的数据寄存器SPIDR。

通过SPI进行数据传送的设备有主SPI和从SPI之分,即SPI传送在一个主SPI和一个从SPI之间进行。

图二给出了两个SPI模块相互连接、进行SPI传送的示意图,图左边是一个主SPI,图右边为一个从SPI。

图二、典型SPI示意图在AN-877应用笔记中,对spi的接口定义与典型spi接口有所不同,AN-877使用一根线SDIO代替了典型SPI的MISO和MOSI,SS接口用CSB代替。

图三和图四分别是双线模式下单器件控制(主从一对一)和双线模式下多器件控制(主从一对多)。

图三:主从一对一控制图四:主从一对多控制但是原理都一样。

主从机之间一般由3个引脚组成:串行时钟引脚(SCLK)、串行数据输入/输出引脚(SDIO)、片选引脚(CSB)。

1、引脚数据输入/输出(SDIO):该引脚用作数据的输入/输出,用作输入还是用作输出具体取决于所发送的指令(读或写)以及时序帧中的相对位置(指令周期或数据周期)。

在读或写的第一个阶段,该引脚用作输入,将信息传递到内部状态机。

如果该命令为读命令,状态机把该引脚(SDIO)变为输出,然后该引脚将数据回传给外部控制器。

如果该命令为写命令,该引脚始终用作输入。

串行时钟(SCLK):SCLK由外部控制器提供,时钟频率最高为25MHZ。

所有数据的输入输出都是与SCLK同步的。

输入数据在SCLK的上升沿有效,输出数据在SCLK的下降沿有效。

SPI 接口的设计第二章介绍了模数转换器的可编程控制架构,其中可编程控制功能的实现需要分成两部分:一部分为SPI 接口电路,以及其根据部寄存器存储的数据产生的控制信号;另一部分是具体的电路受控模块。

本章将介绍接口与数字逻辑电路的设计,包括应用于本模数转换器的SPI 接口与数字逻辑电路的设计、综合以及仿真验证。

3.1 数据通信接口3.1.1 串行通信基本的通信方式有两种:并行通信和串行通信。

并行通信是指数据以成组的方式,在多条并行信道上同时进行传输。

串行通信指要传送的数据或信息按一定的格式编码,然后在单根线上,按位的先后顺序进行传送。

接收数据时,每次从单根线上按位接收信息,再把它们拼成一个字符,送给CPU (Central Processing Unit )做进一步的处理。

收发双方必须保持字符同步,以使接收方能从接收的数据比特流中正确区分出与发送方相同的一个一个字符。

串行通信只需要一条传输信道,易于实现,是目前主要采用的一种通信方式,它具有通信线少以及传送距离远等优点。

串行通信时,按数据的传送的方向可以分为单工、半双工和全双工等三种方式。

(1)单工(Simplex ):数据线仅能向一个方向传输数据,两个设备进行通信时,一边只能发送数据,另一边只能接收数据。

(2)半双工(Half Duplex ):数据可在两个设备间向任一个方向传输,但因为只有一根传输线,故同一时间只能向一个方向传输数据,不能同时收发。

(3)全双工(Full Duplex ):对数据的两个传输方向采用不同的通路,可以同时发送和接收数据,串行通信有两种基本工作方式:异步方式和同步方式。

采用异步方式(Asynchronous )时,数据发送的格式如图3-1所示。

不发送数据时,数据信号线呈现高电平,处于空闲状态。

当有数据要发送时,数据信号线变成低电平,并持续一位的时间,用于表示字符的开始,称为起始位。

起始位之后,在信号线上依次出现待发送的每一位字符数据,最低有效位0D 最先出现。

采用不同的编码方案,待发送的每个字符的位数就不同。

当字符用ASCII 码表示时,数据位占7位(60~D D )。

在数据位的后面有一个奇偶校验位,其后有停止位,用于指示字符的结束。

停止位可以是一位也可以是一位半或两位。

可见,用异步方式发送一个7位的ASCII 码字符时,实际需发送10位、10.5位或11位信息。

如果用10位来发送的话,就意味着发送过程中将会浪费30%的传输时间。

为了提高串行数据传输的速率,可以采用同步传送方式。

一帧第n个字符图3-1 异步串行数据发送格式同步方式(Synchronous )中串行同步字符的格式如图3-2所示。

没有数据发送时,传输线处于空闲状态。

为了表示数据传输的开始,发送方先发送一个或两个特殊字符,称该字符为同步字符。

当发送方和接收方达到同步后,就可以连续地发送数据,不需要起始位和停止位了,可以显著的提高数据的传输速率。

采用同步方式传送的发送过程中,收发双方须由同一个时钟来协调,用来确定串行传输每一位的位置。

在接收数据时,接收方可利用同步字符将部时钟与发送方保持同步,然后将同步字符后面的数据逐位移入,并转换成并行格式,直至收到结束符为止。

图3-2 同步串行数据发送格式3.1.2 SPI 接口简介SPI(Serial Peripheral Interface)是由Motorola 公司提出的一种工业标准,后来交给Opencores 组织进行维护。

SPI 模块是在MCU 与MCU 之间,或MCU 与外围设备之间实现近距离、全双工、同步串行传送的接口。

与其它串行接口相比,具有电路结构简单、速度快、通信可靠等优点。

通过SPI 接口,MCU 可以很方便的与外围芯片直接相连,用以传送控制/状态信息和输入/输出数据。

一个典型的SPI 模块的核心部件是一个8位的移位寄存器和一个8位的数据寄存器SPIDR 。

通过SPI 进行数据传送的设备有主SPI 和从SPI 之分,即SPI 传送在一个主SPI 和一个从SPI 之间进行。

图3-3给出了两个SPI 模块相互连接、进行SPI 传送的示意图,图左边是一个主SPI ,图右边为一个从SPI 。

图3-3 典型SPI模块典型的SPI接口有四个引脚:MISO(主入从出)、MOSI(主出从入)、SCLK(串行时钟)和SS(从选择)。

具体功能如表3-1。

表3-1 典型SPI接口引脚传送时双方的MISO(主入从出)、MOSI(主出从入)、SCLK(串行时钟)同名引脚相连。

SS引脚的定义有几种选择,因而有不同的连法。

可以看到,主SPI和从SPI的移位寄存器通过MISO和MOSI引脚连接为一个16位的移位寄存器。

主SPI的波特率发生器产生移位时钟SCLK。

主SPI启动传送过程,MCU向其SPIDR进行一次写入。

写入SPIDR的数据被装载到SPI的移位寄存器。

根据SCLK的8个周期,双方同步移位8次,移位寄存器中的容交换,然后双方移位寄存器中的数据加载到各自的SPIDR,双方传送完成标志置1,完成一次传送。

仅从传送路径上看,无所谓发送方和接收方。

在一次传送开始之前发送方应将发送数据写入自己的SPIDR,该数据自动装载入移位寄存器。

在一次传送完成后,接收方从SPIDR中读取接收数据[26]。

目前已有的SPI接口IP软核,XILINX公司的CoolRunner系列SPI主机IP核[27](CoolRunner Serial Peripheral Interface Master IP Core),是通过有限状态机来控制SPI主机与从机以及微控制器之间的通信。

Motorola公司的SPI核[28]是一个主从共用的IP软核,具有很高的可重用性和通用性。

3.2 SPI接口的设计与综合3.2.1 设计方法、目标及流程本文SPI接口采用自顶向下设计方法。

自顶向下设计[29][30]是一种逐级分解、变换,将系统要求转变为电路或者版图的过程。

从系统级(System Level Design)开始考虑系统的行为、功能、性能以及允许的芯片面积和成本要求,进行系统划分和功能设计。

用行为语言描述每个方框的外特性,并将全部方框连在一起进行系统仿真(System Simulation)来验证系统设计的正确性。

RTL级设计按照系统要求编写程序,一般使用Verilog HDL或VHDL语言进行编程,使之符合系统设计规定的外特性。

RTL级设计的结果须经行为仿真(Behavior simulation),保证源代码(Source Code)的逻辑功能正确。

把源代码转换为网表的过程叫做综合。

网表是使用Verilog语言对门级电路的结构性描述,它是最底层文件。

网表是原理图的语言描述,对应着门级电路原理图。

网表中所有的器件都包含有必须的工业参数,如温度特性、电压特性、固有门延时、输入阻抗、上升时间、下降时间、驱动能力、面积等[31][32]。

由于这些工业参数的存在,使得门级仿真(Gate Level Simulation)十分接近于真实芯片的物理测试。

经过门级仿真后再经过自动布局布线(Auto Place and Route),从而生成版图(Layout),经过物理验证和后仿真,就可以制版流片,并交付封装测试。

整个流程如图3-4所示。

图3-4 自顶向下的设计流程由上节可知,SPI接口有主从之分,本文设计重点为从SPI(Slave SPI)。

这主要是由于本文的应用环境决定的。

本文设计的ADC接口电路及数字逻辑电路的主要目标是实现外部主SPI对从SPI的初始化。

要求从主SPI接收数据,配置部的寄存器,实现相应的控制目标,产生相应的控制信号。

不需要产生数据来配置其他的芯片,所以本文设计的SPI接口中就没有考虑波特率发生器,它只能从外部接收移位时钟。

首先,对所要设计的从SPI做整体规划,建立架构,并对系统进行层次划分。

根据实际需要,将主SPI与从SPI之间的连接架构简单的归结为图3-5所示。

图3-5 主从SPI之间连接架构主SPI与从SPI之间通过CSB、SCLK、SDIO三个引脚进行相连,它们分别是片选引脚、串行时钟引脚、串行数据输入\输出引脚。

此架构比典型的SPI接口引脚少了一个串行数据输出引脚,为了使芯片引脚数量最少,所以将这一引脚省略。

3.2.2 SPI 接口外特性3.2.2.1 SPI 接口的端口引脚SPI接口的端口引脚包括:CSB、SCLK、SDIO。

(1)CSB片选引脚CSB是一种低电平有效控制,用来选通读写周期。

CSB可以在多种模式下工作,如果控制器具有芯片选择输出或其他多器件选择方法,则该引脚可以与CSB 线相连。

当该线为低电平时,器件被选择,SCLK和SDIO线路上的信息便会得到处理。

当该引脚为高电平时,器件会忽略SCLK和SDIO线路上的所有信息。

这样,多个器件便可以与SPI端口相连。

在只连接一个器件的情况下,可以将CSB 线路与低电平相连,使器件始终处于使能状态,但是此时如果端口发生错误,将无法使器件复位,因为复位信号要在CSB的上升沿才起作用。

(2)SCLK串行时钟SCLK引脚为串行移位时钟输入引脚,用来使串行接口的操作同步。

输入数据在该时钟上升沿有效,输出数据在下降沿有效。

因为本文中SPI接口仅仅用来为配置寄存器传送数据,所以对数据传输的速率要求不高。

为降低该引脚对时钟线路上噪声的敏感度,它采用施密特触发器实现。

(3)SDIO串行数据输入/输出SDIO引脚用作输入或输出,取决于所发送的指令(读或写)以及时序帧中的相对位置(指令周期或者数据周期)。

在写或读操作的第一阶段,该引脚用作输入,将信息传递到部状态机。

如果该命令被确定为写命令,则在指令周期,SDIO引脚始终用作串行输入,将数据传送给部移位寄存器。

如果该命令被确定为读命令,状态机将把SDIO引脚变为输出,然后该引脚将数据回传给控制器。

在本文设计的SPI接口中,该引脚目前只实现向寄存器中写入数据的功能。

3.2.2.2 SPI 接口的数据基本传送规则(1)格式SDIO数据传输的第一阶段是指令阶段,指令由16位组成,之后是数据,数据由一个或多个8位构成,长度由前面的指令字长位确定。

CSB的下降沿与SCLK的上升沿一起决定帧何时开始。

如果器件的CSB与低电平相连,则帧开始于SCLK的第一个上升沿,如图3-6。

图3-6 数据格式(2)指令周期指令周期为串行传输数据的前16位,指令周期分为若干位段,如图3-7所示:图3-7 指令周期(3)读/写指令位数据流中的第一位是读/写指令位(WR/)。

当该位为高电平时,表示指令为读取指令,指令周期(前16位)完成时,部状态机使用所提供的信息解码要读取的部地址。

SDIO的方向由输入变为输出,由字长定义的适当数量的字从从器件移位出来。