TMS320C6713 DSP的SPI接口设计

- 格式:pdf

- 大小:158.98 KB

- 文档页数:9

TMS320C6713DSPEMIF接口与FPGA双口RAM接口设

计

胡彬;陈涛

【期刊名称】《电子质量》

【年(卷),期】2008(000)010

【摘要】文章给出了TMS320C6000 DSP通过EMIF接口与FPGA的片内接收模块进行数据通信的一个设计方案,DSP将处理完的数据通过EMIF接口传送到FPGA的片内接收模块双口RAM,双口RAM采用PING-PONG结构的设计.双口RAM完成对数据的接收.通过实验测试,该设计方案实现了数据的正确传输.

【总页数】4页(P32-35)

【作者】胡彬;陈涛

【作者单位】解放军理工大学通信工程学院研究生1队,江苏,南京,210007;解放军理工大学通信工程学院研究生1队,江苏,南京,210007

【正文语种】中文

【中图分类】TN79

【相关文献】

1.基于IP核双口RAM的FPGA与DSP EMIF的接口设计 [J], 王胜奎

2.双口RAM在PCI总线与AVR接口设计中的应用 [J], 邓江涛;傅煊

3.基于双口RAM的ARM与DSP通信接口设计 [J], 操虹;李臻;贾洪钢

4.基于双口RAM的DSP与PC104高速通信接口设计 [J], 张鹏超

5.基于双口RAM的DSP与PC104高速通信接口设计 [J], 张鹏超

因版权原因,仅展示原文概要,查看原文内容请购买。

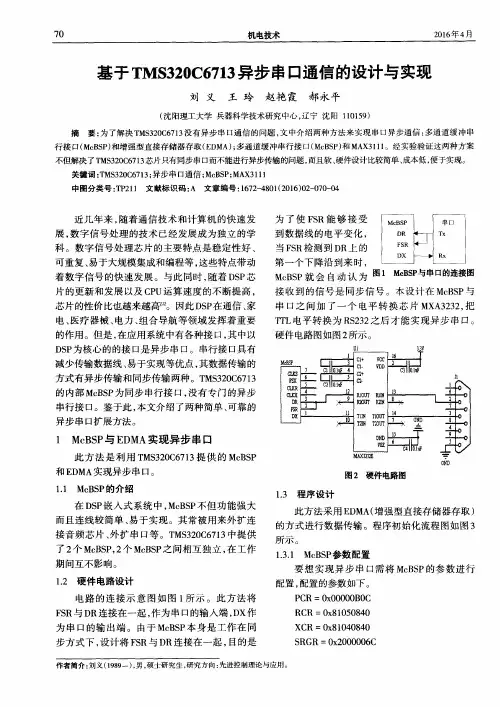

基于TMS320C6713的串行通信电路设计与实现王铮;朱勇;宾辰忠;马春波【期刊名称】《计算机与数字工程》【年(卷),期】2012(040)009【摘要】为了解决TMS320C6713与PC主机串口通信方式不一致的问题,文章选取MAXIM公司的MAX3111E芯片,设计了一种基于SPI协议的解决方案,包括硬件电路设计以及软件编程实现.%In order to solve the problem that serial communication is inconsistent between the TMS320C6713 and the host PC, this pa-per selects the MAX3111E chip produced by the MAXIM Corporation and presents a scheme based on the SPI protocol. This solution in-eludes the hardware circuit design and the software programming.【总页数】3页(P124-126)【作者】王铮;朱勇;宾辰忠;马春波【作者单位】桂林电子科技大学信息与通信学院桂林541004;桂林电子科技大学信息与通信学院桂林541004;桂林电子科技大学信息与通信学院桂林541004;桂林电子科技大学信息与通信学院桂林541004【正文语种】中文【中图分类】TP391【相关文献】1.基于CPLD的异步串行通信电路设计 [J], 胡王月;刘晓芳2.基于McBSP的TMS320C6713异步串行通信的实现 [J], 张云昌;张令弥;赵建洋3.基于Multisim 10和VHDL的异步串行通信电路的建模及仿真 [J], 黄德强;聂典4.通用异步串行通信电路的VHDL设计与实现 [J], 韩佩富;潘锋;赵新秋5.基于蓝牙透传的串行通信电路设计 [J], 朱艳生;刘金亭;武文杰;陈旺因版权原因,仅展示原文概要,查看原文内容请购买。

TMS320C6711和外部存储器接口的设计

段荣行;王平

【期刊名称】《信息技术》

【年(卷),期】2006(30)1

【摘要】DSP和外部存储器接口是TI公司的DSP系统设计中的重要环节.介绍了TMS320C6711外部扩展存储器接口设计,文中以Hynix公司的SDRAM存储器(HY57V653220B)为例,给出了具体的接口电路和相关寄存器的配置方法,并给出了EMIF初始化的程序源代码.

【总页数】3页(P37-39)

【作者】段荣行;王平

【作者单位】南昌大学信息工程学院,南昌,330029;南昌大学信息工程学院,南昌,330029

【正文语种】中文

【中图分类】TP333.2

【相关文献】

1.基于PXA255 XScale的外部存储器接口设计 [J], 李外云;刘锦高;黄振华

2.VC5402与外部存储器的接口设计 [J], 于传河;黄素贞

3.TMS320C6202外部扩展存储器接口设计 [J], 宋莹;季晓勇

4.YHFT-DSP外部同步存储器接口时序设计优化 [J], 黄彩霞;马剑武

5.高端SOC芯片的外部存储器接口设计 [J], 季爱慈;王世明;汪辉

因版权原因,仅展示原文概要,查看原文内容请购买。

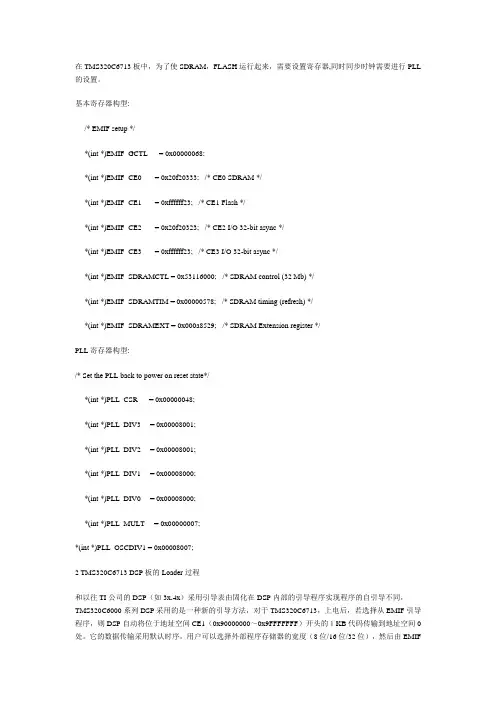

在TMS320C6713板中,为了使SDRAM,FLASH运行起来,需要设置寄存器,同时同步时钟需要进行PLL 的设置。

基本寄存器构型:/* EMIF setup */*(int *)EMIF_GCTL = 0x00000068;*(int *)EMIF_CE0 = 0x20f20333; /* CE0 SDRAM */*(int *)EMIF_CE1 = 0xffffff23; /* CE1 Flash */*(int *)EMIF_CE2 = 0x20f20323; /* CE2 I/O 32-bit async */*(int *)EMIF_CE3 = 0xffffff23; /* CE3 I/O 32-bit async */*(int *)EMIF_SDRAMCTL = 0x53116000; /* SDRAM control (32 Mb) */*(int *)EMIF_SDRAMTIM = 0x00000578; /* SDRAM timing (refresh) */*(int *)EMIF_SDRAMEXT = 0x000a8529; /* SDRAM Extension register */PLL寄存器构型:/* Set the PLL back to power on reset state*/*(int *)PLL_CSR = 0x00000048;*(int *)PLL_DIV3 = 0x00008001;*(int *)PLL_DIV2 = 0x00008001;*(int *)PLL_DIV1 = 0x00008000;*(int *)PLL_DIV0 = 0x00008000;*(int *)PLL_MULT = 0x00000007;*(int *)PLL_OSCDIV1 = 0x00008007;2 TMS320C6713 DSP板的Loader过程和以往TI公司的DSP(如3x,4x)采用引导表由固化在DSP内部的引导程序实现程序的自引导不同,TMS320C6000系列DSP采用的是一种新的引导方法,对于TMS320C6713,上电后,若选择从EMIF引导程序,则DSP自动将位于地址空间CE1(0x90000000~0x9FFFFFFF)开头的1KB代码传输到地址空间0处。

基于TMS320C6713与PC机的PCI总线高速数据传输TMS320C6713 是TI公司在TMS320C6711 的基础上推出的C6000系列新一代浮点DSP 芯片,它是目前为止C6000系列DSP 芯片中性能最高的一种。

TMS320C6713 可在255MHz的时钟频率下实现1800MIPS/1350MFLOPS的定点和浮点运算,因而可极大地满足通信、雷达、数字电视等高科技领域对信号处理实时性的要求。

同时其主机口(HPI)可灵活地和PCI总线控制器相连接。

而PC机则可通过PCI总线控制器直接访问TMS320C6713 的存储空间和外围设备,从而实现PC机与TMS320C6713 之间的高速数据传输。

在TMS320C6713 DSP 与PC机实现高速数据传输的方案中,可选用PLX公司的PCI9052 作为两者之间的接口;同时选用PLX公司的NM93CS46作为加载PCI9052 配置信息的串行EEPROM;而用TI公司的SN74CBTD3384 作为PCI9052 与TMS320C6713HPI 之间的电平转换芯片。

1TMS320C6713 的HPI 简介500)this.style.width=500;”border=“0” />1.1TMS320C6713 HPI 的接口信号TMS320C6713 的HPI 是一个16位宽的并行端口。

主机(上位机)掌管着该端口的主控权,可通过HPI 直接访问TMS320C6713 的存储空间和外围设备。

表1给出了TMS320C6713HPI 接口信号的基本特征。

下面对它们的具体工作方式进行说明:HD[15:0]:可以用作数据和地址的共用总线,通过HD[15:0]传送的数据包括控制寄存器的设置值、初始化的访问地址以及要传输的数据。

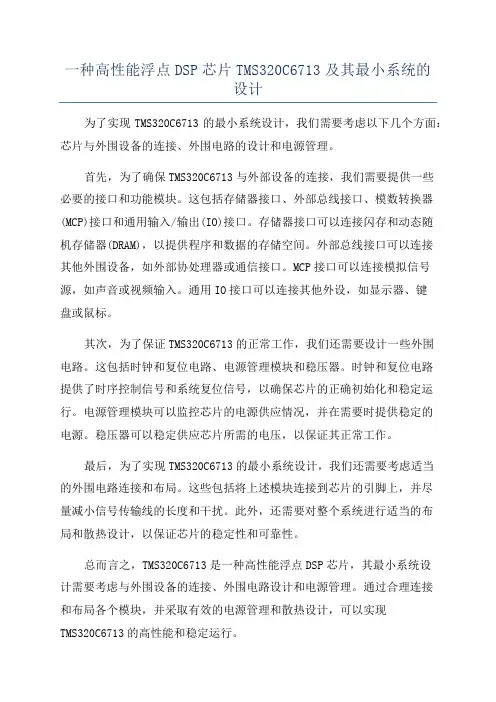

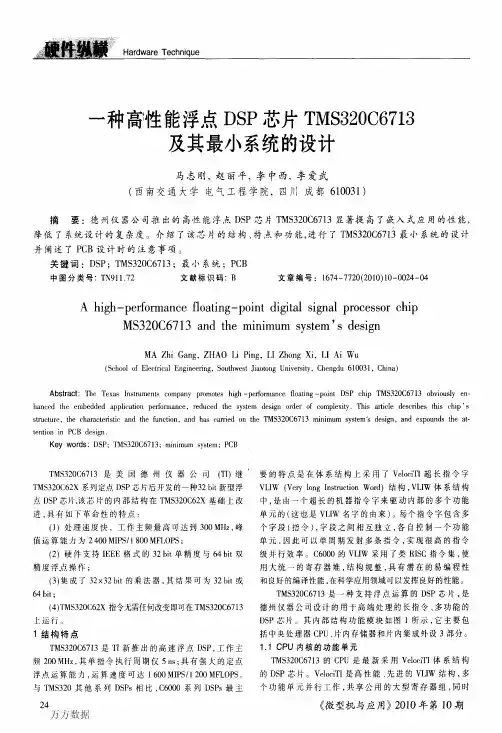

一种高性能浮点DSP芯片TMS320C6713及其最小系统的设计为了实现TMS320C6713的最小系统设计,我们需要考虑以下几个方面:芯片与外围设备的连接、外围电路的设计和电源管理。

首先,为了确保TMS320C6713与外部设备的连接,我们需要提供一些必要的接口和功能模块。

这包括存储器接口、外部总线接口、模数转换器(MCP)接口和通用输入/输出(IO)接口。

存储器接口可以连接闪存和动态随机存储器(DRAM),以提供程序和数据的存储空间。

外部总线接口可以连接其他外围设备,如外部协处理器或通信接口。

MCP接口可以连接模拟信号源,如声音或视频输入。

通用IO接口可以连接其他外设,如显示器、键盘或鼠标。

其次,为了保证TMS320C6713的正常工作,我们还需要设计一些外围电路。

这包括时钟和复位电路、电源管理模块和稳压器。

时钟和复位电路提供了时序控制信号和系统复位信号,以确保芯片的正确初始化和稳定运行。

电源管理模块可以监控芯片的电源供应情况,并在需要时提供稳定的电源。

稳压器可以稳定供应芯片所需的电压,以保证其正常工作。

最后,为了实现TMS320C6713的最小系统设计,我们还需要考虑适当的外围电路连接和布局。

这些包括将上述模块连接到芯片的引脚上,并尽量减小信号传输线的长度和干扰。

此外,还需要对整个系统进行适当的布局和散热设计,以保证芯片的稳定性和可靠性。

总而言之,TMS320C6713是一种高性能浮点DSP芯片,其最小系统设计需要考虑与外围设备的连接、外围电路设计和电源管理。

通过合理连接和布局各个模块,并采取有效的电源管理和散热设计,可以实现TMS320C6713的高性能和稳定运行。

基于TMS320C6713DSP的音乐喷泉控制系统引言音乐喷泉是现代科技与艺术的综合,利用喷泉来表现音乐的美,令人赏心悦目。

目前许多单位均推出了自己的音乐喷泉,取得了良好的效果。

但纵观这些音控产品,有的利用音乐的时域变化来控制喷泉,有的将音乐分成几个频段来控制喷泉的花型,且多采用低频、中频和高频三个频段来控制。

缺点是都没有在频域上很好地展现音乐,因此不能很好地体现音乐的内涵。

本设计针对这些问题,提出了一种新的方法来控制喷泉的变化,通过喷泉水柱的喷射高低来实时地展现音乐的频谱。

总体设计首先对音频信号进行放大、滤波、采样和A/D转换等预处理,经过DSP对音频信号进行傅立叶变换,可以得到音频信号的频谱,即各频率对应声音信号的强度,通过变频控制系统就可以将频谱图用喷泉的水柱表现出来,水柱的高低按线性比例反映音频信号的幅度。

设每次对音频信号的采样个数为n,系统总的结构如图(1)所示。

图1总体设计框图具体设计芯片及功能模块介绍TLV320AIC23(简称AIC23)是一个高性能的多媒体数字语音编解码器,它的内部ADC和DAC转换模块带有完整的数字滤波器。

内部有11个16位寄存器,控制接口具有SPI和I2C工作方式。

数据传输宽度可以是16位,20位,24位和32位,采样频率范围支持从8kHz到96kHz。

在ADC采集达到96kHz时噪音为90-dBA,能够高保真的保存音频信号。

在DAC转换达到96kHz时噪音为100-dBA,能够高品质的数字回放音频。

TMS320C6713是TI公司生产的一种高速数字信号处理器(DSP),他采用先进的超长指令字(VLIW)结构,每时钟周期可以执行8条32b指令,最高时钟频率可以达到300MHz,指令周期最小3.3ns。

该芯片具有丰富的片内存储器资源和多种片上外设,外部总的存储器地址空间最大512MB,数据宽度为32b,可以支持SBRAM,SDRAM,SRAM,FALSH和EPROM。

TMS320C6713和TLV320AIC32通信接口设计

杨侃;张宪起;刘鹏;陈淑凤

【期刊名称】《集成电路通讯》

【年(卷),期】2011(029)003

【摘要】根据水下声学探测信号处理卡实际运用,搭建了音频编解码芯片

TLV320AIC32与TMS320C6713之间通信的软硬件系统。

设计了AIC32和DSP 之间的硬件电路的连接,并设置了TLV320AIC32和TMS320C6713相关的寄存器。

实现了TLV320AIC32和TMS320C6713之间的通信,并给出了I2C写入TLV320AIC32和初始化McASP的相关操作代码,满足了设计要求。

这种接口设计具有广泛的通用性,可应用于各种相关的音频处理设备。

【总页数】5页(P24-28)

【作者】杨侃;张宪起;刘鹏;陈淑凤

【作者单位】中国兵器工业第214研究所,苏州215163

【正文语种】中文

【中图分类】TN911.72

【相关文献】

1.TMS320C6713 DSP的高速EMIF数据接口设计与实现 [J], 周顺燕;吴丹

2.TMS320C6713与DM9000A的接口设计与实现 [J], 倪启彦;石建波

3.TMS320C6713与TLV320AIC23B的接口设计及实现 [J], 倪启彦;石建波

4.基于TMS320C6713的嵌入式网络接口设计 [J], 黄林生;林岩

5.TMS320C6713 DSP与数字上变频器AD9857接口设计 [J], 罗晓莉;刘士彦;周劼

因版权原因,仅展示原文概要,查看原文内容请购买。

TMS320C6713 DSP的高速EMIF数据接口设计与实现周顺燕;吴丹

【期刊名称】《计算机测量与控制》

【年(卷),期】2010(018)007

【摘要】为减少数字控制系统的延迟时间,针对基于TMS320C6713 DSP的数字控制平台,设计了一种结构简单、易于控制的高速数据接口卡,包含16位、40MHz 采样率的A/D转换器以及16位、40MHz刷新率的D/A转换器,通过外部存储器接口EMIF实现DSP开发板与高速数据接口卡的控制信号传输与数据存取,并在CCS编泽平台上编程控制数据的存取以及外部存储器接口EMIF的读写时序;实验结果表明,数字控制系统的延迟时间可低至1.1 μs.

【总页数】3页(P1654-1656)

【作者】周顺燕;吴丹

【作者单位】清华大学,精密仪器及机械学系,摩擦学国家重点实验室,北京,100084;清华大学,精密仪器及机械学系,摩擦学国家重点实验室,北京,100084

【正文语种】中文

【中图分类】TP311

【相关文献】

1.基于TMS3206C6701高速浮点DSP的EMIF接口电路设计 [J], 郭在华;何建新

2.基于TMS320C6713和FPGA的高速实时采集系统的设计与实现 [J], 林林;侯春萍;闫浩;柳鑫;林甡

3.DSP EMIF与FPGA双口RAM高速通信实现 [J], 杨龙;李范鸣;刘士建

4.基于Zynq平台PCIE高速数据接口的设计与实现 [J], 杨亚涛;张松涛;李子臣;张明舵;曹广灿

5.一种基于高速多核DSP的激光捷联惯组软件框架设计与实现 [J], 段祉鸿;李朝阳;狄世超;陈令刚;赵琳

因版权原因,仅展示原文概要,查看原文内容请购买。

2006年第1期信息技术 Informa tion Technology 中图分类号:TP333.2 文献标识码:B 文章编号:1009-2552(2006)01-0037-03TMS320C6711和外部存储器接口的设计段荣行,王 平(南昌大学信息工程学院,南昌330029)摘 要:DSP和外部存储器接口是TI公司的DSP系统设计中的重要环节。

介绍了TMS320C6711外部扩展存储器接口设计,文中以Hynix公司的SDRAM存储器(HY57V653220B)为例,给出了具体的接口电路和相关寄存器的配置方法,并给出了EMIF初始化的程序源代码。

关键词:数字信号处理器;存储器接口;同步动态存储器;寄存器Design of TMS320C6711external memory interfaceDUAN Rong-xing,WANG Ping(School of Information Engineering,Nanchang University,Nanchang330029,China) Abstract:Memory interface is a very important link in the DSP syste m design of TI c ompany.This paper de-scribes the design of TMS320C6711external memory interface,and presents a specific interface circuit,the registers configuration and corresponding code of E MIF initialization on the HY57V653220B platform,which is Hynix company s SDRAM me mory.Key w ords:DSP;EMIF;SDRAM;register数字信号处理器芯片自20世纪80年代初诞生以来,在短短十多年时间里得到了飞速发展。

基于TMS320C6713的嵌入式网络接口设计

黄林生;林岩

【期刊名称】《电子测量技术》

【年(卷),期】2008(31)3

【摘要】嵌入式设备接入以太网已经成为目前研究的一个新领域,为了解决TI

C6000系列DSP与以太网的通信问题,本文首先介绍了一种新型的10/100 M自适应以太网控制器SMSC LAN9218I,然后在认真分析了DSP TMS3200C6713的EMIF(外部存储器接口)的基础上,给出了LAN9218I与TMS320C6713的硬件接口的电路设计,编写了LAN9218I网卡的驱动程序。

经过实验表明该网卡达到了预期的设计目的,实现了DSP接入以太网。

并且该网络接口应用广泛、可移植性强,可以经过修改在其他C6000系列DSP上实现软硬件移植。

【总页数】5页(P70-74)

【关键词】嵌入式设备;LAN9218I;TMS3200C6713;EMIF;硬件接口;驱动程序【作者】黄林生;林岩

【作者单位】北京航空航天大学自动化科学与电气工程学院

【正文语种】中文

【中图分类】TP393.11

【相关文献】

1.基于S3C2410的嵌入式网络接口设计 [J], 蔡树向;张丹

2.基于Rabbit2000的嵌入式以太网络接口设计与开发 [J], 郭宇红;任会峰;阳春华;

程朋胜

3.基于嵌入式NIOSⅡ的μC/TCP-IP网络接口设计 [J], 周乐;林广栋

4.基于DM9000的嵌入式系统的网络接口设计与实现 [J], 韩超;王可人

5.基于TCP/IP的嵌入式Web传感器网络接口设计 [J], 季雨辰;詹林

因版权原因,仅展示原文概要,查看原文内容请购买。