第五章触发器

- 格式:doc

- 大小:964.00 KB

- 文档页数:5

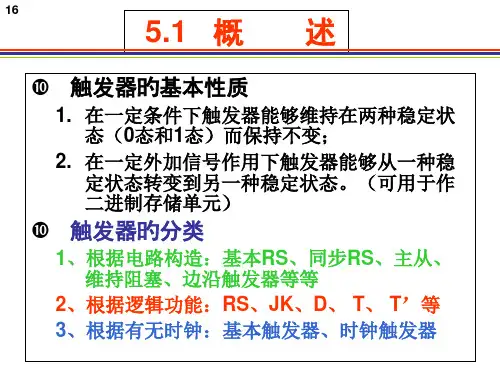

第五章触发器Flip-Flop1、触发器的定义和分类2、常用的触发器3、触发器的分析触发器(Flip-Flop):能够存储一位二进制数字信号的基本单元电路叫做触发器。

(P179引言部分)特点:具有“记忆”功能。

分析下面的电路:当A=0时,F=0某一时刻,由于外界的干扰使得A信号突然消失,此时,相当于A输入端悬空由电路结构得:F=1。

干扰发生前后, F的输出值发生的变化,故该电路没有“记忆”功能再看下面的电路:当A=0时,F=0。

某一时刻,由于外界的干扰使得A信号突然消失,此时,相当于A输入端悬空,但F端反馈回来的值仍然为0,由电路结构得:F=0。

说明该电路具有“记忆”功能。

其根本原因在于,该电路带有反馈。

触发器的分类:P179①按稳定工作状态分:双稳态、单稳态和无稳态(多谐振荡器)触发器。

本章仅讨论双稳态触发器。

②按结构分:主从结构和维持阻塞型(边沿结构)触发器。

本章仅讨论边沿触发器。

③按逻辑功能分:RS、JK、D、T和T’触发器。

本章重点讨论后四种。

常用触发器1、基本RS触发器①电路组成和逻辑符号基本RS触发器有两种:由与非门构成的和由或非门构成的。

我们以前者为例:输出端在正常情形下应是完全相反的两种逻辑状态,即两个稳态。

当Q=0时,称为“0态”;当Q=1时,称为“1态”。

②逻辑功能分析:A)当R=S=0时)(即1==SR11 QQQQ==⋅1可以保证门1的输出值不变。

QQQ=⋅1可以保证门2的输出值不变。

此时,门1和2的输出值均保持不变,称为:触发器的保持功能。

B)当S=0,R=1时)(即0,1==RS1111==⋅可以保证门1的输出值为0。

Q10==⋅Q可以保证门2的输出值为11此时,触发器的Q端始终输出低电平0,称为:触发器复位或触发器清0。

C)当S=1,R=0时)(即1,0==RS1111==⋅可以保证门1的输出值为1。

10==⋅Q可以保证门2的输出值为01此时,触发器的Q端始终输出高电平1,称为:触发器置位或触发器置1。

数字电子技术

第五章 触发器

1. 触发器是 。

2. 触发器有两个稳定的状态,可用来存储数码 和 (只要电源不断电)。

触发器按其逻辑功能可分为 触发器、 触发器、 触发器、 触发器等四种类型。

按触发方式可以分为: 、 、 。

3. 触发器有 个稳定状态,通常用 端的输出状态来表示触发器的状态。

4. 或非门构成的SR 锁存器的输入为 S =1、R =0,当输入S 变为0时,触发器的输出将会( )。

(A )置位 (B )复位 (C )不变

5. 与非门构成的SR 锁存器的输入为0 0==R S 、,当两输入的0状态同时消失时,触发器的输出状态为( )

(A )1 0==Q Q 、 (B )0 1==Q Q 、 (C )1 1==Q Q 、

(D )状态不确定 6. 触发器引入时钟脉冲的目的是( )

(A )改变输出状态

(B )改变输出状态的时刻受时钟脉冲的控制

(C )保持输出状态的稳定性

7. 与非门构成的SR 锁存器的约束条件是( )

(A )0=+R S (B )1=+R S (C )0=⋅R S (D )1=⋅R S

8. “空翻”是指( )

(A )在时钟信号作用时,触发器的输出状态随输入信号的变化发生多次翻转

(B )触发器的输出状态取决于输入信号

(C )触发器的输出状态取决于时钟信号和输入信号

(D )总是使输出改变状态

9. JK 触发器处于翻转时,输入信号的条件是( )

(A)J =0 , K =0 (B)J =0 , K =1 (C) J =1 , K =0 (D)J =1 , K =1

10. J =K =1时,JK 触发器的时钟输入频率为120Hz ,Q 输出为( )

(A)保持为高电平(B)保持为低电平

(C)频率为60Hz的方波(D)频率为240Hz的方波

*,则输入信号为()

11. JK触发器在CP的作用下,要使Q

Q

(A)J=K=0 (B)J=1 , K=0 (C)J=K=Q (D)J=0 , K=1

12. 下列触发器中,没有约束条件的是()

(A)SR锁存器(B)主从JK触发器(C)钟控RS触发器

13. 某JK触发器工作时,输出状态始终保持为1,则可能的原因有()(A)无时钟脉冲输入(B)J=K=1 (C)J=K=0 (D)J=1 , K=0 14. 归纳基本RS触发器、同步触发器、主从触发器和边沿触发器触发翻转的特点。

15. 在下图所示的逻辑图中,试画出在CP脉冲作用下Q1和Q2端的波形图,如果时钟脉冲的频率是4000Hz,那么Q1和Q2波形的频率各为多少?设初始状态Q1=Q2=0。

16. 设下图中各触发器的初始状态皆为Q=0,试求出在CP信号连续作用下各触发器的次态方程。

17. 已有JK触发器,请外接必要的门电路,将它变换成D触发器、T触发器。

18. 已有D触发器,请外接必要的门电路,将它变换成JK触发器、T触发器。

19. 查找资料,说明JK触发器和D触发器的芯片引脚功能。

画出将D触发器转换成T触发器的连线图。

20. 已知主从结构JK触发器输入端J、K和CP的电压波形如图所示,试画出

、端对应的波形。

设触发器的初始状态为Q=0。

Q Q

21. 图示电路中,已知CP和输入信号T的电压波形,试画出触发器输出端Q的电压波

形,设触发器的起始状态为Q=0。

22. 已知上升沿触发的D触发器输入端的波形如图所示,画出输出端Q的波形。

若为下降

沿触发,画出输出端Q的波形。

设初始状态为Q=0。

23. 已知D触发器各输入端的波形如图所示,试画出Q端的波形。

24. 如图所示为边沿D触发器构成的电路图,设触发器的初始状态Q1Q0=00,确定Q0 及

Q1在时钟脉冲作用下的波形。