8触发器_第五章(latch_flipflop)

- 格式:ppt

- 大小:1.69 MB

- 文档页数:60

锁存器Latch和触发器Flip-flop有何区别锁存器Latch概述锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。

锁存,就是把信号暂存以维持某种电平状态。

锁存器的最主要作用是缓存,其次完成高速的控制器与慢速的外设的不同步问题,再其次是解决驱动的问题,最后是解决一个I/O口既能输出也能输入的问题。

锁存器是利用电平控制数据的输入,它包括不带使能控制的锁存器和带使能控制的锁存器。

锁存器Latch结构latch:锁存器,是由电平触发,结构图如下:锁存器latch的优缺点优点:1、面积比ff小门电路是构建组合逻辑电路的基础,而锁存器和触发器是构建时序逻辑电路的基础。

门电路是由晶体管构成的,锁存器是由门电路构成的,而触发器是由锁存器构成的。

也就是晶体管-》门电路-》锁存器-》触发器,前一级是后一级的基础。

latch完成同一个功能所需要的门较触发器要少,所以在asic中用的较多。

2、速度比ff快用在地址锁存是很合适的,不过一定要保证所有的latch信号源的质量,锁存器在CPU设计中很常见,正是由于它的应用使得CPU的速度比外部IO部件逻辑快许多。

缺点:1、电平触发,非同步设计,受布线延迟影响较大,很难保证输出没有毛刺产生2、latch将静态时序分析变得极为复杂触发器Flip-flop结构lip-flop:触发器,是时钟边沿触发,可存储1bitdata,是register的基本组成单位,结构图如下:flip-flop的优缺点优点:1、边沿触发,同步设计,不容易受毛刺的印象2、时序分析简单缺点:1、面积比latch大,消耗的门电路比latch多锁存器Latch和触发器flipflop的区别1、锁存器Latch和触发器flipflop锁存器能根据输。

锁存器和D触发器D触发器是指由时钟边沿触发的存储器单元,锁存器指一个由信号而不是时钟控制的电平敏感的设备。

锁存器通过锁存信号控制,不锁存数据时,输出端的信号随输入信号变化,就像信号通过缓冲器一样,一旦锁存信号起锁存作用,则数据被锁住,输入信号不起作用。

锁存器和D触发器实现的逻辑功能基本相同,都是暂存数据。

由与非门搭建的话,锁存器所耗用的逻辑资源比D触发器少,所以使用锁存器有更高的集成度,但锁存器有一下缺点:(1)对毛刺敏感,毛刺信号会传递下去,无异步复位端,不能在芯片上电时处在一个确定的状态;(2)会使静态时序分析变得复杂,可测性不好,不利于设计的可重用,所以当今的ASIC设计中除了CPU这种甚高速电路,一般不提倡使用锁存器;(3)FP GA器件中有大量的D触发器结构而没有锁存器这种现成的结构,使用锁存器会更耗资源,如何避免使用锁存器:(1)时序逻辑电路中,可用带使能端的D触发器实现;(2)在组合进程中赋默认值;(3)对所有输入条件赋输入值,以覆盖所有条件分支(特别是i f..else..和case结构);(4)避免产生组合电路反馈,组合电路反馈会引起精确静态时序分析难以实现等一系列问题。

在有些设计中,不可避免的需要用到锁存器,如在P CI接口设计中要完成P CI规范中对Reset功能的定义。

可以通过多位选择器,有测试模式管脚做选择控制位来使设计是可测试的。

"触发器" 泛指一类电路结构, 它可以由触发信号(如: 时钟, 置位, 复位等) 改变输出状态, 并保持这个状态直到下一个或另一个触发信号来到时, 触发信号可以用电平或边沿操作. 锁存器是触发器的一种应用类型. 在CMOS 电路中典型的锁存器(LATCH) 是由两个反相器和两个数据开关组成, 其中输入数据开关在闸门(G ATE) 电平操作下开启送入数据. 当闸门关闭后, 另一个数据开关开启, 使两个反相器的串联闭合, 形成RS 触发器类型的正反馈电路, 数据保持在这个RS 触发器中, 以达到锁存的目的, 直到下一个闸门周期.由两个这样的锁存器可以级联成主从结构, 并执行互补的操作. 即前一个送入数据时, 后一个保持先前的数据, 而前一个锁存数据时, 后一个送入这个新数据到输出端. 形成一个边沿触发的D 触发器, 而闸门控制信号成为触发器的时钟. 也可以认为D 触发器是用时钟边沿锁存数据的, 但习惯上不称其为锁存器LATCH.在CMOS 芯片内部经常使用锁存器, 但是在P CB 板级结构上, 建议用触发器在时钟边沿上锁存数据. 这是因为在锁存器闸门开启期间数据的变化会直接反映到输出端, 所以要注意控制闸门信号的脉冲宽度. 而对于触发器, 只考虑时钟的边沿latch和flip-flop都是时序逻辑,区别为:latch同其所有的输入信号相关,当输入信号变化时latch就变化,没有时钟端;flip-flop受时钟控制,只有在时钟触发时才采样当前的输入,产生输出。

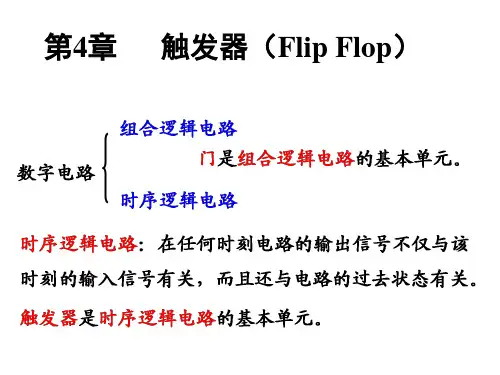

第五章触发器Flip-Flop1、触发器的定义和分类2、常用的触发器3、触发器的分析触发器(Flip-Flop):能够存储一位二进制数字信号的基本单元电路叫做触发器。

(P179引言部分)特点:具有“记忆”功能。

分析下面的电路:当A=0时,F=0某一时刻,由于外界的干扰使得A信号突然消失,此时,相当于A输入端悬空由电路结构得:F=1。

干扰发生前后, F的输出值发生的变化,故该电路没有“记忆”功能再看下面的电路:当A=0时,F=0。

某一时刻,由于外界的干扰使得A信号突然消失,此时,相当于A输入端悬空,但F端反馈回来的值仍然为0,由电路结构得:F=0。

说明该电路具有“记忆”功能。

其根本原因在于,该电路带有反馈。

触发器的分类:P179①按稳定工作状态分:双稳态、单稳态和无稳态(多谐振荡器)触发器。

本章仅讨论双稳态触发器。

②按结构分:主从结构和维持阻塞型(边沿结构)触发器。

本章仅讨论边沿触发器。

③按逻辑功能分:RS、JK、D、T和T’触发器。

本章重点讨论后四种。

常用触发器1、基本RS触发器①电路组成和逻辑符号基本RS触发器有两种:由与非门构成的和由或非门构成的。

我们以前者为例:输出端在正常情形下应是完全相反的两种逻辑状态,即两个稳态。

当Q=0时,称为“0态”;当Q=1时,称为“1态”。

②逻辑功能分析:A)当R=S=0时)(即1==SR11 QQQQ==⋅1可以保证门1的输出值不变。

QQQ=⋅1可以保证门2的输出值不变。

此时,门1和2的输出值均保持不变,称为:触发器的保持功能。

B)当S=0,R=1时)(即0,1==RS1111==⋅可以保证门1的输出值为0。

Q10==⋅Q可以保证门2的输出值为11此时,触发器的Q端始终输出低电平0,称为:触发器复位或触发器清0。

C)当S=1,R=0时)(即1,0==RS1111==⋅可以保证门1的输出值为1。

10==⋅Q可以保证门2的输出值为01此时,触发器的Q端始终输出高电平1,称为:触发器置位或触发器置1。

锁存器(latch)、触发器(flip-flop)〇、时钟、锁存器、触发器a)时钟(clock pulse, CP):其信号周期性变化b)课本已声明,一般将锁存器和触发器统称触发器。

3.1节的“触发器”其实为锁存器。

c)触发器:只有时钟信号触发(trigger)它,才有可能引起它的输出状态改变。

i.由时钟信号触发引起输出状态改变,并且该状态在下一次被触发之前始终不会被改变的器件ii.时序上容易分析控制,对脉冲边沿敏感,一般没有毛刺;不能即时响应。

d)锁存器:时钟信号的触发并不是它输出状态改变的必要条件(使能与触发不同;可由时钟信号使能)i.输出状态不是由时钟信号触发,或者虽然由时钟信号触发,但在时钟信号的某个电平下,输入会(即时地)随着输入而改变的器件。

ii.即时响应(相对于触发器),对脉冲敏感,逻辑门数量少;易产生毛刺,时序分析困难,可能有些输入状态不被允许。

一、R S(set/reset)锁存器a)电路图、输入分析以左图为例分析输入:1. /R=0,/S=0Q=/Q=1。

锁存的Q、/Q应是互补的输出,而现在两个输出相等。

触发器的次态取决于哪个输入先回到0。

这种情况对于锁存器来讲是不允许的;2./R=0,/S=1由于/S=1,故Q的状态取决于/Q的状态,而由于/R=0,/Q=1,故Q=0,所以说当/R=0,/S=1时触发器被置0;3./R=1,/S=0与上一种情况相反,其Q=1,/Q=0,即触发器被置1;4./R=1,/S=1由于输入为低电平有效,而现在输入皆为高电平,输出状态保持不变。

状态表:Qn+1=S+/RQn/S+/R=1激励表:以现态和次态为自变量,输出为因变量的“真值表”。

在已知状态变化的情况下找出实现该状态变化的激励条件。

c)带同步时钟的RS锁存器E=1时,锁存器的输出才受R、S控制。

E可为时钟脉冲CP。

二、J K、D、T锁存器a)JK:JK=1时Q n+1=/Q n。

其余与RS相同。