vhdl array用法

- 格式:doc

- 大小:11.77 KB

- 文档页数:4

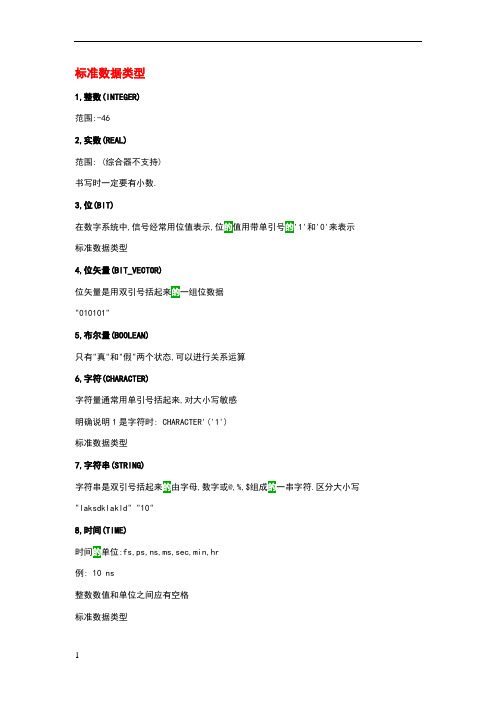

标准数据类型1,整数(INTEGER)范围:-462,实数(REAL)范围: (综合器不支持)书写时一定要有小数.3,位(BIT)在数字系统中,信号经常用位值表示,位值用带单引号'1'和'0'来表示标准数据类型4,位矢量(BIT_VECTOR)位矢量是用双引号括起来一组位数据"010101"5,布尔量(BOOLEAN)只有"真"和"假"两个状态,可以进行关系运算6,字符(CHARACTER)字符量通常用单引号括起来,对大小写敏感明确说明1是字符时: CHARACTER'('1')标准数据类型7,字符串(STRING)字符串是双引号括起来由字母,数字或@,%,$组成一串字符.区分大小写"laksdklakld" "10"8,时间(TIME)时间单位:fs,ps,ns,ms,sec,min,hr例: 10 ns整数数值和单位之间应有空格标准数据类型9,错误等级(SEVERITY LEVEL)在VHDL仿真器中,错误等级用来表示系统状态,它共有4种:NOTE(注意)WARNING(警告)ERROR(错误)FAILURE(失败)标准数据类型10,自然数(NATURAL) 正整数(POSITIVE)自然数是整数一个子类型,包括0和正整数;正整数也是整数一个子类型.只能是正整数数据除定义类型外,有时还需要定义约束范围.INTEGER RANGE 100 DOWNTO 0BIT_ VECTOR (3 DOWNTO 0)REAL RANGE TOIEEE定义的逻辑位与矢量在IEEE程序包std_logic_1164中定义了两个非常重要数据类型:1 ,std_logic取值:0,1,Z,X,W,L,HZ:高阻 X:不定 W:弱信号不定L:弱信号0 H:弱信号12,Std_logic_vector注意1,在使用"std_logic"和"std_logic_vector"时,在程序中必须声明库及程序包说明语句,即LIBRARY ieee和这两句在程序中必不可少.2, std_logic有多个取值,与BIT不同,在编程时应特别注意,需要考虑全所有情况.用户自定义的数据类型1,枚举类型格式:TYPE 数据类型名 IS(元素,元素,…);TYPE STD_LOGIC IS('U','X','0','1','Z','W','L','H','-');TYPE week IS (Sun,Mon,Tue,wed,Thu,Fri,Sat);TYPE color IS (red,green,yellow,blue)TYPE lift_state IS(stopon1,doorpeen,doorclose, doorwait1, doorwait2, doorwait3, doorwait4, doorwait5,up,down,stop)枚举类型声明TYPE color IS (red,green,yellow,blue);VARIABLE A:COLOR;SIGNAL B:COLOR;A:=RED;B<=YELLOW;TYPE lever IS ('0','1','z');SIGNAL V:lever;V<='1';用户自定义数据类型2,整数(INTEGER)格式:TYPE 数据类型名 IS 数据类型定义约束范围例 TYPE digit IS INTEGER RANGE 0 TO 9VARIABLE A:DIGIT;A:=5;A:=28;用户自定义数据类型3,实数(REAL)格式:TYPE 数据类型名 IS 数据类型定义约束范围TYPE current IS REAL RANGE -1E4 TO 1E4VARIABLE A:CURRENT;A:=1E3;A:=1E10;用户自定义数据类型4,数组(ARRAY)格式:TYPE 数据类型名 IS ARRAY 范围 OF 原数据类型名; 例:TYPE word IS ARRAY (1 TO 8) OF STD_LOGIC;TYPE word IS ARRAY (INTEGER 1 TO 8) OF STD_LOGIC; 数组常在总线,ROM和RAM中使用.用户自定义数据类型5,记录(RECODE) 类型将不同数据类型放在一块,就是记录类型数据格式:TYPE 记录类型名 IS RECORD元素名:数据类型名;元素名:数据类型名;::END RECORD[记录类型名];记录(RECODE) 类型例:TYPE bank IS RECORDaddr0: STD_LOGIC_VECTOR(7 DOWNTO 0);addr1: STD_LOGIC_VECTOR(7 DOWNTO 0);r0: INTEGER;END RECORD;记录(RECODE) 类型例:CONSTANT LEN:integer:=100;TYPE array logic IS ARRAY (99 downto 0)OF STD_LOGIC_VECTOR(7 DOWNTO 0) TYPE table IS RECORDa: array logic;b: STD_LOGIC_VECTOR(7 DOWNTO 0);c: integer RANGE 0 to len ;END RECORD;数据类型的转换数据类型转换函数有VHDL语言包提供例如:STD_LOGIC_1164,STD_LOGIC_ARITHSTD_LOGIC_UNSIGNED等等函数说明1、STD_LOGIC_1164包TO_STDLOGIC_VECTOR(A)TO_BITVECTOR(A)TO_LOGIC(A)TO_BIT(A)由BIT_VECTOR转换成STD_LOGIC_VECTOR由STD_LOGIC_VECTOR转换成BIT_VECTOR由BIT转换成STD_LOGIC由STD_LOGIC转换成BIT2、STD_LOGIC_ARITH包CONV_STD_LOGIC_VECTOR(A,位长)CONV_INTEGER(A)由INTEGER,UNSIGNED和SIGNED转换成STD_LOGIC_VECTOR由UNSIGNED和SIGNED转换成INTEGER3、STD_LOGIC_UNSIGNED包CONV_INTEGER(A)_STD_LOGIC_VECTOR转换成INTEGERVHDL属性VHDL没有一般程序语言中那些运算类标准函数,取而代之是多种能反映和影响硬件行为属性.属性在描述时序电路VHDL设计文件中几乎处处可见,如检测上升沿,下降沿,知道前一次发生事件.VHDL属性属性指是关于实体,结构体,类型及信号一些特征.有属性对综合(设计)非常有用. VHDL属性可分为数值类属性,函数类属性,范围类属性,信号类属性,类型类属性.其引用一般形式为:对象'属性.数值类属性数值类属性用于返回数组,块或一般数据有关值,如边界,数组长度等信息.对一般数据有4种数值类属性:对象类型左边界,右边界,上边界,下边界,对应关键字是:LEFT,RIGHT,HIGH,LOW.数组在加一个长度属性LENGTH.数值类属性sdown:IN std_logic_vector(8 DOWNTO 0);sup:IN std_logic-vector(0 to 8);这两个信号各属性值如下:sdown'left=8; sdown'right=0; sdown'low=0; sdown'high=8; sdown'length=9;sup'left=0; sup'right=8; sup'low=0; sup'high=8; sup'length=9;数值类属性TYPE bit32 IS ARRAY (63 DOWNTO 32)OF BITVARIABLE:left_range,right_range,up_range,low_range,len:INTEGER;BEGINleft-range:=bit32'LEFT; --return 63right-range:=bit32'RIGHT; --return 32up-range:=bit32'HIGH; --return 63low-range:=bit32'LOW; --return 32len:=bit32'LENGTH; --return 32函数类属性信号属性函数属于函数类属性,用来返回有关信号行为功能信息.共有5种信号属性函数,分别是: 'EVENT(事件) ; ' ACTIVE(活跃);' LAST_EVENT (最近一次事件到现在经过多少时间);' LAST_ACTIVE (最近一次活跃到现在经过多少时间); ' LAST_VALUE(信号变化前取值是什么)EVENTEVENT:它值为布尔型,取值为TRUE或FALSE;如果刚好有事件发生在该属性所附着信号上(即信号有变化),取值为TRUE.利用此属性可决定时钟边沿是否有效,即时钟是否发生.EVENTSIGNAL clk: IN std_logic;clk 'EVENT AND clk='1'clk='1' AND clk 'EVENTclk 'EVENT AND clk='0'clk='0' AND clk 'EVENTrising_edge(clk) falling_edge(clk)EVENT 和ACTIVEEVENT 要求信号值发生变化;1到0,0到1ACTIVE 信号值任何变化,1到1,1 到0,0到1,0到0;所有事件都是活跃,但并非所有活跃都是事件范围类属性'RANGE属性,其生成一个限制性数据对象范围.例 SIGNAL data_bus:std_logic_vector(15 DOWNTO 0);data_bus 'RANGE=15 downto 0用VHDL语言设计分频电路,把1KHZ的时钟分至约1HZ左右的时钟LIBRARY IEEE;USEENTITY FreDevider ISPORT(Clkin:IN Std_Logic;Clkout:OUT Std_Logic);END;ARCHITECTURE Devider OF FreDevider IS CONSTANT N:Integer:=499;signal counter:Integer range 0 to N; signal Clk:Std_Logic;BEGINPROCESS(Clkin)beginIF rising_edge(Clkin)THENIF Counter=N thencounter<=0;Clk<=not clk;elsecounter<=counter+1;end if;end if;end process;clkout<=clk;end;。

VHDL语法简单总结一个VHDL程序代码包含实体(entity)、结构体(architecture)、配置(configuration)、程序包(package)、库(library)等。

一、数据类型1.用户自定义数据类型使用关键字TYPE,例如:TYPE my_integer IS RANGE -32 TO 32;–用户自定义的整数类型的子集TYPE student_grade IS RANGE 0 TO 100;–用户自定义的自然数类型的子集TYPE state IS (idle, forward, backward, stop);–枚举数据类型,常用于有限状态机的状态定义一般来说,枚举类型的数据自动按顺序依次编码。

2.子类型在原有已定义数据类型上加一些约束条件,可以定义该数据类型的子类型。

VHDL不允许不同类型的数据直接进行操作运算,而某个数据类型的子类型则可以和原有类型数据直接进行操作运算。

子类型定义使用SUBTYPE关键字。

3.数组(ARRAY)ARRAY是将相同数据类型的数据集合在一起形成的一种新的数据类型。

TYPE type_name IS ARRAY (specification) OF data_type;–定义新的数组类型语法结构SIGNAL signal_name: type_name [:= initial_value];–使用新的数组类型对SIGNAL,CONSTANT, VARIABLE进行声明例如:TYPE delay_lines IS ARRAY (L-2 DOWNTO 0) OF SIGNED (W_IN-1 DOWNTO 0);–滤波器输入延迟链类型定义TYPE coeffs IS ARRAY (L-1 DOWNTO 0) OF SIGNED (W_COEF-1 DOWNTO 0);–滤波器系数类型定义SIGNAL delay_regs: delay_lines; –信号延迟寄存器声明CONSTANT coef: coeffs := ( ); –常量系数声明并赋初值4.端口数组在定义电路的输入/输出端口时,有时需把端口定义为矢量阵列,而在ENTITY中不允许使用TYPE进行类型定义,所以必须在包集(PACKAGE)中根据端口的具体信号特征建立用户自定义的数据类型,该数据类型可以供包括ENTITY在内的整个设计使用。

VHDL语法(yǔfǎ)简单总结VHDL语法简单(jiǎndān)总结VHDL语法(yǔfǎ)简单总结一个(yī ɡè)VHDL程序代码包含实体(shítǐ)(entity)、结构(jiégòu)体(architecture)、配置(pèizhì)(configuration)、程序包(package)、库(library)等。

一、数据类型1.用户自定义数据类型使用关键字TYPE,例如:TYPE my_integer IS RANGE -32 TO 32;–用户自定义的整数类型的子集TYPE student_grade IS RANGE 0 TO 100;–用户自定义的自然数类型的子集TYPE state IS (idle, forward, backward, stop);–枚举数据类型,常用于有限状态机的状态定义一般来说,枚举类型的数据自动按顺序依次编码。

2.子类型在原有已定义数据类型(lèixíng)上加一些约束条件,可以定义(dìngyì)该数据类型的子类型。

VHDL不允许不同类型的数据直接进行操作运算,而某个数据类型的子类型则可以和原有类型数据直接进行操作运算。

子类型定义使用(shǐyòng)SUBTYPE关键字。

3.数组(ARRAY)ARRAY是将相同数据类型的数据集合在一起(yīqǐ)形成的一种新的数据类型。

TYPE type_name IS ARRAY (specification) OF data_type;–定义新的数组类型(lèixíng)语法结构SIGNAL signal_name: type_name [:=initial_value];–使用新的数组类型对SIGNAL,CONSTANT, VARIABLE进行声明例如:TYPE delay_lines IS ARRAY (L-2 DOWNTO 0) OF SIGNED (W_IN-1 DOWNTO 0);–滤波器输入延迟链类型定义TYPE coeffs IS ARRAY (L-1 DOWNTO 0) OF SIGNED (W_COEF-1 DOWNTO 0);–滤波器系数(xìshù)类型定义SIGNAL delay_regs: delay_lines; –信号延迟(yánchí)寄存器声明CONSTANT coef: coeffs := ( ); –常量(chángliàng)系数声明并赋初值4.端口数组在定义电路的输入/输出端口时,有时需把端口定义为矢量阵列,而在ENTITY中不允许使用TYPE进行类型定义,所以(suǒyǐ)必须在包集(PACKAGE)中根据端口的具体信号特征建立用户自定义的数据类型,该数据类型可以供包括ENTITY在内的整个设计使用。

VHDL数组的使⽤--定义matrix_index 为数组TYPE matrix_index is array (3 downto 0) of std_logic_vector(7 downto 0);SIGNAL a: matrix_index;--定义了数组a[4],即数组元素为a[0],a[1],a[2],a[3]constant R : matrix_index:=( x"15", x"0F", x"0A", x"06");--定义了常数数组R[4]--使⽤时跟C语⾔中⼀样,加下标就可以了,上⾯是⽤downto定义了⽅向,故R[0]是最后⼀项,如在R数组中R[0]=X"06",R[3]=X"15"⼀维数组(⼜叫向量),直接定义,如: avariable SHUZU:std_logic_vector(3 downto 0);---shuzu是四位向量,变量赋值:shuzu:="1111";shuzu(3):='1;⼆维数组:type matrix_type IS array (7 downto 0) of std_logic_vector (7 downto 0signal matix : matrix_type; -----matix 是⼆维8*8数组,信号赋值:matrix(3)(4)<='1';matrix(2)<="11111111";matrix(1 downto 0)(2)<="11";参考程序---------------------------------------library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;ENTITY shift_row_inv ISPORT(shiftrow_in : IN STD_LOGIC_VECTOR(127 DOWNTO 0);shiftrow_out : OUT STD_LOGIC_VECTOR(127 DOWNTO 0));END shift_row_inv;ARCHITECTURE beh OF shift_row_inv IS-- type describing the byte array consisting of 16 byte matrix arrayTYPE matrix_index is array (15 downto 0) of std_logic_vector(7 downto 0);SIGNAL b, c : matrix_index;BEGIN--initial mapping of input into a byte matrix array named bmatrix_mapping:PROCESS(shiftrow_in)BEGINFOR i IN 15 DOWNTO 0 LOOPb(15-i) <= shiftrow_in(8*i+7 DOWNTO 8*i);END LOOP;END PROCESS matrix_mapping;--shift row transformation-- b(i) --> c(i)---- | 0 4 8 12 | | 0 4 8 12 | (no shift)-- | 1 5 9 13 | ==> | 13 1 5 9 | ( 1 right shift)-- | 2 6 10 14 | | 10 14 2 6 | ( 2 right shift)-- | 3 7 11 15 | | 7 11 15 3 | ( 3 right shift)--shifted first columnc(0) <= b(0);c(1) <= b(13);c(2) <= b(10);c(3) <= b(7);--shifted second columnc(4) <= b(4);c(5) <= b(1);c(6) <= b(14);c(7) <= b(11);--shfited third columnc(8) <= b(8);c(9) <= b(5);c(10) <= b(2);c(11) <= b(15);--shifted forth columnc(12) <= b(12);c(13) <= b(9);c(14) <= b(6);c(15) <= b(3);--mapping temporary c vector into shiftedrow output matrix_mapping_back:PROCESS(c)BEGINFOR i IN 15 DOWNTO 0 LOOPshiftrow_out(8*i+7 DOWNTO 8*i) <= c(15-i);END LOOP;END PROCESS matrix_mapping_back;END beh;。

vhdl array用法

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,广泛应用于数字电路设计和仿真。

在VHDL 中,数组(array)是一种非常常用的数据结构,它允许在单个信号名称下存储多个值。

这篇文章将详细介绍VHDL中的数组用法,重点关注中括号的使用,并逐步回答相关问题。

1. 什么是VHDL中的数组?

数组是一种用于存储多个值的数据结构。

在VHDL中,数组可以是一维、二维或多维的,并且可以包含指定数量的元素。

2. 如何声明一个一维数组?

在VHDL中,可以使用以下语法声明一个一维数组:

type array_name is array (range) of element_type;

其中,`array_name`是数组名称,`range`是数组的范围,可以是确定的或变量的,而`element_type`是数组元素的数据类型。

3. 如何声明一个二维数组?

声明一个二维数组的语法如下:

type array_name is array (range1) of element_type_1;

type array2d_name is array (range2) of array_name;

其中,`range1`和`range2`是数组的范围,`element_type_1`是数组元素的数据类型。

4. 如何初始化数组的元素?

可以使用以下方式初始化数组的元素:

array_name := (value1, value2, value3, ...);

其中,`array_name`是数组名称,`value1`、`value2`等是要初始化的元素值。

5. 如何访问数组的元素?

可以使用以下方式访问数组的元素:

array_name(index);

其中,`array_name`是数组名称,`index`是要访问的元素的索引。

6. 数组的索引如何定义?

数组的索引可以是任何VHDL支持的数据类型,如整数或枚举类型。

索引可以

是递增或递减的,也可以不连续。

7. 如何遍历数组的元素?

可以使用Foreach循环遍历数组的元素,语法如下:

for index in array_name'range loop

可以访问array_name(index)

在此处执行循环体的代码

end loop;

其中,`array_name`是数组名称,`index`是索引的变量。

8. 数组的大小是否可以动态改变?

在VHDL中,一旦数组被声明,其大小是固定的,不可以动态改变。

如果需要改变数组的大小,需要重新声明一个新的数组。

9. 数组与信号的区别是什么?

数组和信号都可以用于存储多个值,但数组是一个在仿真过程中用于存储数据的变量,而信号则用于描述数字电路中的连续传输的数据。

10. 如何在VHDL中使用数组?

在VHDL中,数组常用于存储和处理多个数据,并使代码更清晰、更具可读性。

可以将数组用于存储寄存器状态、处理多个输入/输出等场景。

总结:

VHDL中的数组是一种非常有用的数据结构,它可以通过一个信号名称存储多个值,并且提供了灵活的索引和遍历方式。

本文介绍了声明一维和二维数组的语法,讨论了数组元素的初始化和访问方法,并解答了一些与数组相关的常见问题。

通过充分理解VHDL中的数组用法,可以更好地应用它们来实现复杂的数字电路设计。