VHDL的基本语法-完整版

- 格式:pdf

- 大小:14.78 MB

- 文档页数:125

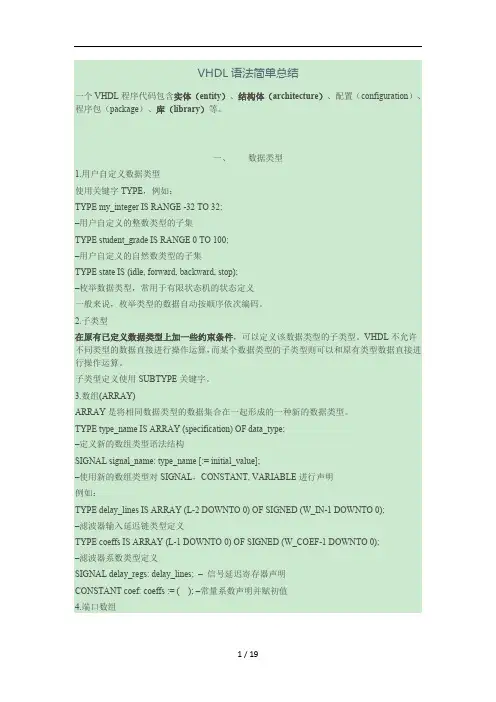

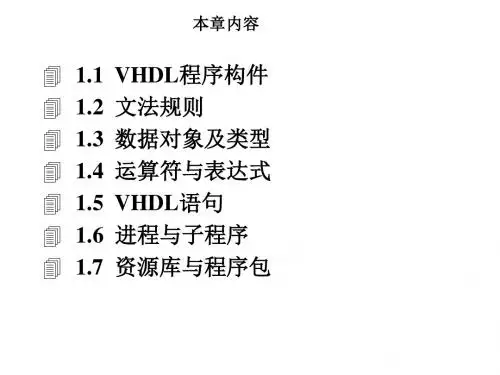

VHDL语法简单总结一个VHDL程序代码包含实体(entity)、结构体(architecture)、配置(configuration)、程序包(package)、库(library)等。

一、数据类型1.用户自定义数据类型使用关键字TYPE,例如:TYPE my_integer IS RANGE -32 TO 32;–用户自定义的整数类型的子集TYPE student_grade IS RANGE 0 TO 100;–用户自定义的自然数类型的子集TYPE state IS (idle, forward, backward, stop);–枚举数据类型,常用于有限状态机的状态定义一般来说,枚举类型的数据自动按顺序依次编码。

2.子类型在原有已定义数据类型上加一些约束条件,可以定义该数据类型的子类型。

VHDL不允许不同类型的数据直接进行操作运算,而某个数据类型的子类型则可以和原有类型数据直接进行操作运算。

子类型定义使用SUBTYPE关键字。

3.数组(ARRAY)ARRAY是将相同数据类型的数据集合在一起形成的一种新的数据类型。

TYPE type_name IS ARRAY (specification) OF data_type;–定义新的数组类型语法结构SIGNAL signal_name: type_name [:= initial_value];–使用新的数组类型对SIGNAL,CONSTANT, VARIABLE进行声明例如:TYPE delay_lines IS ARRAY (L-2 DOWNTO 0) OF SIGNED (W_IN-1 DOWNTO 0);–滤波器输入延迟链类型定义TYPE coeffs IS ARRAY (L-1 DOWNTO 0) OF SIGNED (W_COEF-1 DOWNTO 0);–滤波器系数类型定义SIGNAL delay_regs: delay_lines; –信号延迟寄存器声明CONSTANT coef: coeffs := ( ); –常量系数声明并赋初值4.端口数组在定义电路的输入/输出端口时,有时需把端口定义为矢量阵列,而在ENTITY中不允许使用TYPE进行类型定义,所以必须在包集(PACKAGE)中根据端口的具体信号特征建立用户自定义的数据类型,该数据类型可以供包括ENTITY在内的整个设计使用。

VHDL(VHSIC Hardware Description Language)是一种硬件描述语言,用于描述数字电路和系统。

它是由美国国防部(DOD)于20世纪80年代初期的VHSIC(Very High Speed Integrated Circuits)项目中开发的。

VHDL的基本语法包括一些常用的关键字和结构,其中ifdef是其中之一。

ifdef是VHDL中的一个条件编译指令,用于根据给定的条件来判断是否包含某段代码。

在VHDL中,ifdef语句的基本语法如下:```vhdl`ifdef condition-- code to be included if condition is true`else-- code to be included if condition is false`endif```在上面的代码中,condition是一个条件表达式,可以是一个参数、宏定义或者其他已经定义过的条件。

如果condition为真,则会编译`ifdef和`endif之间的代码;如果condition为假,则会编译`else和`endif之间的代码。

使用ifdef可以让我们根据不同的条件来控制代码的编译和包含,这在一些复杂的项目中非常有用。

下面是使用ifdef的一个简单示例:```vhdl`ifdef DEBUGreport "Debug mode is enabled";`elsereport "Debug mode is disabled";`endif```在上面的代码中,如果DEBUG宏被定义了,那么report语句"Debug mode is enabled"将被编译进去;否则将编译进去"Debug mode is disabled"。

除了`ifdef语句外,VHDL还提供了一些其他的条件编译指令,如`ifndef(如果给定条件为假则编译)、`elsif(如果前面的条件为假则继续判断下一个条件)、`elsif和`endif。

一、数据类型A. 标准数据类型1)整数类型(INTEGER)VARIBLE A:INTEGER RANGE -128 TO 128范围-(231-1)~ +(231-1)2#11111111# --binary,=255D8#377#16#FF#2)实数类型和浮点类型(REAL & FLOATING)实数范围-1.0E+38 ~ +1.0E+38大多数EDA工具不支持浮点类型16#0F#E+016#FF.FF#E-13)位类型(BIT)TYPE BITIS(‘0',‘1')4)位矢量类型(BIT_VECTOR)位矢量(bit_vector)类型实际上就是位(bit)的一位数组,它的表示方法是用双引号将一组位数据括起来。

例如:"11010111"。

不难看出,采用位矢量可以很方便地表示电路描述中的总线状态,这在VHDL程序中经常用到。

B"1111-1100" --长度为8X"FBC" --长度为12,=B"1111-1011-1100"O"371" --长度为9,=B"011-111-001"5)布尔类型(BOOLEAN)6)字符类型(CHARACTER)‘A',‘a',‘B',大小写不敏感。

7)字符串类型(TRING)"VHDL","MULTI_SCREEN"8)物理类型(physical)--时间类型--The physics unit time is a predefined typeTYPE time IS RANGE -1E18 TO 1E18UNITSfs; -- Femto-secondps = 1000 fs;ns = 1000 ps;us = 1000 ns;ms = 1000 us;sec = 1000ms;min = 60 sec;END UNITS--another--DISTANCE TYPETYPE distance IS RANGE 0 TO 1E16UNITSA;nm = 10A;um = 1000nm;mm = 1000um;cm = 10mm;m = 1000 mm;km = 1000m;END UNITS;9)错误类型(NOTE,WARNING,ERROR,FAILURE)10)自然数、正整数类型(NATURAL & POSITIVE)ENTITY_compare ISPORT(a,b:INTEGER RANGE 0 to 9:=0;c:out Boolean);END compare;B. 自定义数据类型1)枚举类型(ENUMERATED)TYPE PCI_BUSstate IS(Idle,busbusy,write,read,Back off); --PCI总线状态机变量TYPEstd_ulogic IS('U',‘X',‘1',‘0',‘Z',‘W',‘L',‘H',‘-‘);TYPE boolean IS(false,true);TYPE BITIS(‘0',‘1');2)整数类型(INTEGER)TYPE digit IS INTEGER RANGE -128 TO 1283)实数类型和浮点类型(REAL & FLOATING)4)数组类型(ARRAY)TYPE MYARRAY IS ARRAY(INTEGER 0 TO 9)OFstd_LOGIC5)存取类型(ACCESS)TYPE line IS ACCESS string; --Line是指向字符串的指针6)文件类型(FILES)TYPE text IS FILE OF string;TYPE input-type IS FILE OF character;7)记录类型(RECODE)--RECORD适于描写总线,通讯协议TYPE PCI_BUS IS RECORDADDR:std_LOCIG_VECTOR(31 DOWNTO 0);DATA:std_LOGIC_VECTOR(31 DOWNTO 0);END RECORD;SEGINAL DECODE1,DECODE2:PCI_BUS;PCI_DEVICE1 <= DECODE1.ADDR;PCI_DEVICE1RAM <= DECODE1.DATA;8)时间类型(TIME)9)VHDLstd_logic在VHDL中,设计人员经常使用的数据类型是枚举类型std_ulogic和它的子类型std_logic,它们都是一个九值逻辑系统。

VHDL 基础语法篇——VHDLVHDL硬件描述语言1。

1 VHDL概述1。

1。

1 VHDL的特点VHDL语言作为一种标准的硬件描述语言,具有结构严谨、描述能力强的特点,由于VHDL语言来源于C、Fortran等计算机高级语言,在VHDL语言中保留了部分高级语言的原语句,如if语句、子程序和函数等,便于阅读和应用。

具体特点如下:1。

支持从系统级到门级电路的描述,既支持自底向上(bottom-up)的设计也支持从顶向下(top—down)的设计,同时也支持结构、行为和数据流三种形式的混合描述。

2. VHDL的设计单元的基本组成部分是实体(entity)和结构体(architecture),实体包含设计系统单元的输入和输出端口信息,结构体描述设计单元的组成和行为,便于各模块之间数据传送.利用单元(componet)、块(block)、过程(procure)和函数(function)等语句,用结构化层次化的描述方法,使复杂电路的设计更加简便。

采用包的概念,便于标准设计文档资料的保存和广泛使用。

3. VHDL语言有常数、信号和变量三种数据对象,每一个数据对象都要指定数据类型,VHDL的数据类型丰富,有数值数据类型和逻辑数据类型,有位型和位向量型。

既支持预定义的数据类型,又支持自定义的数据类型,其定义的数据类型具有明确的物理意义,VHDL是强类型语言。

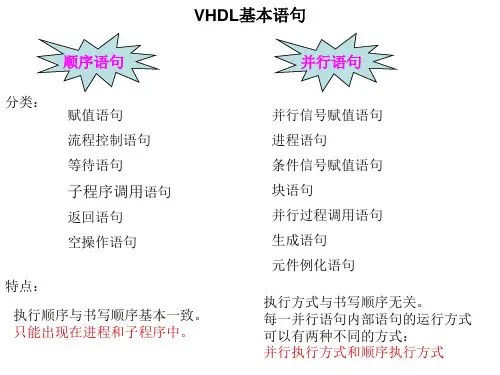

4. 数字系统有组合电路和时序电路,时序电路又分为同步和异步,电路的动作行为有并行和串行动作,VHDL语言常用语句分为并行语句和顺序语句,完全能够描述复杂的电路结构和行为状态。

1.1.2 VHDL语言的基本结构VHDL语言是数字电路的硬件描述语言,在语句结构上吸取了Fortran和C等计算机高级语言的语句,如IF语句、循环语句、函数和子程序等,只要具备高级语言的编程技能和数字逻辑电路的设计基础,就可以在较短的时间内学会VHDL语言。

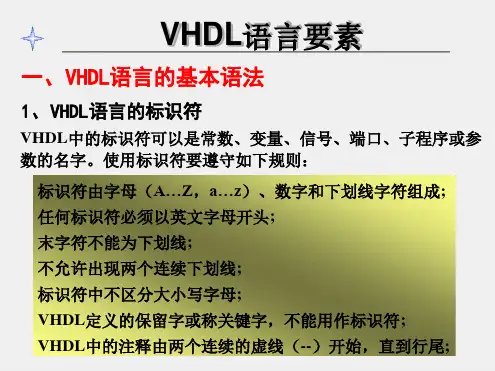

但是VHDL毕竟是一种描述数字电路的工业标准语言,该种语言的标识符号、数据类型、数据对象以及描述各种电路的语句形式和程序结构等方面具有特殊的规定,如果一开始就介绍它的语法规定,会使初学者感到枯燥无味,不得要领.较好的办法是选取几个具有代表性的VHDL程序实例,先介绍整体的程序结构,再逐步介绍程序中的语法概念。