《VHDL的基本语法》

- 格式:ppt

- 大小:703.00 KB

- 文档页数:16

VHDL语法(yǔfǎ)简单总结VHDL语法简单(jiǎndān)总结VHDL语法(yǔfǎ)简单总结一个(yī ɡè)VHDL程序代码包含实体(shítǐ)(entity)、结构(jiégòu)体(architecture)、配置(pèizhì)(configuration)、程序包(package)、库(library)等。

一、数据类型1.用户自定义数据类型使用关键字TYPE,例如:TYPE my_integer IS RANGE -32 TO 32;–用户自定义的整数类型的子集TYPE student_grade IS RANGE 0 TO 100;–用户自定义的自然数类型的子集TYPE state IS (idle, forward, backward, stop);–枚举数据类型,常用于有限状态机的状态定义一般来说,枚举类型的数据自动按顺序依次编码。

2.子类型在原有已定义数据类型(lèixíng)上加一些约束条件,可以定义(dìngyì)该数据类型的子类型。

VHDL不允许不同类型的数据直接进行操作运算,而某个数据类型的子类型则可以和原有类型数据直接进行操作运算。

子类型定义使用(shǐyòng)SUBTYPE关键字。

3.数组(ARRAY)ARRAY是将相同数据类型的数据集合在一起(yīqǐ)形成的一种新的数据类型。

TYPE type_name IS ARRAY (specification) OF data_type;–定义新的数组类型(lèixíng)语法结构SIGNAL signal_name: type_name [:=initial_value];–使用新的数组类型对SIGNAL,CONSTANT, VARIABLE进行声明例如:TYPE delay_lines IS ARRAY (L-2 DOWNTO 0) OF SIGNED (W_IN-1 DOWNTO 0);–滤波器输入延迟链类型定义TYPE coeffs IS ARRAY (L-1 DOWNTO 0) OF SIGNED (W_COEF-1 DOWNTO 0);–滤波器系数(xìshù)类型定义SIGNAL delay_regs: delay_lines; –信号延迟(yánchí)寄存器声明CONSTANT coef: coeffs := ( ); –常量(chángliàng)系数声明并赋初值4.端口数组在定义电路的输入/输出端口时,有时需把端口定义为矢量阵列,而在ENTITY中不允许使用TYPE进行类型定义,所以(suǒyǐ)必须在包集(PACKAGE)中根据端口的具体信号特征建立用户自定义的数据类型,该数据类型可以供包括ENTITY在内的整个设计使用。

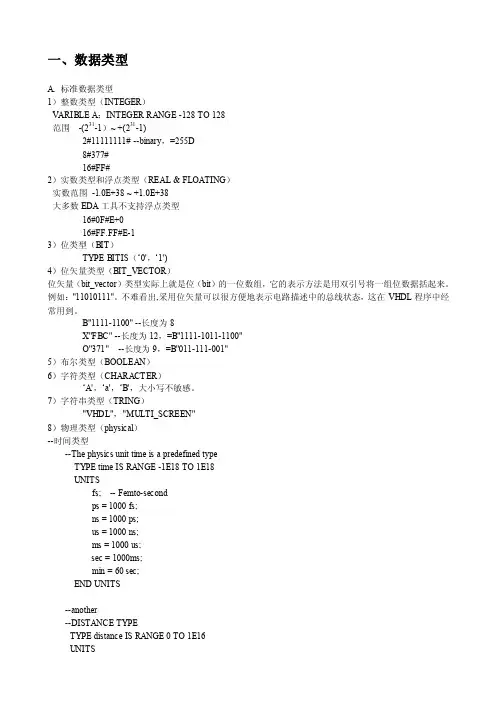

一、数据类型A. 标准数据类型1)整数类型(INTEGER)VARIBLE A:INTEGER RANGE -128 TO 128范围-(231-1)~ +(231-1)2#11111111# --binary,=255D8#377#16#FF#2)实数类型和浮点类型(REAL & FLOATING)实数范围-1.0E+38 ~ +1.0E+38大多数EDA工具不支持浮点类型16#0F#E+016#FF.FF#E-13)位类型(BIT)TYPE BITIS(‘0',‘1')4)位矢量类型(BIT_VECTOR)位矢量(bit_vector)类型实际上就是位(bit)的一位数组,它的表示方法是用双引号将一组位数据括起来。

例如:"11010111"。

不难看出,采用位矢量可以很方便地表示电路描述中的总线状态,这在VHDL程序中经常用到。

B"1111-1100" --长度为8X"FBC" --长度为12,=B"1111-1011-1100"O"371" --长度为9,=B"011-111-001"5)布尔类型(BOOLEAN)6)字符类型(CHARACTER)‘A',‘a',‘B',大小写不敏感。

7)字符串类型(TRING)"VHDL","MULTI_SCREEN"8)物理类型(physical)--时间类型--The physics unit time is a predefined typeTYPE time IS RANGE -1E18 TO 1E18UNITSfs; -- Femto-secondps = 1000 fs;ns = 1000 ps;us = 1000 ns;ms = 1000 us;sec = 1000ms;min = 60 sec;END UNITS--another--DISTANCE TYPETYPE distance IS RANGE 0 TO 1E16UNITSA;nm = 10A;um = 1000nm;mm = 1000um;cm = 10mm;m = 1000 mm;km = 1000m;END UNITS;9)错误类型(NOTE,WARNING,ERROR,FAILURE)10)自然数、正整数类型(NATURAL & POSITIVE)ENTITY_compare ISPORT(a,b:INTEGER RANGE 0 to 9:=0;c:out Boolean);END compare;B. 自定义数据类型1)枚举类型(ENUMERATED)TYPE PCI_BUSstate IS(Idle,busbusy,write,read,Back off); --PCI总线状态机变量TYPEstd_ulogic IS('U',‘X',‘1',‘0',‘Z',‘W',‘L',‘H',‘-‘);TYPE boolean IS(false,true);TYPE BITIS(‘0',‘1');2)整数类型(INTEGER)TYPE digit IS INTEGER RANGE -128 TO 1283)实数类型和浮点类型(REAL & FLOATING)4)数组类型(ARRAY)TYPE MYARRAY IS ARRAY(INTEGER 0 TO 9)OFstd_LOGIC5)存取类型(ACCESS)TYPE line IS ACCESS string; --Line是指向字符串的指针6)文件类型(FILES)TYPE text IS FILE OF string;TYPE input-type IS FILE OF character;7)记录类型(RECODE)--RECORD适于描写总线,通讯协议TYPE PCI_BUS IS RECORDADDR:std_LOCIG_VECTOR(31 DOWNTO 0);DATA:std_LOGIC_VECTOR(31 DOWNTO 0);END RECORD;SEGINAL DECODE1,DECODE2:PCI_BUS;PCI_DEVICE1 <= DECODE1.ADDR;PCI_DEVICE1RAM <= DECODE1.DATA;8)时间类型(TIME)9)VHDLstd_logic在VHDL中,设计人员经常使用的数据类型是枚举类型std_ulogic和它的子类型std_logic,它们都是一个九值逻辑系统。

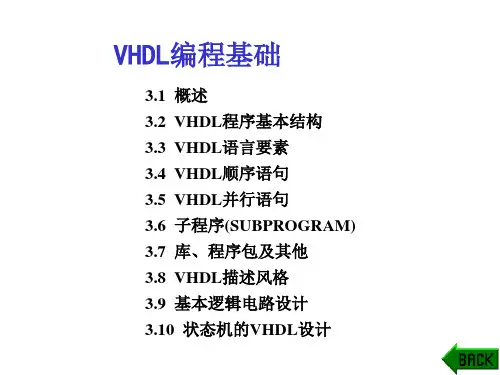

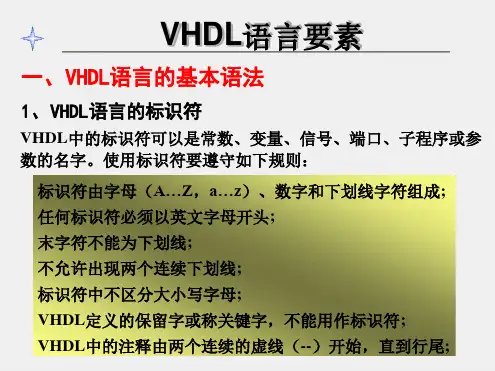

vhdl基本语法(简略共34页)vhdl基本语法(简略共34页)VHDL硬件描述语言1.1 VHDL概述1.1.1 VHDL的特点VHDL语言作为一种标准的硬件描述语言,具有结构严谨、描述能力强的特点,由于VHDL语言来源于C、Fortran等计算机高级语言,在VHDL语言中保留了部分高级语言的原语句,如if语句、子程序和函数等,便于阅读和应用。

具体特点如下:1. 支持从系统级到门级电路的描述,既支持自底向上(bottom-up)的设计也支持从顶向下(top-down)的设计,同时也支持结构、行为和数据流三种形式的混合描述。

2. VHDL的设计单元的基本组成部分是实体(entity)和结构体(architecture),实体包含设计系统单元的输入和输出端口信息,结构体描述设计单元的组成和行为,便于各模块之间数据传送。

利用单元(componet)、块(block)、过程(procure)和函数(function)等语句,用结构化层次化的描述方法,使复杂电路的设计更加简便。

采用包的概念,便于标准设计文档资料的保存和广泛使用。

3. VHDL语言有常数、信号和变量三种数据对象,每一个数据对象都要指定数据类型,VHDL的数据类型丰富,有数值数据类型和逻辑数据类型,有位型和位向量型。

既支持预定义的数据类型,又支持自定义的数据类型,其定义的数据类型具有明确的物理意义,VHDL是强类型语言。

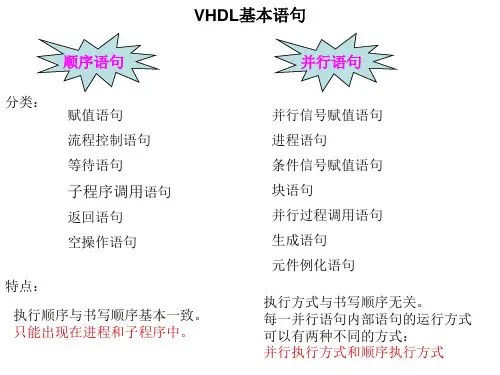

4. 数字系统有组合电路和时序电路,时序电路又分为同步和异步,电路的动作行为有并行和串行动作,VHDL语言常用语句分为并行语句和顺序语句,完全能够描述复杂的电路结构和行为状态。

1.1.2 VHDL语言的基本结构VHDL语言是数字电路的硬件描述语言,在语句结构上吸取了Fortran和C等计算机高级语言的语句,如IF语句、循环语句、函数和子程序等,只要具备高级语言的编程技能和数字逻辑电路的设计基础,就可以在较短的时间内学会VHDL语言。