vhdl条件赋值语句

- 格式:docx

- 大小:3.64 KB

- 文档页数:7

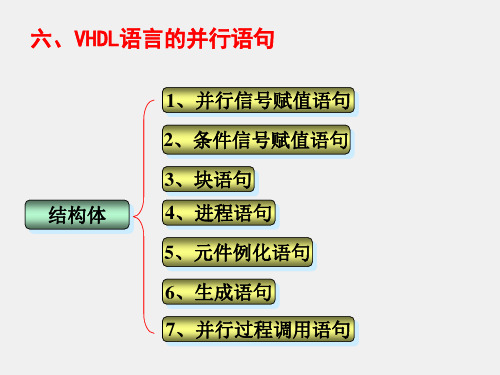

VHDL的顺序语句和并行语句一、顺序语句顺序语句只能出现在进程(PROCESS)、子程序(过程(PROCEDURE)和函数(FUNCTION))中,其特点与传统的计算机编程语句类似,是按程序书写的顺序自上而下、一条一条地执行。

利用顺序语句可以描述数字逻辑系统中的组合逻辑电路和时序逻辑电路。

VHDL的顺序语句有赋值语句、流程控制语句、等待语句、子程序调用语句、返回语句、空操作语句等六类。

<1>赋值语句赋值语句的功能是将一个值或一个表达式的运算结果传递给某一个数据对象。

(1)变量赋值语句格式:目标变量名:=赋值源(表达式);例如:x:=5.0;(2)信号赋值语句格式:目标信号名<=赋值源;例如:y<=…1‟;说明:该语句若出现在进程或子程序中则是顺序语句,若出现在结构体中则是并行语句。

( 3 )数组元素赋值例如:SIGNAL a,b:STD LOGIC VECTOR(1 TO 4);a<=“1101”;a(1 TO 2)<=“10”;a(1 TO 2)<=b(2 TO 3);<2>流程控制语句通过条件控制开关决定是否执行一条或几条语句,或重复执行一条或几条语句,或跳过一条或几条语句。

流程控制语句共有5种:IF语句CASE语句LOOP语句NEXT语句EXIT语句(1)IF语句1、IF 条件句Then 顺序语句END IF ;2、IF 条件句Then 顺序语句ELSE 顺序语句END IF ;3、IF 条件句Then 顺序语句ELSIF 条件句Then 顺序语句...ELSE 顺序语句END IF4、IF 条件句ThenIF 条件句Then...END IFEND IF例子:8线-3线优先编码器的设计LIBRARY IEEE;USE IEEE.STD LOGIC 1164.ALLENTITY coder ISPORT(a:IN STD LOGIC VECTOR(0 TO 7);y:OUT STD LOGIC VECTOR(0 TO 2));END coder;ARCHITECTURE example2 OF coder ISBEGINPROCESS(a)BEGINIF (a(7)=…0‟)THEN y<=”111”;ELSIF (a(6)=‟0‟) THEN y<=”011”;ELSIF (a(5)=‟0‟) THEN y<=”101”;ELSIF (a(4)=‟0‟) THEN y<=”001”;ELSIF (a(3)=‟0‟) THEN y<=”110”;ELSIF (a(2)=‟0‟) THEN y<=”010”;ELSIF (a(1)=‟0‟) THEN y<=”100”;ELSE y<=”000”;END IF;END PROCESS;END example2;(2)CASE语句格式:CASE 表达式ISWhen 选择值=>顺序语句;When 选择值=>顺序语句;…When OTHERS =>顺序语句;END CASE;说明:“=>”不是运算符,相当“THEN”。

vhdl语句

VHDL是一种硬件描述语言,用于描述数字电路和系统的行为和结构。

以下是VHDL中的一些基本语句:

1.实体(Entity):用于声明一个电路或系统的接口,包括输入、输

出和输入/输出端口。

2.结构体(Architecture):用于描述电路或系统的实现,包括元件的

连接和行为描述。

3.信号赋值语句:用于在进程中给信号赋值,例如“a <= b;”。

4.条件赋值语句:用于根据条件给信号赋值,例如“IF condition THEN

a <=

b ELSE a <=

c END IF;”。

5.选择信号赋值语句:用于根据选择信号的值给信号赋值,例如

“SELECT CASE a WHEN value1 THEN b WHEN value2 THEN c WHEN OTHERS THEN d END CASE;”。

6.进程语句:用于描述电路或系统的行为,包括顺序执行和并行执

行。

7.元件例化语句:用于实例化一个元件,并将其连接到其他元件上。

8.生成语句:用于生成多个相同类型的元件实例。

9.子程序调用语句:用于调用一个子程序。

10.顺序语句:在仿真意义上具有一定顺序性,并不意味着这些语句

对于的硬件结构也有相同的顺序性。

所有门电路是并行地工作,并没有先后之分。

11.并行语句:在仿真运行中总处于两种状态:执行或者挂起。

当执

行到wait语句时,运行程序将被挂起,直到满足此语句设置的结束挂起条件后,将重新开始执行进程中的程序。

以上只是VHDL中的一些基本语句,实际上VHDL还支持更多的高级功能和描述方式。

vhdl条件赋值语句

vhdl是一种硬件描述语言,用于描述硬件电路的行为和结构。

在vhdl中,条件赋值语句是一种常用的语法结构,用于根据特定条件给变量赋值。

下面列举了10个关于vhdl条件赋值语句的例子。

1. 当输入信号X为1时,将输出信号Y赋值为0;否则将Y赋值为1。

```vhdl

process (X)

begin

if X = '1' then

Y <= '0';

else

Y <= '1';

end if;

end process;

```

2. 当输入信号A为0时,将输出信号B赋值为C的值;否则将B赋值为D的值。

```vhdl

process (A, C, D)

begin

if A = '0' then

B <= C;

else

B <= D;

end if;

end process;

```

3. 根据输入信号Sel的值,选择对应的输入信号并赋值给输出信号Out。

```vhdl

process (Sel, In1, In2, In3)

begin

case Sel is

when "00" =>

Out <= In1;

when "01" =>

Out <= In2;

when "10" =>

Out <= In3;

when others =>

Out <= "0000";

end case;

end process;

```

4. 如果输入信号X大于等于Y,则将输出信号Z赋值为1;否则将Z赋值为0。

```vhdl

process (X, Y)

begin

if X >= Y then

Z <= '1';

else

Z <= '0';

end if;

end process;

```

5. 当输入信号Valid为1且输入信号Data的值为偶数时,将输出信号Even赋值为1;否则将Even赋值为0。

```vhdl

process (Valid, Data)

begin

if Valid = '1' and Data mod 2 = 0 then

Even <= '1';

Even <= '0';

end if;

end process;

```

6. 当输入信号X为1时,将输出信号Y赋值为X的平方;否则将Y 赋值为X的立方。

```vhdl

process (X)

begin

if X = '1' then

Y <= X * X;

else

Y <= X * X * X;

end if;

end process;

```

7. 如果输入信号A等于B且C等于D,则将输出信号X赋值为1;否则将X赋值为0。

```vhdl

process (A, B, C, D)

if A = B and C = D then

X <= '1';

else

X <= '0';

end if;

end process;

```

8. 根据输入信号Sel的值,选择对应的输入信号的最大值并赋值给输出信号Max。

```vhdl

process (Sel, In1, In2, In3)

begin

case Sel is

when "00" =>

Max <= In1;

when "01" =>

Max <= In2;

when "10" =>

Max <= In3;

when others =>

Max <= '0';

end case;

end process;

```

9. 当输入信号A为0时,将输出信号B赋值为1;当A为1时,将B赋值为2;否则将B赋值为3。

```vhdl

process (A)

begin

case A is

when '0' =>

B <= '1';

when '1' =>

B <= '2';

when others =>

B <= '3';

end case;

end process;

```

10. 根据输入信号Sel的值,选择对应的输入信号并将其左移一位后赋值给输出信号Out。

```vhdl

process (Sel, In1, In2, In3)

begin

case Sel is

when "00" =>

Out <= In1 sll 1;

when "01" =>

Out <= In2 sll 1;

when "10" =>

Out <= In3 sll 1;

when others =>

Out <= '0';

end case;

end process;

```

以上是10个关于vhdl条件赋值语句的例子,每个例子都展示了不同的条件判断和赋值方式。

通过合理使用条件赋值语句,可以实现复杂的电路行为描述,提高硬件设计的灵活性和可重用性。