小型数字系统设计完整版

- 格式:ppt

- 大小:519.50 KB

- 文档页数:13

南通大学计算机科学与技术学院操作系统课程设计报告专业:计嵌151学生姓名:王志宏学号:1513052018时间:2017/6/28设计一个小型的操作系统设计要求将本学期三次的实验集成实现: 1.中断处理 2.作业调度 3.PV 原语 4.死锁 5.页面替换 6.磁盘调度(一)设计流程图主流程图开始的图形界面中断处理 死锁磁盘调度先来先服务先来先服作业调度页面替换 L R U 算银行家算时钟 先进先出PV 原语 哲学家吃通1.中断处理模拟时钟中断的产生及设计一个对时钟中断事件进行处理的模拟程序。

计算机系统工作过程中,若出现中断事件,硬件就把它记录在中断寄存器中。

中断寄存器的每一位可与一个中断事件对应,当出现某中断事件后,对应的中断寄存器的某一位就被置成―1‖。

处理器每执行一条指令后,必须查中断寄存器,当中断寄存器内容不为―0‖时,说明有中断事件发生。

硬件把中断寄存器内容以及现行程序的断点存在主存的固定单元,且让操作系统的中断处理程序占用处理器来处理出现的中断事件。

操作系统分析保存在主存固定单元中的中断寄存器内容就可知道出现的中断事件的性质,从而作出相应的处理。

本实习中,用从键盘读入信息来模拟中断寄存器的作用,用计数器加 1 来模拟处理器执行了一条指令。

每模拟一条指令执行后,从键盘读入信息且分析,当读入信息=0 时,表示无中断事件发生,继续执行指令;当读入信息=1 时,表示发生了时钟中断事件,转时钟中断处理程序2.作业调度1)先来先服务FCFSN 开始初始化进程控制块,让进程控制块按进程到达先后顺序让进程排队调度数组中首个进程,并让数组中的下一位移到首位计算并打印进程的完成时刻、周转时间、带权周转时间其中:周转时间= 完成时间- 到达时间带权周转时间=周转时间/服务时间更改计时器的当前时间,即下一刻进程的开始时间当前时间=前一进程的完成时间+其服务时间数组为空Y先来先服务算法流程3.PV原语1)哲学家吃通心面问题哲学家吃通心面:在这道题目里,每把叉子必须互斥使用,当一位哲学家吃通心面之前必须执行两个P操作,获得自己左右两边的叉子,在吃完通心面后必须执行两个V操作,放下叉子。

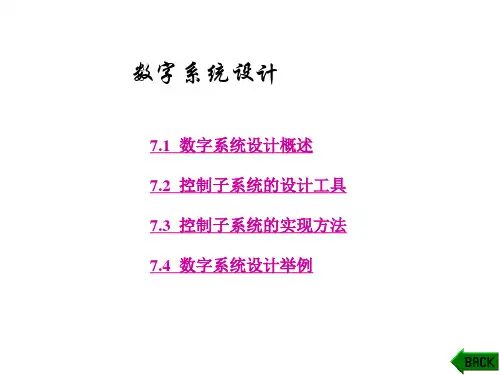

数字系统设计课程设计一、课程目标知识目标:1. 理解数字系统设计的基本原理和概念,包括数字逻辑、组合逻辑和时序逻辑;2. 掌握数字电路的基本组成元素,如逻辑门、触发器、计数器等;3. 学会使用硬件描述语言(如Verilog、VHDL)进行数字系统的设计和描述;4. 了解数字系统的测试和验证方法。

技能目标:1. 能够运用所学知识,设计简单的数字系统,如加法器、寄存器、状态机等;2. 能够使用硬件描述语言编写代码,实现数字系统的功能;3. 能够对设计的数字系统进行功能仿真和时序分析;4. 能够运用调试工具和仪器对数字系统进行测试和调试。

情感态度价值观目标:1. 培养学生的团队合作意识和沟通能力,学会与他人共同解决问题;2. 培养学生的创新意识和实践能力,敢于尝试新方法,善于发现和解决问题;3. 增强学生的工程素养,使其认识到数字系统设计在实际应用中的重要性;4. 培养学生严谨、细致的学习态度,注重细节,追求高质量的设计成果。

本课程针对高年级学生,课程性质为理论与实践相结合。

通过本课程的学习,使学生能够掌握数字系统设计的基本方法和技能,培养其创新意识和工程实践能力。

在教学过程中,注重学生的主体地位,鼓励学生积极参与讨论和实践,提高其分析问题和解决问题的能力。

课程目标的设定旨在使学生在知识、技能和情感态度价值观方面取得具体的学习成果,为后续相关课程的学习和实际工程应用打下坚实基础。

二、教学内容1. 数字系统设计基础- 数字逻辑与数字电路基本概念- 常用逻辑门电路及其功能- 数字电路的布尔代数与逻辑化简2. 组合逻辑设计- 组合逻辑电路的分析与设计方法- 常用组合逻辑电路(如编码器、译码器、多路选择器等)- 竞争与冒险现象及其解决方法3. 时序逻辑设计- 时序逻辑电路的特点与基本组成- 触发器类型及其功能- 同步与异步时序电路的设计方法4. 硬件描述语言- Verilog/VHDL基本语法与结构- 数字系统设计实例及代码编写- 仿真与调试方法5. 数字系统测试与验证- 功能仿真与时序分析- 数字系统的测试方法与测试向量生成- FPGA器件及实验板使用6. 数字系统设计实践- 设计简单的数字系统(如加法器、寄存器等)- 项目实践与团队协作- 设计报告撰写与成果展示教学内容按照教学大纲的安排,从基础理论到实践应用,循序渐进地展开。

课程设计报告课程设计名称:数据库原理与应用系部:二系学生姓名:班级:学号:成绩:指导教师:一.设计题目:小型办公系统二.主要内容:➢用户凭帐号密码登入系统,有4类用户:普通员工、部门经理、总经理、系统管理员➢系统管理员可以查看、增加、删除前3类用户,即普通员工、部门经理和总经理,并可修改其密码;可以查看、增加、删除部门信息,可以指定或更改部门经理,可以为每位员工分配部门。

➢所有用户均可以查看所有员工(包括部门经理、总经理、管理员等)的通信录;均可以改变自己的通信方式和登陆密码。

➢总经理可以为所有普通员工、部门经理群发短消息,可以为指定人员发短消息和布置工作任务。

➢部门经理可以为本部门的所有员工群发短消息,可以为本部门指定人员发短消息和分配工作任务;可以查看是否有自己的短消息,可以看到系统提示当前日期(今天)有无工作任务。

➢普通员工可以查看是否有自己的短消息,可以看到系统提示当前日期(今天)有无工作任务,是谁布置的以及具体工作内容要求。

三.具体要求1.课程设计的内容独立自主完成,课程设计报告内容完整、格式规范、排版整洁美观;2.后台数据库采用MS SQL SERVER2005,前台界面语言不限,编写的程序代码,须有较详细的注释说明;四.进度安排课程设计安排:16周星期一讲解课程设计的内容,安排每一天的具体任务,分配并熟悉题目;星期二需求分析:给出系统的功能需求、性能需求,并绘制DFD和DD;星期三概念结构设计:绘制实体属性图(可选),局部ER图和全局ER图;星期四逻辑结构设计:转换、优化、外模式的设计;星期五物理结构设计及数据库实施;17周星期一应用程序编制调试、整理课程设计报告,并检查;星期二根据反馈结果修改课程设计;星期三提交作业上交的材料:课程设计的电子稿、打印稿、源码(SQL代码和程序代码)五.成绩评定考核方法:现场验收(占50%),课程设计报告(占50%)。

考核内容:学习态度(出勤情况,平时表现等)、方案合理性、各阶段的图表与程序编制质量、设计报告质量。

操作系统课程设计报告题目:一个小型的操作系统班级:计122(杏)学号:1213023075姓名:贾苏日期:2014/06/231.实验平台(1)软件平台:开发系统平台:Windows 7 (64)Microsoft visual c++ 6.0测试系统平台:Windows 7 (64)(2)硬件平台:cpu:AMD A6-3420 APU内存:4GB硬盘:500G2.所需实现的功能及相应的阐述:(1)进程调度管理为了贴切现实中的os,采用RR(轮转调度算法),且不提供用户显式的选择调度算法,即对用户是透明的。

现实中的处理器主频为1Ghz~3Ghz,选取中间点为1.5Ghz,得时间片大小为0。

7ns ,为方便计算*10,则时间片大小定为7ns.假设进程之间的调度和切换不耗费cpu时间。

(2)死锁的检测与处理检测当然采用的是银行家算法处理:让用户选择kill一个进程,释放他所占有的所有资源。

(3)虚拟分页调度管理虚拟分页:给出的是逻辑值访问磁盘将那个数据块放入到内存中内存中的地址采用一定的算法相对应于磁盘的地址。

特规定访存采用的是按字节寻址内存的大小128KB外存的大小1MB即整个系统可以提供1MB的逻辑地址空间供进程进行访问(在地址总线足够扫描内存的情况下)。

虚拟地址映射采用:直接映射法规定的8kB为一个页面,故内存有16个页面,外存有128个页面。

如果产生了内存已满,便会产生缺页中断,淘汰采用FIFO算法,利用一个队列来做.(4)I/O中断处理设中断来自两个方面:1.DMA输送开始和结束时的中断设定一个宏定义为DMA一次传输的数据量的大小->DmaNum假定为10kb每次DMA开始:耗费1ns cpu时间进行中断处理DMA结束:耗费2ns cpu时间进行中断处理由操作系统课程知,DMA传输数据时不需要CPU的干预。

2.随机的中断发生外部随机中断,cpu无条件的立即响应,并执行中断处理程序,同样的假设中断处理程序的调度和切换不耗费cpu时间。

小型数字系统设计(1)实施方案(计算机11)1 CDIO二级项目“小型数字系统设计(1)(2)”实施方案(计算机2011级)计算机科学与技术系2013.11.21小型数字系统设计实施方案一、设计目的与要求小型数字系统设计(1)作为CDIO三级项目的实施是计算机科学与技术专业集中实践性环节之一,是学习完“数字逻辑”“单片机原理及应用”“汇编语言”“计算机组成原理”等课程后进行的一次全面的综合性实践课程。

总的目标要求是:(1)完成一具体的嵌入式计算机应用系统(产品)设计(包括硬件设计和软件设计)并实现其基本功能要求;(2)提交完整的设计报告(含电子版)并答辩通过;(3)调试并完成硬件产品,实现功能。

硬件课程设计其目的在于进一步加深对基础理论和基本知识的理解,掌握相关软硬件应用系统设计开发的基本方法,提高解决实际问题和创新实践的能力。

同时,进一步拓展学生在生产工艺及工程设计方面的实际知识。

针对计算机科学与技术专业学生特点和本届学生实际情况,实施中具体要求学生关注意了解熟悉掌握以下几个方面的知识点:(1)根据需求确定整体软硬件实现方案的能力;(2)应用虚拟仿真工具(如Proteus)进行硬件电路设计及数字系统仿真及元器件选型、采购等方面的知识;(3)熟练使用硬件电路调试常用仪器仪表及工具;(4)根据硬件原理进行软件驱动编程及软硬件联调方面的综合训练;(5)通过实际编程,加深对软件算法在系统中的核心地位的认识,明确以后努力方向;(6)其它方面的工程训练,如温度传感器的类型、价格,几层板、工艺、工具等。

二、设计选题要求课程设计选题分学生自选和指定题目两种:(1)自选题目:要求提前报名并提交简单的开题报告,经统一审核。

按先后顺序,先报先批。

原则上不允许出现相同题目。

接近的题目,要求功能设计和硬件或软件设计上均应有所不同。

(2)指定题目:由指导教师另行发布题目清单按要求进行分组选题三、设计步骤1根据选题,分析系统功能需求,确定系统软硬件实现方案;2查找资料准备阶段:可通过上网、图书馆、实验室查找各种图书、杂志、产品说明书等资料,裁剪、划分软硬件,设计出硬件原理图;3按小组制作、调试系统硬件(所需元器件材料先自己选择,最后由老师确定);4根据硬件原理图和功能要求,进行软件系统设计,完成软件编程;5进行软硬件联调,最终完成设计功能;6完成课程设计说明书(编写工作从一开始就应积极准备材料)。

运动码表设计数字系统特征⏹结构复杂,组件众多☐寄存器、计数器、译码器、多路选择器、总线、运算器、触发器,逻辑门电路☐数据通路(执行部件)和控制单元⏹状态复杂,很难用状态转换表来表示⏹设计方法:模块化、层次化控制信号控制输入数据输出控制单元CLK状态信号数据输入数据通路控制输出数据通路抽象模型(寄存器传输)ACLKRegA outRegA in RegB out Func (A) BMEMA RD RCLK AR outDR in访存通路总线ABCLK A outB in总线传输组合逻辑FuncENBENRegB in A BCCLKC inA L U运算通路A outB out数字系统设计流程1.设计需求分析☐外部数据,控制输入,数据、控制、状态输出2.设计功能部件☐得到内部控制信号,状态信号3.构建数据通路☐从数据流角度连接所有功能部件4.构建控制单元☐绘制系统状态图☐构建状态转换电路☐构建输出函数电路(生成所有内部,外部控制信号,状态输出)☐构建控制单元5.系统集成联调☐从控制流角度连接控制单元和执行部件(数据通路)⏹输入:4个按钮输出:4个7段数码管☐Start:计时器归零,重新开始计时☐Stop:停止计时,显示计时数据☐Store:尝试更新系统记录,并显示系统记录☐Reset:复位,计时=00.00,系统记录=99.99#功能部件控制信号输入输出1时间计数器TM TM-En,TM-Rst CLK时间计数输出16位216位寄存器SD SD-En CLK,Din(16位)Q(16位)3数码管显示DP Din(16位)DisplayInfo(32位) 4比较器52路选择器Sel3、码表数据通路构建⏹构建功能部件输入来源表#功能部件数据输入来源备注1时间计数器TM216位寄存器SD CLK,Din(16位)99.99 或当前记录增加2路选择器SD-Sel 3数码管显示DP Din(16位)TM.Q或SD.Q增加2路选择器DP-Sel 4比较器当前计时& SD.Q NewRecord⏹有多个输入来源的增设多路选择器⏹按数据流连接数据通路4、构建控制单元⏹外部控制输入信号☐Start, Stop, Reset, Store⏹定义内部、外部控制信号、内部状态信号、状态输出☐TM-EN, TM-RST, SD-EN, SD-SEL, DP-SEL,NewRecord ⏹根据功能需求构建状态图⏹填写状态转换表Excel表⏹填写输出函数真值表Excel表⏹生成状态转换逻辑表达式⏹生成输出函数逻辑表达式⏹构建控制单元内部逻辑5、码表系统集成联调⏹按控制流连接控制单元与数据通路⏹功能测试下节课再见…。