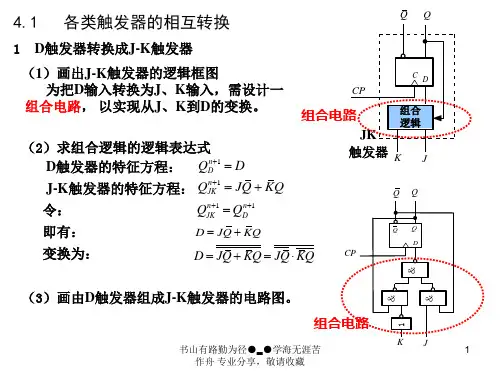

各类触发器的相互转换

- 格式:ppt

- 大小:468.50 KB

- 文档页数:16

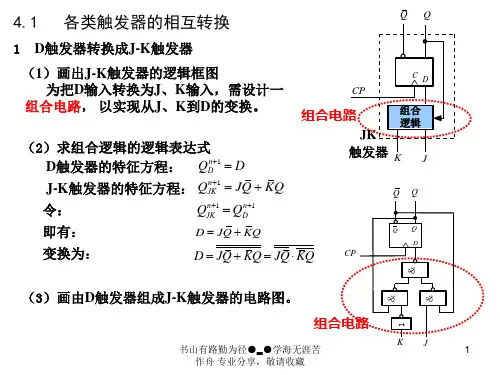

D触发器转换成T触发器真值表1. 什么是D触发器和T触发器?D触发器(D latch)和T触发器(T flip-flop)是数字电路中常用的逻辑门元件。

它们都能够保存一个比特(即二进制0或1)的状态值。

1.1 D触发器D触发器是一种具有两个输入端(D和C)和两个输出端(Q和Q’)的逻辑门。

其中,D是数据输入端,C是时钟输入端,Q是输出端,Q’是反相输出端。

D触发器有两种常见的类型:正沿触发型和负沿触发型。

正沿触发型是指当时钟信号上升沿到来时,D的值被传递到Q;负沿触发型是指当时钟信号下降沿到来时,D 的值被传递到Q。

D触发器的真值表如下:C D | Q | Q'-----------------0 0 | Q | Q'0 1 | Q | Q'1 0 | 0 | 11 1 | 1 | 01.2 T触发器T触发器是一种特殊的D触发器,它有一个输入端T(也称作切换端)用来控制状态的变化。

当T为1时,T触发器的状态将翻转;当T为0时,T触发器的状态保持不变。

T触发器的真值表如下:C T | Q | Q'-----------------0 0 | Q | Q'0 1 | Q | Q'1 0 | Q | Q'1 1 | Q' | Q2. D触发器转换成T触发器的实现方法D触发器可以通过逻辑门电路来实现T触发器的功能。

以下是两种常见的实现方法:2.1 使用与非门(NAND)可以使用两个与非门(NAND)和一个反相器(NOT)来实现D触发器转换成T触发器。

实现电路如下:C D | Q | Q'------------------0 0 | Q | Q'0 1 | Q | Q'1 0 | Q | Q'1 1 | Q' | Q2.2 使用与或非门(AND-OR-NOT)可以使用两个与非门(NAND)、一个或非门(NOR)和一个反相器(NOT)来实现D触发器转换成T触发器。

不同触发器循环整数-回复不同触发器循环整数: 从逻辑门到计算机芯片的奇妙旅程触发器是计算机中一种重要的逻辑元件,用于存储和处理二进制数据。

不同的触发器类型在电子元件的工作原理和功能上存在差异。

它们能够在电子电路中循环传送整数,为计算机的正常运行提供支持。

本文将深入探讨不同触发器的工作原理和应用,并展示它们在计算机科学中的重要性。

我们首先来介绍最简单的触发器类型——SR触发器。

SR触发器基于两个交替的输入线(S和R),可控制两个输出线(Q和Q')。

当输入S和R同时为0时,触发器的状态保持不变;当S为1,R为0时,触发器置位(Q 为1);当S为0,R为1时,触发器复位(Q为0)。

这种类型的触发器广泛应用于计算机存储器中,用于存储和传输二进制数据。

接下来是D触发器,它是SR触发器的简化版本。

D触发器只需一个输入线(D)来控制触发器的状态。

当D为1时,触发器置位;当D为0时,触发器复位。

D触发器在计算机的时序电路中扮演重要角色,用于存储并传送数据。

例如,在计算机的内存中,D触发器用于存储从处理器传来的数据。

接下来我们介绍一种非常常见的触发器类型——JK触发器。

JK触发器是一种多功能触发器,具有置位(Set)和复位(Reset)的功能。

JK触发器结构与SR触发器类似,但多了一个反馈功能。

当J和K同时为0时,触发器的状态保持不变;当J为1,K为0时,触发器置位;当J为0,K为1时,触发器复位;当J和K同时为1时,触发器反转(如果当前状态为1,则变为0;如果当前状态为0,则变为1)。

JK触发器在计算机的计数器和状态机中广泛应用。

还有一种常见的触发器类型是T触发器,它与JK触发器非常相似。

T触发器只有一个输入线(T),用于控制触发器的状态。

当T为0时,触发器保持不变;当T为1时,触发器反转(如果当前状态为1,则变为0;如果当前状态为0,则变为1)。

T触发器与JK触发器之间的关系是:当T为1时,JK触发器的J和K输入都为1,触发器将反转。

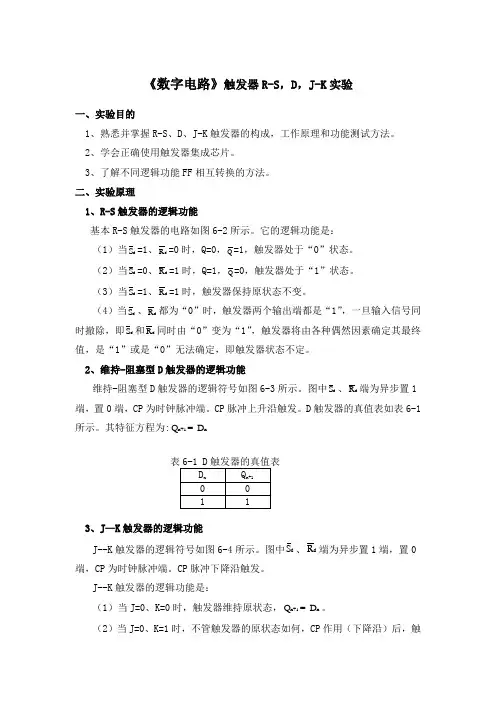

《数字电路》触发器R-S,D,J-K实验一、实验目的1、熟悉并掌握R-S、D、J-K触发器的构成,工作原理和功能测试方法。

2、学会正确使用触发器集成芯片。

3、了解不同逻辑功能FF相互转换的方法。

二、实验原理1、R-S触发器的逻辑功能基本R-S触发器的电路如图6-2所示。

它的逻辑功能是:(1)当d S=1、d R=0时,Q=0,Q=1,触发器处于“0”状态。

(2)当d S=0、d R=1时,Q=1,Q=0,触发器处于“1”状态。

(3)当d S=1、d R=1时,触发器保持原状态不变。

(4)当d S、d R都为“0”时,触发器两个输出端都是“1”,一旦输入信号同时撤除,即d S和d R同时由“0”变为“1”,触发器将由各种偶然因素确定其最终值,是“1”或是“0”无法确定,即触发器状态不定。

2、维持-阻塞型D触发器的逻辑功能维持-阻塞型D触发器的逻辑符号如图6-3所示。

图中d S、d R端为异步置1端,置0端,CP为时钟脉冲端。

CP脉冲上升沿触发。

D触发器的真值表如表6-1所示。

其特征方程为:n+1 nQ= D3、J—K触发器的逻辑功能J--K触发器的逻辑符号如图6-4所示。

图中d S、d R端为异步置1端,置0端,CP为时钟脉冲端。

CP脉冲下降沿触发。

J--K触发器的逻辑功能是:(1)当J=0、K=0时,触发器维持原状态,n+1 nQ= D。

(2)当J=0、K=1时,不管触发器的原状态如何,CP作用(下降沿)后,触发器总是处于“0”状态,n+1Q=0 。

(3)当J=1,K=0时,不管触发器原状态如何,CP作用后,触发器总是处于“1”状态,n+1Q=1(4)当J=1,K=1时,不管触发器原状态如何,CP作用后,触发器的状态都要翻转,n+1 nQ= Q。

三、实验仪器及材料1、双踪示波器2、器件(1)74LS00 二输入端四与非门 1片(2)74LS74 双D触发器 1片(3)74LS112 双J—K触发器 1片四、预习要求1、预习RS、D、JK触发器的工作原理,逻辑功能。

一、实验目的1. 理解和掌握触发器的基本原理和功能。

2. 熟悉基本RS、JK、D和T触发器的逻辑功能及其应用。

3. 学习触发器之间相互转换的方法。

4. 通过实验,加深对触发器在数字电路中的应用理解。

二、实验原理触发器是一种具有记忆功能的电子器件,它可以根据输入信号和时钟脉冲的变化,在两个稳定状态之间进行切换。

触发器在数字电路中有着广泛的应用,如计数器、寄存器、时序电路等。

触发器根据时钟脉冲的触发方式分为同步触发器和异步触发器。

同步触发器在时钟脉冲的上升沿或下降沿发生状态转换,而异步触发器则不受时钟脉冲的限制,可以在任何时刻发生状态转换。

三、实验仪器与设备1. 双踪示波器2. 数字万用表3. 数字电路实验箱4. 74LS00(二输入端四与非门)5. 74LS74(双D触发器)6. 74LS76(双J-K触发器)四、实验内容与步骤1. 基本RS触发器功能测试(1)搭建基本RS触发器电路,连接实验箱中的与非门。

(2)按照实验要求,在S、R端加信号,观察并记录触发器的Q、端状态。

(3)分析实验结果,总结RS触发器的逻辑功能。

2. JK触发器功能测试(1)搭建JK触发器电路,连接实验箱中的与非门。

(2)按照实验要求,在J、K端加信号,观察并记录触发器的Q、端状态。

(3)分析实验结果,总结JK触发器的逻辑功能。

3. D触发器功能测试(1)搭建D触发器电路,连接实验箱中的与非门。

(2)按照实验要求,在D端加信号,观察并记录触发器的Q、端状态。

(3)分析实验结果,总结D触发器的逻辑功能。

4. T触发器功能测试(1)搭建T触发器电路,连接实验箱中的与非门。

(2)按照实验要求,在T端加信号,观察并记录触发器的Q、端状态。

(3)分析实验结果,总结T触发器的逻辑功能。

5. 触发器之间相互转换(1)分析基本RS触发器与JK触发器之间的转换方法。

(2)分析基本RS触发器与D触发器之间的转换方法。

(3)分析基本RS触发器与T触发器之间的转换方法。

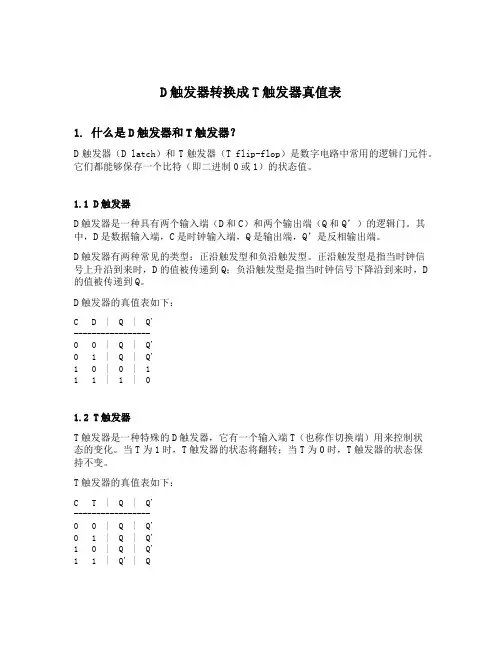

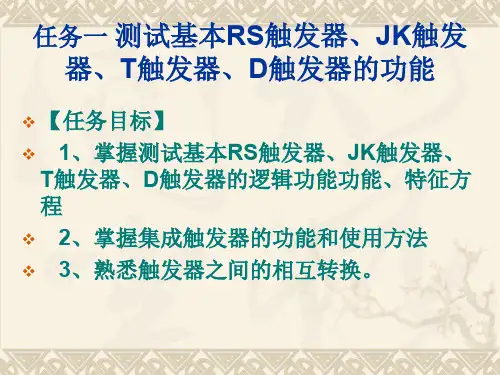

触发器的转换

触发器的转换就是通过一种触发器加上必要的逻辑电路实现另外一种触发器的功能。

触发器是时序逻辑电路的基本构成单元,按功能不同可分为 RS 触发器、 JK 触发器、 D 触发器及 T 触发器四种,其功能的描述可以使用功能真值表、激励表、状态图及特性方程。

只要增加门电路便可以实现不同功能触发器的相互转换,例如要将 D 触发器转换为 JK 触发器,转换的关键是推导出 D 触发器的输入端 D 与 JK 触发器的输入端 J 、 K 及状态输出端 Qn 的逻辑表达式,然后用门电路去实现该逻辑表达式。

具体的设计方法有公式法和图表法两种。

·公式法

公式法是不同触发器进行转换最简单与最直接的方法,其依据是描述触发器功能的特性方程,设计的过程主要是比较所使用的源触发器与要实现的目标触发器的特性方程,从而直接推导出源触发器的输入端与目标触发器的输入端及状态之间的逻辑关系。

·图表法

图表法的依据是描述触发器功能的真值表与激励表,要使用的工具是卡诺图,设计的过程是先列出要实现的目标触发器的功能真值表,该真值表反映的是在不同的输入组合及不同的现态下,目标触发器次态

的值,再根据使用的源触发器的激励表,在上述真值表中列出每一行不同状态的转变对应源触发器输入端的值,最后以此表为依据推导出源触发器的输入端与目标触发器的输入端及状态之间的逻辑关系。

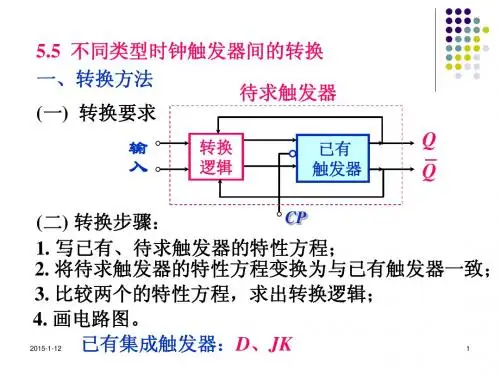

触发器规律功能转换 - 电子技术将某种规律功能的触发器经过改接或附加一些门电路后,转换为另一种触发器。

1.JK触发器转换成D触发器

一、基本结构图1 将JK触发器转换成D触发器如图1所示,在主从型JK触发器基础上,通过一“非”门是JK两端输入互为反量。

二、功能分析

当D=1,即J=1、K=0时,在C的下降沿到来后触发器翻转或保持“1”态;当D=0,即J=0、K=1时,在C的下降沿到来后触发器翻转或保持“0”态。

三、状态表

由主从型JK触发器转换而成的D触发器状态表如表1所示。

表1 D触发器规律状态表

2.JK触发器转换成T触发器

一、基本结构

图2 将JK触发器转换成T触发器

如图2所示,将J,K端连联在一起,称为T端。

二、功能分析

当T=0时,时钟脉冲作用后触发器状态不变;当T=1时,触发器具有计数功能,即。

三、状态表

由JK触发器转换而成的T触发器状态表如表2所示。

表2 T触发器规律状态表

图3 D触发器转换为T' 触发器 3. 触发器转换为T' 触发器

一、基本结构如图3,将D触发器的输出端与输入端D相联,组成T' 触发器。

二、功能分析

由于Q与是非的关系,故每来一个时钟脉冲,Q的状态必取其非,即,具有计数功能。