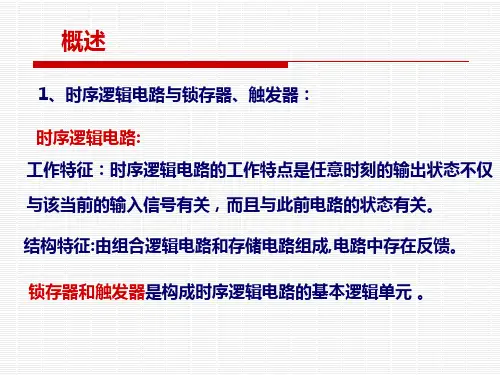

与该当前的输入信号有关,而且与此前电路的状态有关。

结构特征:由组合逻辑电路和存储电路组成,电路中存在反馈。 锁存器和触发器是构成时序逻辑电路的基本逻辑单元 。

2

4.1 概述 一、触发器的概念及特点 1.概念:

FF: (Flip-Flop, 简称FF)能够存储1位二进制信号 的基本单元电路。

2.特点: (1)有两个稳定的状态:0状态和1状态。 (2)在触发信号控制下,根据不同输入信号可置成 0或1状态。 (触发信号为时钟脉冲信号)

第4章 触发器

4.1 概述

4.2 基本SR触发器(SR锁存器)

4.3 同步触发器(电平触发)

4.4 主从触发器(脉冲触发)

4.5 边沿触发器(边沿触发) 4.6 触发器的逻辑功能及描述方法 4.7 集成触发器 4.8 触发器应用举例

作业题

【5】【6】【8】【11】

1

时序逻辑电路与锁存器、触发器: 时序逻辑电路: 工作特征:时序逻辑电路的工作特点是任意时刻的输出状态不仅

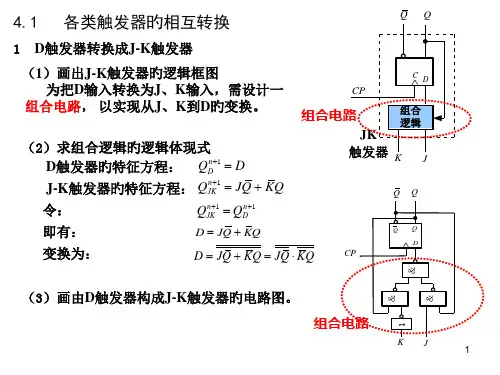

1、电路结构 以基本SRFF为基础,增加两个与非门。

置1端 时钟信号 (高电平有效) (同步控制)

置 0端 (高电平有效)

图4-5 同步SRFF

13

2、工作原理

分析CLK=0时: 有 SD’ =RD’=1, 则Q、Q’不变。 分析CLK=1时: (1)S=R=0时,有SD’ =RD’=1:Q、Q’不变(保持原态) (2)S =0, R=1:输出Q=0, Q’=1 (置0状态) (3)S =1, R=0:Q=1, Q’=0 (置1状态) (4)S=R=1:Q=Q’=1(未定义状态)

t t

1

主

O

Q

从

O

图4-13 主从JKFF波形