数字版图流程与工具1

- 格式:ppt

- 大小:2.32 MB

- 文档页数:61

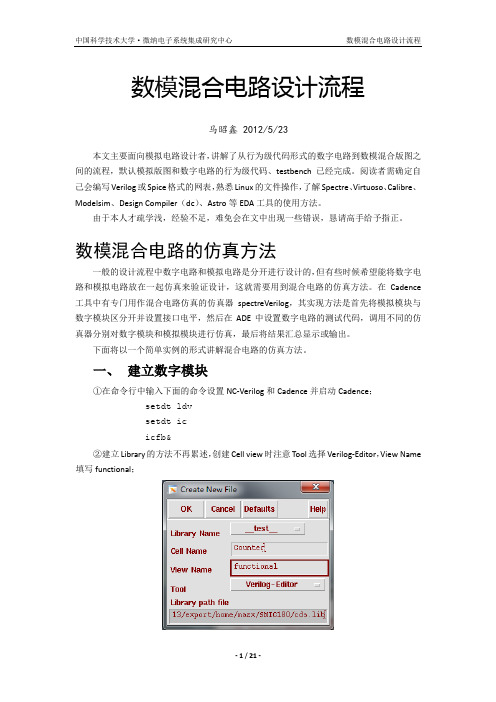

数模混合电路设计流程马昭鑫 2012/5/23本文主要面向模拟电路设计者,讲解了从行为级代码形式的数字电路到数模混合版图之间的流程,默认模拟版图和数字电路的行为级代码、testbench已经完成。

阅读者需确定自己会编写Verilog或Spice格式的网表,熟悉Linux的文件操作,了解Spectre、Virtuoso、Calibre、Modelsim、Design Compiler(dc)、Astro等EDA工具的使用方法。

由于本人才疏学浅,经验不足,难免会在文中出现一些错误,恳请高手给予指正。

数模混合电路的仿真方法一般的设计流程中数字电路和模拟电路是分开进行设计的,但有些时候希望能将数字电路和模拟电路放在一起仿真来验证设计,这就需要用到混合电路的仿真方法。

在Cadence 工具中有专门用作混合电路仿真的仿真器spectreVerilog,其实现方法是首先将模拟模块与数字模块区分开并设置接口电平,然后在ADE中设置数字电路的测试代码,调用不同的仿真器分别对数字模块和模拟模块进行仿真,最后将结果汇总显示或输出。

下面将以一个简单实例的形式讲解混合电路的仿真方法。

一、建立数字模块①在命令行中输入下面的命令设置NC-Verilog和Cadence并启动Cadence;setdt ldvsetdt icicfb&②建立Library的方法不再累述,创建Cell view时注意Tool选择Verilog-Editor,View Name 填写functional;③点击OK后会弹出有模块代码框架的vi窗口,将设计需要的代码输入或粘贴进去;④保存并关闭后如果没有错误会弹出创建Symbol View的询问对话框,确定后会进入Symbol编辑器,并自动生成了Symbol(注意在Cadence中总线用尖括号<>表示);⑤保存并关闭Symbol编辑器。

至此已经完成了数字模块的创建。

二、建立模拟模块模拟电路的创建方法无需赘述,这里搭建了一个输出频率为10MHz的环形振荡器。

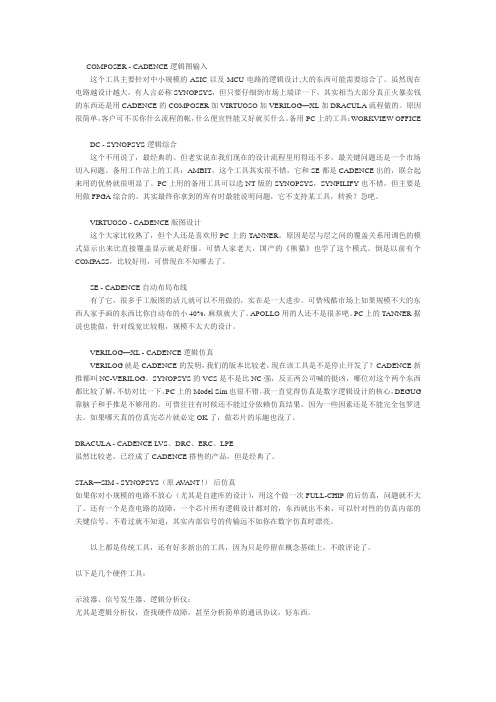

COMPOSER - CADENCE 逻辑图输入这个工具主要针对中小规模的ASIC以及MCU电路的逻辑设计,大的东西可能需要综合了。

虽然现在电路越设计越大,有人言必称SYNOPSYS,但只要仔细到市场上端详一下,其实相当大部分真正火暴卖钱的东西还是用CADENCE的COMPOSER加VIRTUOSO加VERILOG—XL加DRACULA流程做的。

原因很简单,客户可不买你什么流程的帐,什么便宜性能又好就买什么。

备用PC上的工具:WORKVIEW OFFICEDC - SYNOPSYS 逻辑综合这个不用说了,最经典的。

但老实说在我们现在的设计流程里用得还不多,最关键问题还是一个市场切入问题。

备用工作站上的工具:AMBIT,这个工具其实很不错,它和SE都是CADENCE出的,联合起来用的优势就很明显了。

PC上用的备用工具可以选NT版的SYNOPSYS,SYNPILIFY也不错,但主要是用做FPGA综合的。

其实最终你拿到的库有时最能说明问题,它不支持某工具,转换?急吧。

VIRTUOSO - CADENCE 版图设计这个大家比较熟了,但个人还是喜欢用PC上的TANNER。

原因是层与层之间的覆盖关系用调色的模式显示出来比直接覆盖显示就是舒服。

可惜人家老大,国产的《熊猫》也学了这个模式。

倒是以前有个COMPASS,比较好用,可惜现在不知哪去了。

SE - CADENCE 自动布局布线有了它,很多手工版图的活儿就可以不用做的,实在是一大进步。

可惜残酷市场上如果规模不大的东西人家手画的东西比你自动布的小40%,麻烦就大了。

APOLLO用的人还不是很多吧。

PC上的TANNER 据说也能做,针对线宽比较粗,规模不太大的设计。

VERILOG—XL - CADENCE 逻辑仿真VERILOG就是CADENCE的发明,我们的版本比较老,现在该工具是不是停止开发了?CADENCE 新推都叫NC-VERILOG。

SYNOPSYS的VCS是不是比NC强,反正两公司喊的挺凶,哪位对这个两个东西都比较了解,不妨对比一下。

集成电路(IC)设计完整流程详解及各个阶段工具简介集成电路(ic)设计完整流程及工具集成电路的设计过程可以分为两部分:前端设计(也称为逻辑设计)和后端设计(也称为物理设计)。

这两部分之间没有统一而严格的界限。

任何与流程相关的设计都可以称为后端设计。

前端设计的主要流程:1、规格制定芯片规格与功能清单一样,是客户向芯片设计公司(称为fabless,fabless design company)提出的设计要求,包括芯片需要满足的具体功能和性能要求。

2.详细设计fabless根据客户提出的规格要求,拿出设计解决方案和具体实现架构,划分模块功能。

3、hdl编码使用硬件描述语言(VHDL、Verilog HDL,工业公司普遍使用)以代码形式描述和实现模块功能,即用HDL语言描述实际硬件电路功能,形成RTL(寄存器传输级)代码。

4.模拟验证仿真验证通过,进行逻辑综合。

逻辑综合的结果就是把设计实现的hdl代码翻译成门级网表netlist。

综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到的标准。

逻辑综合需要基于特定的综合库,不同的库中,门电路基本标准单元(standardcell)的面积,时序参数是不一样的。

所静态时序分析(STA)也属于验证范畴,主要从时序方面验证电路,并检查电路是否违反设置时间和保持时间。

这是数字电路的基础知识。

当寄存器中出现这两种时序冲突时,无法正确采样和输出数据,因此基于寄存器的数字芯片的功能肯定会出现问题。

sta工具是Synopsys的黄金时间。

7.正式核查这也是验证范畴,它是从功能上(sta是时序上)对综合后的网表进行验证。

常用的就是等价性检查方法,以功能验证后的hdl设计为参考,对比综合后的网表功能,他们是否在功能上存在等价性。

这样做是为了保证在逻辑综合过程中没有改变原先hdl描述的电路功能。

形式验证工具有synopsys的formality。

前端设计的流程暂时写到这里。

版图模拟集成电路版图设计工作流程

一、设计准备阶段

1.收集设计需求和规格

2.确定版图设计工具

(1)选择合适的版图设计软件

(2)熟悉工具操作方法

二、布局设计

1.绘制整体版图布局

(1)放置主要功能模块

(2)确定连线路径和间距

2.设计外围器件布局

(1)放置电容、电阻等器件

(2)保证布局紧凑和良好连接

三、器件布线

1.连接器件引脚

(1)确定引脚连接顺序

(2)绘制连线路径

2.优化布线

(1)考虑信号传输和功耗(2)调整布线路径提高性能

四、特殊器件设计

1.设计特殊功能模块

(1)绘制模拟电路部分(2)完成数字逻辑设计

2.验证特殊器件功能

(1)模拟仿真验证

(2)数字仿真测试

五、验证与调试

1.进行版图验证

(1)检查器件连接和间距(2)确保布局符合设计规范2.仿真验证

(1)电气仿真测试

(2)时序分析和功耗测试

六、提交版图

1.准备版图文件

(1)导出版图文件格式

(2)打包必要设计文件2.提交给布局工程师(1)交流设计细节和要求(2)确认后提交版图。