锁相与频率合成

- 格式:ppt

- 大小:2.78 MB

- 文档页数:19

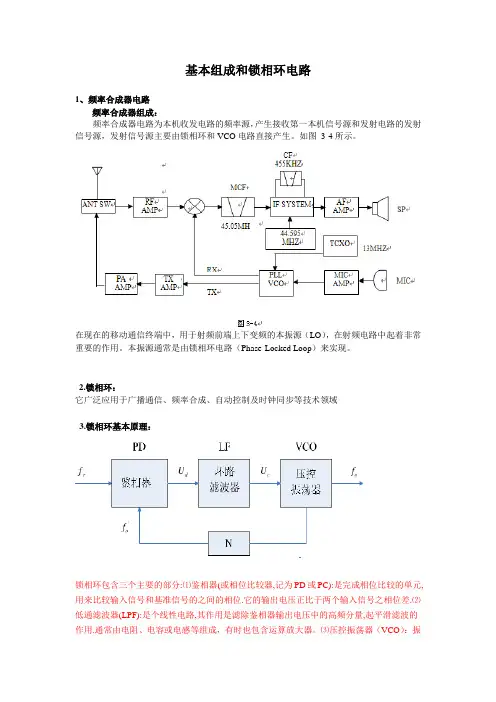

基本组成和锁相环电路1、频率合成器电路频率合成器组成:频率合成器电路为本机收发电路的频率源,产生接收第一本机信号源和发射电路的发射信号源,发射信号源主要由锁相环和VCO电路直接产生。

如图3-4所示。

在现在的移动通信终端中,用于射频前端上下变频的本振源(LO),在射频电路中起着非常重要的作用。

本振源通常是由锁相环电路(Phase-Locked Loop)来实现。

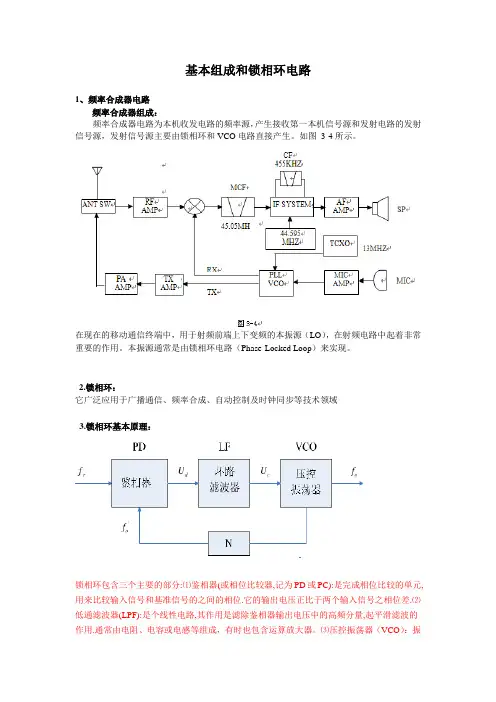

2.锁相环:它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域3.锁相环基本原理:锁相环包含三个主要的部分:⑴鉴相器(或相位比较器,记为PD或PC):是完成相位比较的单元,用来比较输入信号和基准信号的之间的相位.它的输出电压正比于两个输入信号之相位差.⑵低通滤波器(LPF):是个线性电路,其作用是滤除鉴相器输出电压中的高频分量,起平滑滤波的作用.通常由电阻、电容或电感等组成,有时也包含运算放大器。

⑶压控振荡器(VCO):振荡频率受控制电压控制的振荡器,而振荡频率与控制电压之间成线性关系。

在PLL中,压控振荡器实际上是把控制电压转换为相位。

1、压控振荡器的输出经过采集并分频;2、和基准信号同时输入鉴相器;3、鉴相器通过比较上述两个信号的频率差,然后输出一个直流脉冲电压;4、控制VCO,使它的频率改变;5、这样经过一个很短的时间,VCO 的输出就会稳定于某一期望值。

锁相环电路是一种相位负反馈系统。

一个完整的锁相环电路是由晶振、鉴相器、R分频器、N分频器、压控振荡器(VCO)、低通滤波器(LFP)构成,并留有数据控制接口。

锁相环电路的工作原理是:在控制接口对R分频器和N分频器完成参数配置后。

晶振产生的参考频率(Fref)经R分频后输入到鉴相器,同时VCO的输出频率(Fout)也经N分频后输入到鉴相器,鉴相器对这两个信号进行相位比较,将比较的相位差以电压或电流的方式输出,并通过LFP滤波,加到VCO的调制端,从而控制VCO的输出频率,使鉴相器两输入端的输入频率相等。

基本组成和锁相环电路1、频率合成器电路频率合成器组成:频率合成器电路为本机收发电路的频率源,产生接收第一本机信号源和发射电路的发射信号源,发射信号源主要由锁相环和VCO电路直接产生。

如图3-4所示。

在现在的移动通信终端中,用于射频前端上下变频的本振源(LO),在射频电路中起着非常重要的作用。

本振源通常是由锁相环电路(Phase-Locked Loop)来实现。

2.锁相环:它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域3.锁相环基本原理:锁相环包含三个主要的部分:⑴鉴相器(或相位比较器,记为PD或PC):是完成相位比较的单元,用来比较输入信号和基准信号的之间的相位.它的输出电压正比于两个输入信号之相位差.⑵低通滤波器(LPF):是个线性电路,其作用是滤除鉴相器输出电压中的高频分量,起平滑滤波的作用.通常由电阻、电容或电感等组成,有时也包含运算放大器。

⑶压控振荡器(VCO):振荡频率受控制电压控制的振荡器,而振荡频率与控制电压之间成线性关系。

在PLL中,压控振荡器实际上是把控制电压转换为相位。

1、压控振荡器的输出经过采集并分频;2、和基准信号同时输入鉴相器;3、鉴相器通过比较上述两个信号的频率差,然后输出一个直流脉冲电压;4、控制VCO,使它的频率改变;5、这样经过一个很短的时间,VCO 的输出就会稳定于某一期望值。

锁相环电路是一种相位负反馈系统。

一个完整的锁相环电路是由晶振、鉴相器、R分频器、N分频器、压控振荡器(VCO)、低通滤波器(LFP)构成,并留有数据控制接口。

锁相环电路的工作原理是:在控制接口对R分频器和N分频器完成参数配置后。

晶振产生的参考频率(Fref)经R分频后输入到鉴相器,同时VCO的输出频率(Fout)也经N分频后输入到鉴相器,鉴相器对这两个信号进行相位比较,将比较的相位差以电压或电流的方式输出,并通过LFP滤波,加到VCO的调制端,从而控制VCO的输出频率,使鉴相器两输入端的输入频率相等。

目录摘要 (1)1. 设计任务 (2)2. 锁相频率合成器的硬件设计 (2)2.1 锁相环基本原理 (2)2.2 频率合成器总体设计方案 (3)2.3 VCO电路设计(MAX2620) (4)2.4 集成锁相环电路设计(MB1504) (6)2.5 单片机控制电路设计 (9)3. 软件设计 (11)3.1 MB1504数据输入设计 (11)3.2 程序流程设计 (13)总结 (15)参考文献 (16)锁相频率合成器的设计摘要由锁相环构成的间接式频率合成器在无线通信领域发挥着非常重要的作用。

通常采用锁相频率合成器的输出信号来作为无线接收机中的本振信号,以使直接频率调制器、频率解调器能够从输入信号中再生载波。

本文锁相频率合成器的整个设计方案,包括压控振荡器VCO电路设计、MB1504集成锁相环电路设计、以及单片机最小硬件系统、单片机与MB1504接口电路等硬件电路设计;软件方面,以MB1504串行数据输入格式为标准,通过分析MB1504串行数据传输时序图,建立了串行通信协议。

关键词:频率合成器;锁相环;控振荡器(VCO)1. 设计任务设计一个基于锁相环的锁相频率合成器2. 锁相频率合成器的硬件设计2.1 锁相环基本原理锁相环(PLL )是一个相位跟踪系统。

图2-1显示了最基本的锁相环方框图。

它包括三个基本部件,鉴相器(PD ) 环路滤波器(LPF )和压控振荡器(VCO )图2- 1 基本的锁相环方框图设参考信号(1) 式中 ur 为参考信号的幅度ωr 为参考信号的载波角频率θr(t)为参考信号以其载波相位ωrt 为参考时的瞬时相位若参考信号是未调载波时,则θr(t)= θ1=常数。

设输出信号为(2)式中 Uo 为输出信号的振幅ωo 为压控振荡器的自由振荡角频率θo (t)为参考信号以其载波相位ωot 为参考时的瞬时相位, 在VCO 未受控制前他是常数,受控之后他是时间函数。

则两信号之间的瞬时相位差为(3) 由频率和相位之间的关系可得两信号之间的瞬时频差为(4)()sin[()]r r r r u t U t t ωθ=+()cos[()]o o o o u t U t t ωθ=+0000()()(())()()c r r r r t t t t t t θωθωθωωθθ=+-+=-+-00()()e r d t d t dt dt θθωω=--鉴相器是相位比较器,他把输出信号uo(t)和参考信号ur(t)的相位进行比较,产生对应于两信号相位差θe (t)的误差电压ud(t)。

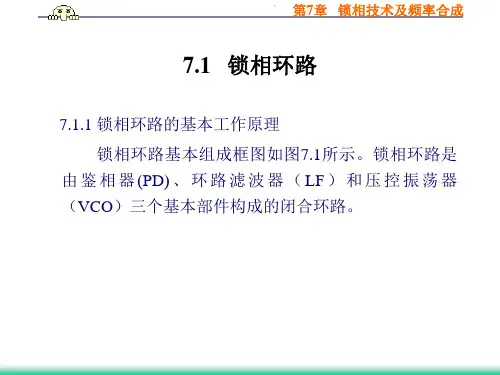

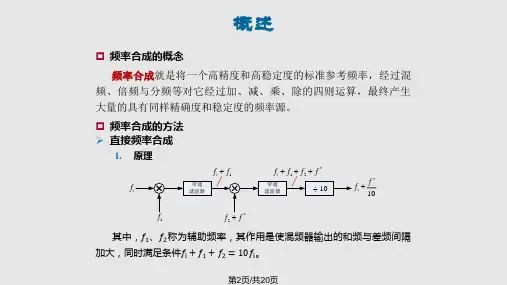

7.3 锁相频率合成电路一、锁相环路PLL(P hase-L ocked L oop)(一)锁相环路组成和工作原理鉴相器是相位比较器部件,能够鉴别出两个输入信号之间的相位误差,其输出电压与两输入信号之间的相位误差成正比。

环路滤波器具有低通特性,用来消除鉴相器输出信号中的高频分量和噪声,改善压控振荡器控制电压的频谱纯度,提高系统的稳定性。

压控振荡器是一个电压频率(相位)变换电路,当uc(t)=0时它有一个固有振荡频率,用ωo0表示,在环路滤波器的输出电压uc(t)的作用下,其振荡频率ωo在ωo0上下发生变化,因此压控振荡器的振荡频率和相位是受uc(t)控制的。

锁定状态:ϕi (t)- ϕo(t)= 常数,ωi= ωo失锁状态:ωi≠ωo(二)集成锁相环路CD4046是低频多功能单片集成锁相环路。

具有电源电压范围宽、功耗低和输入阻抗高等优点,最高工作频率为1MHz,其内部组成框图如下图所示。

二、锁相频率合成器(一)原理框图其原理框图如下图所示。

由石英晶体振荡器产生一高稳定度的标准频率源f s,经固定分频器进行M分频后得到参考频率f r,显然有f r=f s M,它被送到锁相环路的鉴相器的一个输入端,而锁相环路压控振荡器的输出频率为f o,经可编程序分频器N分频后,也送到鉴相器的另一个输入端。

当环路锁定时,一定有f r=f o N 因此,压控振荡器的输出信号频率为f o=NM f s=N f r,亦即输出信号频率f o为输入参考信号频率f r的N倍,改变分频系数N就可得到不同频率的信号输出,f r也是各输出信号频率之间的频率间隔,称为频率合成器的频率分辨率。

(二)应用实例。

锁相环及频率合成器的原理及电路设计方案介绍引言锁相环简称PLL,是实现相位自动控制的一门技术,早期是为了解决接收机的同步接收问题而开发的,后来应用在电视机的扫描电路中。

由于锁相技术的发展,该技术已逐渐应用到通信、导航、雷达、计算机到家用电器的各个领域。

自从20世纪70年代起,随着集成电路的发展,开始出现集成的锁相环器件、通用和专用集成单片锁相环,使锁相环逐渐变成一个低成本、使用简便的多功能器件。

如今,PLL技术主要应用在调制解调、频率合成、彩电色幅载波提取、雷达、FM立体声解码等各个领域。

随着数字技术的发展,还出现了各种数字PLL器件,它们在数字通信中的载波同步、位同步、相干解调等方面起着重要的作用。

随着现代电子技术的飞快发展,具有高稳定性和准确度的频率源已经成为科研生产的重要组成部分。

高性能的频率源可通过频率合成技术获得。

随着大规模集成电路的发展,锁相式频率合成技术占有越来越重要的地位。

由一个或几个高稳定度、高准确度的参考频率源通过数字锁相频率合成技术可获得高品质的离散频率源。

1 锁相环及频率合成器的原理1.1 锁相环原理PLL是一种反馈控制电路,其特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因PLL可以实现输出信号频率对输入信号频率的自动跟踪,所以PLL通常用于闭环跟踪电路。

PLL在工作的过程中,当输出信号的频率与输入信号的频率相同时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是PLL名称的由来。

PLL通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,PLL组成的原理框图如图1所示。

PLL中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控。

1 绪论1.1引言锁相环(Phase Lock Loop),简称PLL,是一种利用外部输入的参考信号控制环路内部振荡信号反馈控制电路。

他的被控制量是相位,被控对象是压控振荡器。

如果锁相环路中压控振荡器的输出信号频率发生变化,则输入到相位比较器的信号相位θv(t)和θR(t)必然会不同,使相位比较器输出一个与相位误差成比例的误差电压V d(t),经环路滤波器输出一个缓慢变化的直流电压V c(t),来控制压控振荡器输出信号的相位,使输入和输出相位差减小,直到两信号之间的相位差等于常数。

此时,压控振荡器的输出信号频率和输入信号频率相等,且环路处于锁定状态。

锁相环是构成频率合成器的核心部件。

主要由相位比较器(Phase Discriminator)、压控振荡器(V oltage Control Oscillator)、环路滤波器(Loop Filter)组成。

锁相环路是一个能跟踪输入信号相位的闭环自动控制系统。

锁相环路系统在各个领域都有很多的用途,发展将势不可挡。

锁相环路在宇宙飞行目标的跟踪、遥测和遥控、电视接收机、电动机转速控制、自动跟踪调谐等领域都有更好的发展。

频率合成是电子系统中的关键技术,是决定电子系统性能的主要设备,随着通信、数字电视、卫星定位、航空航天、雷达和电子对抗等技术的发展,频率合成技术提出了越来越高的要求。

频率合成技术是将一个或多个高稳定、高精确度的标准频率经过一定变换,产生同样高稳定度和精确度的大量离散频率的技术。

锁相环是一个相位反馈控制系统,在数字锁相环中,由于误差控制信号是离散的数字信号,而不是模拟电压,因而受控的输出电压的改变是离散的而不是连续的;此外,环路组成部件也全用数字电路实现,故而这种锁相环就称之为数字锁相环(Digital Phase Lock Loop)。

传统的锁相环由模拟电路实现,而数字锁相环与传统的模拟电路实现的PLL 相比,具有精度高且不受温度和电压影响,环路带宽和中心频率编程可调,易于构建高阶锁相环等优点,并且应用在数字系统中时,不需A/D及D/A转换。