锁相环频率合成技术

- 格式:pdf

- 大小:43.72 KB

- 文档页数:8

锁相环频率合成技术及其应用在当今的调频广播发送技术中,为了适应对发射机输出频率稳定度和频率准确度的严格要求,以及方便更换发射机频率的需要,在固态调频发射机中普遍使用了锁相技术和频率合成技术。

锁相环频率合成器成为固态调频发射机重要的组成部分。

锁相环频率合成器的优点在于其能提供频率稳定度很高的输出信号,能很好地抑制寄生分量,避免大量使用滤波器,因而有利于集成化和小型化。

而频率合成器中的程序分频器的分频比可以使用微机进行控制,易于实现发射机频率的更换及其频率显示的程控和遥控,促进全固态调频发射机的数字化、集成化和微机控制化。

将一个标准频率(如晶振参考源),经过加、减、乘、除运算,变成具有同一稳定度和准确度的多个所需频率的技术,称为频率合成技术。

控制振荡器,使其输出信号和一个参考信号之间保持确定关系的技术,称为锁相技术。

把由基准频率获得不同频率信号的组件或仪器,称为“频率合成器”。

频率合成的方法很多,但大致可分成两大类:直接合成法和间接合成法。

固态调频发射机中的频率合成器采用间接合成法。

间接合成法一般可用一个受控源(例如压控振荡器)、参考源和控制回路组成一个系统来实现。

即用一个频率源,通过分频产生参考频率,然后用锁相环(控制回路),把压控振荡器的频率锁定在某一频率上,由压控振荡器间接产生出所需要的频率输出。

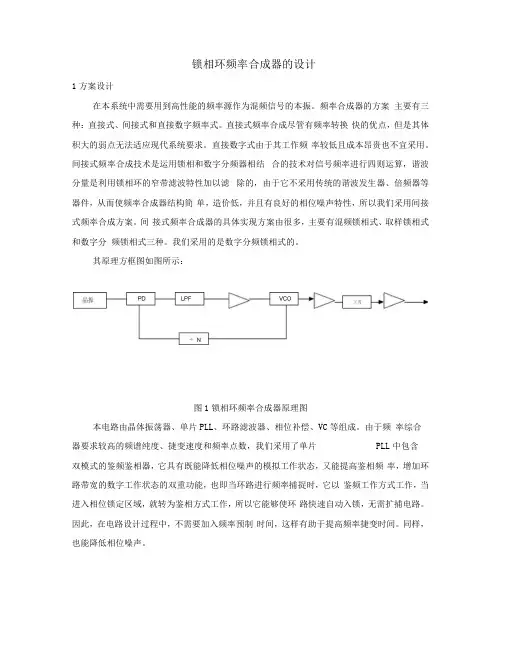

1锁相环基本工作原理一个基本的锁相环路由以下3个部件组成:压控振荡器(VCO)、鉴相器(PD)和环路滤波器(LF),如图1所示。

当锁相环开始工作时,输入参考信号的频率f i与压控振荡器的固有振荡频率f 0总是不相同的,即f i≠f 0,这一固有频率差△f=f i-f 0必然引起它们之间的相位差不断变化,并不断跨越2π角。

由于鉴相器特性是以相位差2π为周期的,因此鉴相器输出的误差电压总是在某一范围内摆动。

这个误差电压通过环路滤波器变成控制电压加到压控振荡器上,使压控振荡器的频率f 0趋向于参考信号的频率f i,直到压控振荡器的频率变化到与输入参考信号的频率相等,并满足一定条件,环路就在这个频率上稳定下来。

基于锁相环的频率合成器的设计随着现代技术的进展,具有高稳定性和精确度的频率源已经成为通信、雷达、仪器仪表、高速计算机及导航系统的主要组成部分。

高性能的频率源可通过频率合成技术获得。

随着大规模的进展,锁相式频率合成技术占有越来越重要的地位。

由一个或几个高稳定度、高精确度的参考频率源通过数字锁相频率合成技术可获得高品质的离散频率源。

1 锁相环频率合成器的原理1.1 锁相环原理锁相环(PLL)是构成频率合成器的核心部件。

主要由相位(PD)、压控(VCO)、环路(LP)和参考频率源组成。

锁相环是一种利用外部输入的参考信号控制环路内部振荡信号反馈控制。

他的被控制量是相位,被控对象是压控振荡器。

1所示,假如锁相环路中压控振荡器的输出信号频率发生变幻,则输入到相位比较器的信号相位θv(t)和θR(t)必定会不同,使相位比较器输出一个与相位误差成比例的误差Vd(t),经环路滤波器输出一个缓慢变幻的直流电压Vc(t),来控制压控振荡器输出信号的相位,使输入和输出相位差减小,直到两信号之间的相位差等于常数。

此时,压控振荡器的输出信号频率和输入信号频率相等,且环路处于锁定状态。

1.2 锁相环频率合成器原理2所示,锁相环频率合成器是由参考频率源、参考分频器、相位比较器、环路滤波器、压控振荡器、可变分频器构成。

参考分频器对参考频率源举行分频,输出信号作为相位比较器参考信号。

可变分频器对压控振荡器的输出信号举行分频,分频之后返回到相位比较器输入端与参考信号举行比较。

当环路处于锁定时有f1=f2,由于f1=fr/M,f2=fo/N,所以有fo=Nfr/M。

只要转变可变分频器的分频第1页共3页。

锁相环频率合成器的设计1方案设计在本系统中需要用到高性能的频率源作为混频信号的本振。

频率合成器的方案主要有三种:直接式、间接式和直接数字频率式。

直接式频率合成尽管有频率转换快的优点,但是其体积大的弱点无法适应现代系统要求。

直接数字式由于其工作频率较低且成本昂贵也不宜采用。

间接式频率合成技术是运用锁相和数字分频器相结合的技术对信号频率进行四则运算,谐波分量是利用锁相环的窄带滤波特性加以滤除的,由于它不采用传统的谐波发生器、倍频器等器件,从而使频率合成器结构简单,造价低,并且有良好的相位噪声特性,所以我们采用间接式频率合成方案。

间接式频率合成器的具体实现方案由很多,主要有混频锁相式、取样锁相式和数字分频锁相式三种。

我们采用的是数字分频锁相式的。

其原理方框图如图所示:图1锁相环频率合成器原理图本电路由晶体振荡器、单片PLL、环路滤波器、相位补偿、VC等组成。

由于频率综合器要求较高的频谱纯度、捷变速度和频率点数,我们采用了单片PLL中包含双模式的鉴频鉴相器,它具有既能降低相位噪声的模拟工作状态,又能提高鉴相频率,增加环路带宽的数字工作状态的双重功能,也即当环路进行频率捕捉时,它以鉴频工作方式工作,当进入相位锁定区域,就转为鉴相方式工作,所以它能够使环路快速自动入锁,无需扩捕电路。

因此,在电路设计过程中,不需要加入频率预制时间,这样有助于提高频率捷变时间。

同样,也能降低相位噪声。

另外,对于输出频率大于2GHZ勺本振源,我们采用倍频法来得到微波毫米波段的输出信号。

需要在锁相环的输出后附加微波毫米波倍频组件,以得到更高的频率。

2 各电路部件勺实现2.1单片PLL为了满足小体积的要求,我们采用单片PLL频率合成技术,单片PLL频率合成技术是现代频率合成技术的一大革命,它使得P、L、S波段实现小型化、低相位噪声频率合成器成为可能。

在本方案中,我们采用Q323睐实现。

美国QUALCO公司推出的Q3236单片PLL 芯片,其性能优良,工作频率在0〜2GHz除此之外,Q3236还具有以下特性:1)内设前置十10/11分频器2)输入灵敏度范围-10dBm〜+10dBm3)鉴相器增益高达302mv4)输入驻波比小于2:15)程序控制端口TTL/CMO兼容,8bit串行的或并行的数据线6)锁定指示7)参考分明比在1 〜16之间8)2〜128分频器的工作频率可达300MHz,90〜1295分频比的工作频率可达2GHzQ3236还包括以下几个功能部件:1)高速参考信号线性接收管和高速VCO的输出信号的线性接收器2)可以高频工作的十10/11双模前置分频器3)由M和A计数器组成的吞脉冲计数分频器4)可编程的参考分频器5)数字鉴频/鉴相器6)锁定/失锁检测电路7)TTL/CMO兼容的并行接口和8位数据总线接口使用Q323睐实现锁相环路,只需外加一阶环路滤波器和VCO参考分频比和分频比均采用外部控制模式。

认识有理数教学反思

《认识有理数教学反思》

在学习有理数的这段时间里,我感觉自己就像在数学的海洋里遨游,有时风平浪静,有时却波涛汹涌。

一开始,老师在黑板上写下那些数字,正数、负数、零,我眼睛都看直啦!心想:“这都是些啥呀?”特别是负数,那小小的负号,就像一个调皮的小精灵,总是让我迷糊。

记得有一次课堂上,老师问:“同学们,负数表示的意义你们懂了吗?”我心里直打鼓,不敢吭声。

旁边的同桌却自信满满地说:“老师,我懂!负数就是比零还小的数嘛!”老师笑着点头,我心里那个羡慕呀,反问自己:“我咋就没这么快明白呢?”

后来做练习题的时候,那一道道题目就像一个个小怪兽,张牙舞爪地等着我去打败它们。

有时候我能一下子就把它们解决掉,心里那叫一个美,就好像在炎热的夏天吃到了最爱的冰淇淋;可有时候,我却被它们难住了,抓耳挠腮,急得像热锅上的蚂蚁,嘴里嘟囔着:“这题咋这么难啊!”

小组讨论的时候可热闹啦!大家七嘴八舌地说着自己的想法。

“哎呀,这道题我觉得应该这样做!”“不对不对,你那样做错啦!”“那到底该咋办呀?”我们争得面红耳赤,可最后在大家的共同努力下,难题还是被我们攻克了,那种成就感,简直没法形容!

经过这段时间的学习,我发现有理数其实也没那么可怕。

它们就像我的小伙伴,虽然有时候会调皮捣蛋,但只要我用心去了解它们,就能和它们友好相处。

我觉得学习有理数就像爬山,一开始觉得山好高好难爬,但是只要一步一个脚印,坚持往上走,总会到达山顶,看到美丽的风景。

所以呀,遇到困难别害怕,勇敢面对,总会找到解决办法的!。

锁相与频率合成技术实验讲义桂林电子科技大学通信实验中心实验一锁相环实验一、实验原理锁相环路实质是一个负反馈的相位差自动调节系统。

1、锁相环路的构成图1 锁相环基本框图1(1)鉴相器鉴相器是相位差转换成电压的变换器(θe / V变换器、相差/电压变换器),它把两个信号U2(t)和U1(t)的相位进行比较,产主对应于两个信号相位差θe的误差电Ud(t)。

图2(a) 鉴相器模型23图2(b )异或门鉴相曲线 图2(c )数字比相器的鉴频鉴相曲线4如图2(c )的数字比相器,其特性可以理解为:① 对于相位跳变信号,如f1输入已调2PSK 信号,f2输入载波信号,则鉴相器的输入输出信号为:图3 f 1 :PSK 信号图4 f 0: 载波信号图5 f 1 与f 0 的相差θe图6 鉴相器的输出电压Ud②对于频率跳变信号,如f1输入已调2FSK信号,由高低频率f H、f L组成,f2输入f L信号,则鉴相器的输入输出信号为:图7 f1:FSK信号图8 f0:FSK的f L信号图9 f1与f0 的相差θe5(2)环路滤波器环路滤波器的作用是滤除误差电压Ud(t)中的进行积分,以保证环路所要求的性能,增加系统的稳定性。

环路滤波器常用的类型有RC积分滤波器,无源比例积分滤波器,有源比例积分滤波器。

(3)压控振荡器VCO的技术指标:中心频率、频率变化范围、频率稳定度、相位噪声、压控线性度、压控灵敏度。

图11 压控振荡器控制电压/ 输出频率(Uc-ωO)特性曲线6同步带与捕获带同步带的测量方法:环路锁定之后,缓慢提高信号源的输入频率,直到输入输出频率不相等,测出Δωh H ;用同样方法测量Δωh L ,环路锁定之后,降低信号源的输入频率,直到输入输出频率不相等,测出ΔωL 。

图20 PLL同步带范围78同步带的测量方法:由于频率太低引起环路失锁之后,缓慢提高信号源的输入频率,直到输入输出频率不相等,测出Δωp H ;用同样方法测量Δωp L 。