2.1 闩锁、设计规则和SOI

- 格式:ppt

- 大小:2.44 MB

- 文档页数:50

半导体硅片发展历程、常见形态及SOI硅片的4种制备技术?硅材料根据晶胞的排列方式不同,分为单晶硅和多晶硅。

单晶硅和多晶硅最大的区别是单晶硅的晶胞排是有序的,而多晶硅是无序的。

在制造方法方面,多晶硅一般是直接把硅料倒入坩埚中融化,然后再冷却而成。

单晶硅是通过拉单晶的方式形成晶棒(直拉法)。

在物理性质方面,两种硅的特性相差较大。

单晶硅导电能力强,光电转换效率高,单晶硅光电转换效率一般在 17%~25%左右,多晶硅效率在 15%以下。

光伏硅片:由于光电效应,且单晶硅优势明显,所以人们使用硅片完成太阳能到电能的转换。

在光伏领域使用的一般为圆角方形的单晶硅电池片。

价格较便宜的电多晶硅片也有使用,但转换效率较低。

由于光伏硅片对纯度、曲翘度等参数要求较低,所制造过程相对简单。

以单晶硅电池片为例,第一步是切方磨圆,先按照尺寸要求将单晶硅棒切割成方棒,然后将方棒的四角磨圆。

第二步是酸洗,主要是为了除去单晶方棒的表面杂质。

第三步是切片,先将清洗完毕后的方棒与工板粘贴。

然后将工板放在切片机上,按照已经设定好的工艺参数进行切割。

最后将单晶硅片清洗干净监测表面光滑度,电阻率等参数。

半导体硅片:半导体硅片比光伏硅片的要求更高。

首先,半导体行业使用的硅片全部为单晶硅,目的是为了保证硅片每个位臵的相同电学特性。

在形状和尺寸上,光伏用单晶硅片是正方形,主要有边长125mm,150mm,156mm 的种类。

而半导体用单晶硅片是圆型,硅片直径有 150mm(6 寸晶圆),200mm(8 寸晶圆)和 300mm (12 寸晶圆)尺寸。

在纯度方面,光伏用单晶硅片的纯度要求硅含量为4N-6N 之间(99.99%-99.9999%),但是半导体用单晶硅片在9N(99.9999999%)-11N(99.999999999%)左右,纯度要求最低是光伏单晶硅片的1000 倍。

在外观方面,半导体用硅片在表面的平整度,光滑度和洁净程度要比光伏用硅片的要求高。

1. 集成电路是指通过一系列特定的加工工艺,将晶体管、二极管、MOS管等有源器件和阻、电容、电感等无源器件,按一定电路互连,“集成”在一块半导体晶片(硅或砷化镓)上,封装在一个外壳内,执行特定电路或系统功能的一种器件。

2.集成电路的规模大小是以它所包含的晶体管数目或等效的逻辑门数目来衡量。

等效逻辑门通常是指两输入与非门,对于CMOS集成电路来说,一个两输入与非门由四个晶体管组成,因此一个CMOS电路的晶体管数除以四,就可以得到该电路的等效逻辑门的数目,以此确定一个集成电路的集成度。

3.摩尔定律”其主要内容如下:集成电路的集成度每18个月翻一番/每三年翻两番。

摩尔分析了集成电路迅速发展的原因,他指出集成度的提高主要是三方面的贡献:(1)特征尺寸不断缩小,大约每3年缩小 1.41倍;(2)芯片面积不断增大,大约每3年增大 1.5倍;(3)器件和电路结构的改进。

4.反标注是指将版图参数提取得到的分布电阻和分布电容迭加到相对应节点的参数上去,实际上是修改了对应节点的参数值。

5.CMOS反相器的直流噪声容限:为了反映逻辑电路的抗干扰能力,引入了直流噪声容限作为电路性能参数。

直流噪声容限反映了电流能承受的实际输入电平与理想逻辑电平的偏离范围。

6. 根据实际工作确定所允许的最低输出高电平,它所对应的输入电平定义为关门电平;给定允许的最高输出低电平,它所对应的输入电平为开门电平7. 单位增益点.在增益为0和增益很大的输入电平的区域之间必然存在单位增益点,即dVout/dVin=1的点8. “闩锁”现象在正常工作状态下,PNPN四层结构之间的电压不会超过Vtg,因此它处于截止状态。

但在一定的外界因素触发下,例如由电源或输出端引入一个大的脉冲干扰,或受r射线的瞬态辐照,使PNPN四层结构之间的电压瞬间超过Vtg,这时,该寄生结构中就会出现很大的导通电流。

只要外部信号源或者Vdd和Vss能够提供大于维持电流Ih的输出,即使外界干扰信号已经消失,在PNPN四层结构之间的导通电流仍然会维持,这就是所谓的“闩锁”现象9. 延迟时间:T pdo ——晶体管本征延迟时间;UL ——最大逻辑摆幅,即最大电源电压;Cg ——扇出栅电容(负载电容);Cw ——内连线电容;Ip ——晶体管峰值电流。

CMOS集成电路闩锁效应抑制技术董丽凤;李艳丽;王吉源【摘要】闩锁效应是CMOS集成电路在实际应用中失效的主要原因之一,而且随着器件特征尺寸越来越小,使得CMOS电路结构中的闩锁效应日益突出.文章以P 阱CMOS反相器为例,从CMOS集成电路的工艺结构出发,采用可控硅等效电路模型,较为详细地分析了闩锁效应的形成机理,给出了闩锁效应产生的三个基本条件,并从版图设计和工艺设计两方面总结了几种抑制闩锁效应的关键技术.【期刊名称】《电子与封装》【年(卷),期】2010(010)009【总页数】3页(P28-30)【关键词】CMOS集成电路;闩锁效应;可控硅;抑制【作者】董丽凤;李艳丽;王吉源【作者单位】江西理工大学信息工程学院,江西,赣州,341000;江西理工大学信息工程学院,江西,赣州,341000;江西理工大学信息工程学院,江西,赣州,341000【正文语种】中文【中图分类】TM341CMOS(Complementary Metal-Oxide-Semiconductor)集成电路是目前大规模(LSI)和超大规模(VLSI)集成电路中广泛应用的一种电路结构,相对于传统的双极型、NMOS和PMOS集成电路而言,其在功率消耗、噪声抑制等方面具有明显的优势,虽然CMOS电路具有以上众多优点,但也有一些由于自身结构引发的寄生效应限制了其优越性的充分发挥,隐含于体硅CMOS(指在硅衬底上制作的CMOS)结构中的闩锁效应就是一个最典型的例子,并且随着器件尺寸的不断缩小,闩锁效应对电路性能的影响将愈发明显。

闩锁效应(latch up)是指在体硅CMOS结构中,从电源到地存在的PNPN寄生可控硅结构,在满足可控硅触发条件下,引起电源到地的极大电流,破坏电路正常工作乃至烧毁整个电路的现象,也称自锁效应。

闩锁效应往往发生在芯片中某一局部区域,有两种情况:一种是闩锁只发生在外围与输入输出有关的地方,另一种是闩锁可能发生在芯片的任何地方,在使用中前一种情况遇到较多。

基于SOI工艺的高压LED驱动设计诸剑慧;何乐年;林玲【摘要】In order to expand the application of LED driver into high-voltage region, the silicon-on-insulator(SOI) technology was used. Based on this technology, an LED driver was designed. The system diagram of the LED driver was introduced at first and then the important blocks were described in detail. This LED driver works in peak current mode, and has a wide input range from 40 V to 625 V. It provides two dimming functions; linear dimming and pulse width modulation(PWM) dimming, and could be used in tens to a hundred series LED applications. The prototype chip was designed by Cadence Spectre tools and fabricated in XFAB 1 μm SOI Process. The simulation and test results verify this design. This research lays the foundation for the design of the high-voltage power management chips which are based on SOI process.%为了解决LED驱动芯片因耐压低而在高压领域应用受限制的问题,将绝缘体上硅(SOI)技术应用到LED驱动的设计中,设计了一款基于SOI工艺的高压LED驱动芯片.首先提出了该驱动的系统框图,并介绍了其工作原理,然后对各重要模块进行了详细的介绍.该LED驱动输入电压范围为40 V~625 V,采用峰值电流模式控制,并提供线性与脉宽调制(PWM)两种调光方式,根据不同应用,外接的LED灯可达十几至上百个不等.采用XFAB 1 μm SOI工艺,并使用Cadence的Spectre系列软件进行了仿真.仿真与测试结果验证了该驱动的良好性能.该设计对基于SOI工艺的高压电源管理芯片的设计具有指导意义.【期刊名称】《机电工程》【年(卷),期】2011(028)008【总页数】5页(P1028-1032)【关键词】绝缘体上硅;高压;LED驱动;峰值电流模式;脉宽调制【作者】诸剑慧;何乐年;林玲【作者单位】浙江大学超大规模集成电路设计研究所,浙江杭州310027;浙江大学超大规模集成电路设计研究所,浙江杭州310027;浙江大学超大规模集成电路设计研究所,浙江杭州310027【正文语种】中文【中图分类】TN4330 引言当前,绝缘体上硅(SOI)已经成为半导体行业发展的一大亮点。

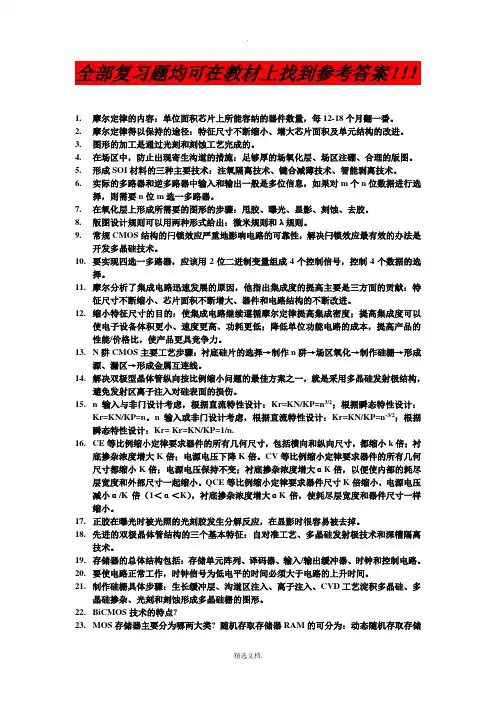

全部复习题均可在教材上找到参考答案!!!1.摩尔定律的内容:单位面积芯片上所能容纳的器件数量,每12-18个月翻一番。

2.摩尔定律得以保持的途径:特征尺寸不断缩小、增大芯片面积及单元结构的改进。

3.图形的加工是通过光刻和刻蚀工艺完成的。

4.在场区中,防止出现寄生沟道的措施:足够厚的场氧化层、场区注硼、合理的版图。

5.形成SOI材料的三种主要技术:注氧隔离技术、键合减薄技术、智能剥离技术。

6.实际的多路器和逆多路器中输入和输出一般是多位信息,如果对m个n位数据进行选择,则需要n位m选一多路器。

7.在氧化层上形成所需要的图形的步骤:甩胶、曝光、显影、刻蚀、去胶。

8.版图设计规则可以用两种形式给出:微米规则和λ规则。

9.常规CMOS结构的闩锁效应严重地影响电路的可靠性,解决闩锁效应最有效的办法是开发多晶硅技术。

10.要实现四选一多路器,应该用2位二进制变量组成4个控制信号,控制4个数据的选择。

11.摩尔分析了集成电路迅速发展的原因,他指出集成度的提高主要是三方面的贡献:特征尺寸不断缩小、芯片面积不断增大、器件和电路结构的不断改进。

12.缩小特征尺寸的目的:使集成电路继续遵循摩尔定律提高集成密度;提高集成度可以使电子设备体积更小、速度更高、功耗更低;降低单位功能电路的成本,提高产品的性能/价格比,使产品更具竞争力。

13.N阱CMOS主要工艺步骤:衬底硅片的选择→制作n阱→场区氧化→制作硅栅→形成源、漏区→形成金属互连线。

14.解决双极型晶体管纵向按比例缩小问题的最佳方案之一,就是采用多晶硅发射极结构,避免发射区离子注入对硅表面的损伤。

15.n输入与非门设计考虑,根据直流特性设计:Kr=KN/KP=n3/2;根据瞬态特性设计:Kr=KN/KP=n。

n输入或非门设计考虑,根据直流特性设计:Kr=KN/KP=n-3/2;根据瞬态特性设计:Kr= Kr=KN/KP=1/n.16.CE等比例缩小定律要求器件的所有几何尺寸,包括横向和纵向尺寸,都缩小k倍;衬底掺杂浓度增大K倍;电源电压下降K倍。

CMOS工艺中抗闩锁技术的研究朱琪;华梦琪【摘要】伴随着CMOS工艺技术的发展,CMOS电路已经成为VLSI制造中的主流,而CMOS器件特征尺寸的快速缩小和CMOS电路的广泛应用,使得CMOS 电路中的latch-up效应引起的可靠性问题也越来越受到大家的重视。

阐述了CMOS工艺中闩锁的概念、原理及其给电路的可靠性带来的严重后果,深入分析了产生闩锁效应的条件、触发方式,并针对所分析的闩锁原因从版图设计、工艺改良、电路应用三个方面提出了一些防闩锁的优化措施,以满足和提高CMOS电路的可靠性要求。

%With the development of CMOS process technology, CMOS VLSI circuit manufacturing has become mainstream, and widely applied rapidly reduced feature sizes in CMOS devices and the CMOS circuit, a CMOS circuit so that the reliability of the effect caused by the latch-up increasingly attentions. The paper described the concept of latch CMOS process, the serious consequences of the generation of latch-up condition, the way conflict with the law, and the reasons for the latch from the layout analysis, process improvement, three circuit applications made some latch optimization measures to meet the requirements and improve the reliability of CMOS circuits.【期刊名称】《电子与封装》【年(卷),期】2014(000)004【总页数】4页(P34-37)【关键词】闩锁;寄生BJT;PNPN结构【作者】朱琪;华梦琪【作者单位】中国电子科技集团公司第58研究所,江苏无锡214035;中国电子科技集团公司第58研究所,江苏无锡214035【正文语种】中文【中图分类】TN4331 引言CMOS电路由于具有高集成度、低功耗、工艺成熟等优越性而成为VLSI制造中的主流,但同时我们应该看到,CMOS电路中的Latch-up(闩锁)效应严重影响着产品的可靠性[1]。

集成电路版图设计什么是集成电路版图设计?所谓的集成电路版图设计是根据逻辑与电路功能和性能要求以及工业水平要求来设计芯片制造时光刻用的掩模版图,实现IC设计的最终输出其中版图是一组相互套合的图形,各层版图表示不同的工艺步骤,每层版图用不同的图案表示。

DRS和LVS开始前需要做哪些准备?DRC开始前需要准备好版图文件和DRC规则文件,LVS开始前需要准备好版图文件、电路图文件和runset文件为什么需要进行版图数据处理?在形成整体的版图并通过DRC、LVS的验证后,版图设计过程就完成了,但这个时候的版图GDS数据还不能拿去制作掩模版,还需要对GDS数据进行处理。

该版图GDS数据中的层次跟最终模板的层次并不是完全一致的,该版图GDS 数据还需要进行工艺涨缩处理,以满足掩模版制作需求。

集成电路设计流程:功能要求、电路设计、电路仿真、版图设计、版图验证、后仿及优化。

光刻工艺流程:底膜处理、涂胶、前烘、曝光、显影、坚膜、显影检测、刻蚀、去胶、最终检验。

工艺要求:特征尺寸、集成度、晶圆尺寸工艺文件夹包含:技术文件、显示文件DRC步骤:建立DRC运行目录、修改规则文件、导出gds2文件、编译规则文件、执行DRC检查、DRC结构分析狗骨电阻的优点:能够控制电流走向,使电阻误差减小。

集成电路发展的趋势是什么?制程工艺越来越精细、集成度越来越高、电路功能越来越强大、越来越趋向于智能化集成电路中的电阻分为哪几种?有扩散电阻、多晶硅电阻、阱电阻简述为什么尽可能多地设计阱接触?能大大减小寄生电阻的阻值,有效抑制闩锁。

在绘制PMOS版图时,为什么在接触区域进行SN注入?SN注入降低了接触电阻,接触孔容易刻蚀,形成欧姆接触。

简述什么是闩锁效应?闩锁效应是CMOS工艺所特有的寄生效应,严重会导致电路的失效,甚至烧毁芯片。

什么是保护环,保护环的主要作用?能抑制闩锁效应的设计方式就是保护环作用: 1.阻碍少子保护环 2.载流子注入类型为少子 3.保护类型为少子 4.电位保持PN结反偏 5.起分流作用。

Latch up:即闩锁效应,又称自锁效应、闸流效应,它是由寄生晶体管引起的,属于CMOS电路的缺点。

通常在电路设计和工艺制作中加以防止和限制。

该效应会在低电压下导致大电流,这不仅能造成电路功能的混乱,而且还会使电源和地线间短路,引起芯片的永久性损坏。

防止:在集成电路工艺中采用足够多的衬底接触。

Latch up 的定义Latch up 最易产生在易受外部干扰的I/O电路处, 也偶尔发生在内部电路Latch up 是指cmos晶片中, 在电源power VDD和地线GND(VSS)之间由于寄生的PNP和NPN双极性BJT相互影响而产生的一低阻抗通路, 它的存在会使VDD和GND之间产生大电流随着IC制造工艺的发展, 封装密度和集成度越来越高,产生Latch up的可能性会越来越大Latch up 产生的过度电流量可能会使芯片产生永久性的破坏, Latch up 的防范是IC Layout 的最重要措施之一Latch up 的原理图分析Latch up 的原理分析Q1为一垂直式PNP BJT, 基极(base)是nwell, 基极到集电极(collector)的增益可达数百倍;Q2是一侧面式的NPN BJT,基极为P substrate,到集电极的增益可达数十倍;Rwell是nwell的寄生电阻;Rsub是substrate电阻。

以上四元件构成可控硅(SCR)电路,当无外界干扰未引起触发时,两个BJT处于截止状态,集电极电流是C-B的反向漏电流构成,电流增益非常小,此时Latch up不会产生。

当其中一个BJT的集电极电流受外部干扰突然增加到一定值时,会反馈至另一个BJT,从而使两个BJT因触发而导通,VDD至GND(VSS)间形成低抗通路,Latch up由此而产生。

CMOS电路中的寄生双极型晶体管部分出现闩锁,必须满足以下几个条件:(1) 电路要能进行开关转换,其相关的PNPN结构的回路增益必须大于1即βnpn*βpnp >1,在最近的研究中,把闩锁产生的条件用寄生双极晶体管的有效注入效率和小信号电流增益来表达。