集成电路版图第6章:寄生参数

- 格式:ppt

- 大小:672.50 KB

- 文档页数:46

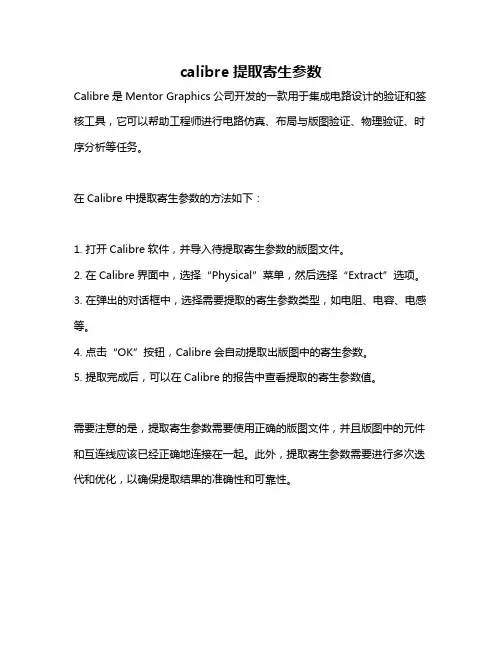

calibre提取寄生参数

Calibre是Mentor Graphics公司开发的一款用于集成电路设计的验证和签核工具,它可以帮助工程师进行电路仿真、布局与版图验证、物理验证、时序分析等任务。

在Calibre中提取寄生参数的方法如下:

1. 打开Calibre软件,并导入待提取寄生参数的版图文件。

2. 在Calibre界面中,选择“Physical”菜单,然后选择“Extract”选项。

3. 在弹出的对话框中,选择需要提取的寄生参数类型,如电阻、电容、电感等。

4. 点击“OK”按钮,Calibre会自动提取出版图中的寄生参数。

5. 提取完成后,可以在Calibre的报告中查看提取的寄生参数值。

需要注意的是,提取寄生参数需要使用正确的版图文件,并且版图中的元件和互连线应该已经正确地连接在一起。

此外,提取寄生参数需要进行多次迭代和优化,以确保提取结果的准确性和可靠性。

DIVA中寄生元器件提取语句介绍DIVA中关于寄生元件提取的语句很多,分别是measureParasitic、multiLevelParasitic、measureFringe、calculatParasitic、saveParasitic、attachParasitic。

下面将就它们的用法作一些简单的介绍:在介绍之前,我们有必要澄清几个概念:首先,我们为什么要对版图进行寄生元件提取?很简单,我们都知道,在电路的版图当中,由于工艺上的或是其他的一些不可避免的因素的影响,会产生一些寄生的元件。

比如说:寄生电容、寄生电阻等等。

而这些寄生元件又往往会对我们的电路特性带来负面的影响,所以我们得尽量的减少其生成。

但就如上面所说的一样,一些寄生元件的产生有其必然性,这就要求我们设计的芯片能够在这些负面的影响下也能体现较好的特性。

所以在一块芯片的版图完成之后,我们所要进行的很重要的一步工作就是提取版图中的寄生参数并将其代入电路中进行模拟。

这就是我们所说的后模拟。

只有经过后模拟的版图才是最接近实际情况的器件版图。

另外,我们知道,在版图验证中LVS 是非常重要的。

在我们做完寄生参数的提取工作之后,下一步要进行的将是带寄生参数的SPICE模拟。

也就是说我们所提取得那些寄生参数将被加入到SPICE的网表(netlist)中去。

但是,在LVS 中我们却不能将这些寄生元件加入到其网表中,因为这些元件在原始版图中事实上是不存在的。

所以,我们将会得到两个不同的视图(view):SPICE view和LVS view。

接下来,我们将进入正题。

在具体到每一个语句之前,我先介绍一下后面会经常用到的一些测量语句。

Area:面积 perimeter:周长 length:长度 bends:凹角(concave corner)corners:凸角(convex corner) angle:任意角(bends +corners)calculatParastic语句介绍:这个函数可以在前面measureParasitic语句所导出的值或是calculatParasitic语句所计算出的值的基础上进行进一步的计算。

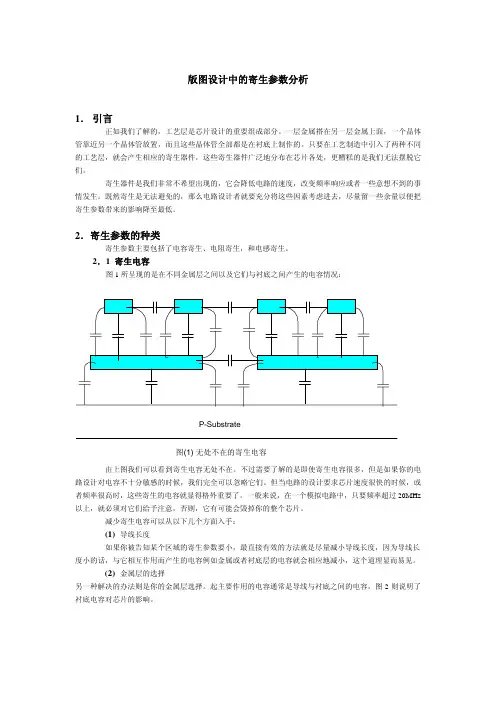

版图设计中的寄生参数分析1.引言正如我们了解的,工艺层是芯片设计的重要组成部分。

一层金属搭在另一层金属上面,一个晶体管靠近另一个晶体管放置,而且这些晶体管全部都是在衬底上制作的。

只要在工艺制造中引入了两种不同的工艺层,就会产生相应的寄生器件,这些寄生器件广泛地分布在芯片各处,更糟糕的是我们无法摆脱它们。

寄生器件是我们非常不希望出现的,它会降低电路的速度,改变频率响应或者一些意想不到的事情发生。

既然寄生是无法避免的,那么电路设计者就要充分将这些因素考虑进去,尽量留一些余量以便把寄生参数带来的影响降至最低。

2.寄生参数的种类寄生参数主要包括了电容寄生、电阻寄生,和电感寄生。

2.1 寄生电容图1所呈现的是在不同金属层之间以及它们与衬底之间产生的电容情况:图(1) 无处不在的寄生电容由上图我们可以看到寄生电容无处不在。

不过需要了解的是即使寄生电容很多,但是如果你的电路设计对电容不十分敏感的时候,我们完全可以忽略它们。

但当电路的设计要求芯片速度很快的时候,或者频率很高时,这些寄生的电容就显得格外重要了。

一般来说,在一个模拟电路中,只要频率超过20MHz 以上,就必须对它们给予注意,否则,它有可能会毁掉你的整个芯片。

减少寄生电容可以从以下几个方面入手:(1)导线长度如果你被告知某个区域的寄生参数要小,最直接有效的方法就是尽量减小导线长度,因为导线长度小的话,与它相互作用而产生的电容例如金属或者衬底层的电容就会相应地减小,这个道理显而易见。

(2)金属层的选择另一种解决的办法则是你的金属层选择。

起主要作用的电容通常是导线与衬底之间的电容,图2则说明了衬底电容对芯片的影响。

Noisy Quiet图(2) 衬底电容产生的噪声影响如上所示,电路1和电路2都对地产生了一个衬底电容,衬底本身又有一个寄生电阻,这样一来电路1的噪声就通过衬底耦合到电路2上面,这是我们不希望看到的。

(设法使所有的噪声都远离衬底)因此我们改变一下金属层,通常情况下,最高金属层所形成的电容总是最小的。

ads 晶体管寄生参数

一、概述

ads晶体管寄生参数是影响晶体管性能的重要因素,它们包括寄生电容、寄生电阻和寄生电感等。

这些参数会对晶体管的交流性能产生影响,从而影响电路的性能。

二、寄生电容

晶体管的寄生电容主要来自于半导体材料中的杂质和缺陷,它们构成了晶体管中的电容结构。

这些电容结构会对晶体管的交流信号产生影响,影响晶体管的开关速度和增益。

三、寄生电阻

晶体管的寄生电阻主要来自于半导体材料的表面和界面,它们构成了晶体管中的电阻结构。

这些电阻结构会对晶体管的直流性能产生影响,影响晶体管的电压和电流特性。

四、寄生电感

晶体管的寄生电感主要来自于半导体材料的形状和尺寸,它们构成了晶体管中的电感结构。

这些电感结构会对晶体管的交流信号产生影响,影响晶体管的频率响应和稳定性。

五、总结

了解并控制晶体管的寄生参数对于优化电路性能至关重要。

在实际应用中,应通过优化设计、选择合适的材料和工艺等方法,减小晶体管的寄生参数,提高电路的性能和稳定性。

此外,对于特定的应用场景,还需针对性地分析和计算寄生参数,以获得最佳的设计方案。

六、参考文献

(请在此插入参考文献)。

MOS寄生参数1. 寄生参数的定义在通信系统中,MOS(Mean Opinion Score)是一种用于评估语音质量的指标。

而寄生参数则是指在MOS评估中使用的一组相关参数,用来描述语音质量与其它因素之间的关系。

寄生参数主要包括以下几个方面:•时延(Delay):指信号传输过程中引入的时延,包括传输时延、处理时延等。

•抖动(Jitter):指信号传输过程中引入的抖动现象,即信号到达时间上的不确定性。

•丢包率(Packet Loss Rate):指信号传输过程中发生的数据丢失率。

•噪声(Noise):指信号传输过程中受到的干扰噪声。

•声音失真(Distortion):指信号经过编解码等处理后引入的失真现象。

2. 寄生参数与语音质量之间的关系寄生参数与语音质量之间存在着密切的关系。

下面将分别介绍各个寄生参数对语音质量影响的具体情况。

2.1 时延时延是影响语音通信质量最直接、最敏感的一个因素。

较大的时延会导致通话中出现明显的对话延迟,给用户带来不适感,从而降低语音质量。

一般来说,时延在150ms以内被认为是可接受的。

2.2 抖动抖动是指信号到达时间上的不确定性,会导致声音出现断续、卡顿等现象。

较大的抖动会使声音听起来不连贯,影响语音通信的可理解性和自然性。

为了保证语音质量,抖动应尽量控制在20ms以内。

2.3 丢包率丢包率是指信号传输过程中发生的数据丢失率。

较高的丢包率会导致语音信号缺失、声音断续等问题,降低语音通信的可理解性和连贯性。

一般来说,丢包率应控制在1%以下。

2.4 噪声噪声是指信号传输过程中受到的干扰噪声。

噪声会使语音听起来杂乱无章、清晰度下降,影响语音通信的可理解性和舒适度。

为了提高语音质量,应尽量减小噪声干扰。

2.5 声音失真声音失真是指信号经过编解码等处理后引入的失真现象。

较大的失真会使语音听起来不自然、含糊不清,降低语音通信的可理解性和自然性。

为了保证语音质量,应尽量减小声音失真。