第5章80868088总线操作和时序

- 格式:ppt

- 大小:6.48 MB

- 文档页数:70

微机原理第2章8086/8088系统结构8086/8088 的工作时序1. 时钟周期、总线周期、指令周期微机原理时钟周期:是CPU的基本时间单位,记为T,其值为计算机主频的倒数。

微机原理时钟周期:是CPU 的基本时间单位,记为T ,其值为计算机主频的倒数。

总线周期:CPU 通过总线对存储器或I/O 进行1次访问所需要的时间。

它至少包含4个T ,记为T 1,T 2,T 3,T 4.1. 时钟周期、总线周期、指令周期1. 时钟周期、总线周期、指令周期微机原理的时间,它包含一个或多个总线周期。

常采用MIPS(Million Instructions Per Second)作单位。

微机原理(1) 8086读总线周期T 1T 2T3T 4一个总线周期CLK A 19~A 16S 6~S 3A 19/S 6 ~ A 16/S 3DATA INAD 15 ~ AD 0ALE 低=I/O ,高=MM/IORD DT/R DENA 15~A 02. 读/写工作时序微机原理(2) 8086写总线周期T 1T 2T 3T 4一个总线周期CLK A 19 ~ A 16S 6 ~ S 3A 19/S 6 ~ A 16/S 3DATA OUTAD 15 ~ AD 0ALE 高=I/O ,低=MM/IOWRDT/R DENA 15~A 0微机原理(3)8086具有等待状态的读总线周期T 1T 2T 3T W 一个总线周期CLK A 19~A 16A 19/S 6 ~ A 16/S 3DATA INAD 15 ~ AD 0ALE 低=I/O ,高=MM/IORD DT/RDEN A 15~A 0T 4READYWAITREADYS 6~S 3微机原理(4) 8088读总线周期T 1T 2T 3T 4一个总线周期CLK A 19~A 16S 6~S 3A 19/S 6 ~ A 16/S 3DATA INAD 7 ~ AD 0ALE 高=I/O ,低=MIO/MRD DT/R DENA 7~A 0A 15 ~ A 8A 15~A 8微机原理例1:在8088 CPU 中对存储器进行读操作时,CPU 引脚的IO/M 、RD 、WR 、DT/R 的输出电平分别是什么?例2:在若在1个总线周期中,插入了3个T W ,请问在该总线周期中对READY 信号进行了几次采样?低电平低电平高电平低电平4微机原理下次课见。

微机原理复习总结第1章基础知识⏹计算机中的数制⏹BCD码与二进制数11001011B等值的压缩型BCD码是11001011B。

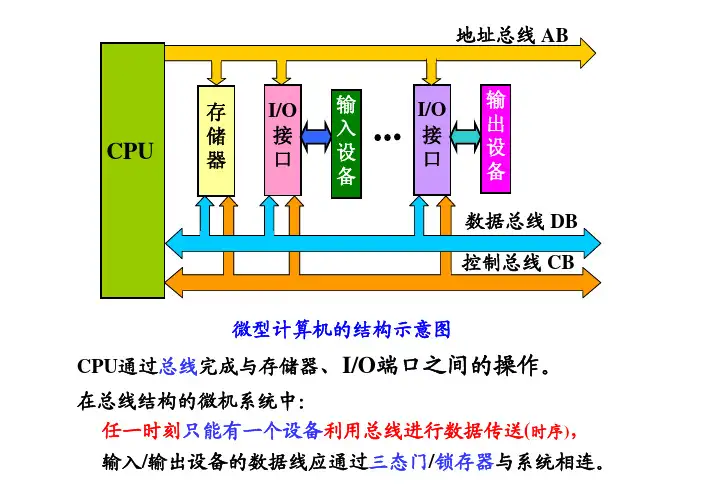

F第2章微型计算机概论⏹计算机硬件体系的基本结构计算机硬件体系结构基本上还是经典的冯·诺依曼结构,由运算器、控制器、存储器、输入设备和输出设备5个基本部分组成。

⏹计算机工作原理1.计算机由运算器、控制器、存储器、输入设备和输出设备5个基本部分组成。

2.数据和指令以二进制代码形式不加区分地存放在存储器重,地址码也以二进制形式;计算机自动区分指令和数据。

3.编号程序事先存入存储器。

⏹微型计算机系统是以微型计算机为核心,再配以相应的外围设备、电源、辅助电路和控制微型计算机工作的软件而构成的完整的计算机系统。

⏹微型计算机总线系统数据总线 DB(双向)、控制总线CB(双向)、地址总线AB(单向);⏹8086CPU结构包括总线接口部分BIU和执行部分EUBIU负责CPU与存储器,,输入/输出设备之间的数据传送,包括取指令、存储器读写、和I/O读写等操作。

EU部分负责指令的执行。

⏹存储器的物理地址和逻辑地址物理地址=段地址后加4个0(B)+偏移地址=段地址×10(十六进制)+偏移地址逻辑段:1). 可开始于任何地方只要满足最低位为0H即可2). 非物理划分3). 两段可以覆盖1、8086为16位CPU,说明(A )A. 8086 CPU内有16条数据线B. 8086 CPU内有16个寄存器C. 8086 CPU内有16条地址线D. 8086 CPU内有16条控制线解析:8086有16根数据线,20根地址线;2、指令指针寄存器IP的作用是(A )A. 保存将要执行的下一条指令所在的位置B. 保存CPU要访问的内存单元地址C. 保存运算器运算结果内容D. 保存正在执行的一条指令3、8086 CPU中,由逻辑地址形成存储器物理地址的方法是(B )A. 段基址+偏移地址B. 段基址左移4位+偏移地址C. 段基址*16H+偏移地址D. 段基址*10+偏移地址4、8086系统中,若某存储器单元的物理地址为2ABCDH,且该存储单元所在的段基址为2A12H,则该存储单元的偏移地址应为(0AADH )。

第五章8088的总线操作和时序本章内容主要介绍8088执行指令的三种周期,以及它们之间的区别和相互联系,在此基础上结合8088芯片引脚信号的功能分别介绍最小、最大组态下三总线信号在这些典型的总线周期中出现的时间关系。

5.1重点与难点本章的学习重点包括8088芯片外部的三总线结构,最大组态与最小组态的基本配置,总线控制器8288在最大组态配置中的作用,在最大组态系统或最小组态系统中的时序配合问题。

3.1.1 8088的工作周期在微型机系统中,CPU的操作都是在系统主时钟CLK的控制下按节拍有序进行的。

CPU 执行一条指令的时间(包括取指令、指令译码和执行该指令所需的全部时间)称为一个指令周期。

把通过外系统总线对存储器或I/O端口进行一次读/写操作的过程称为总线周期,T 状态就是CLK时钟周期。

一个指令周期由若干个总线周期组成。

每个总线周期通常包含4个T状态,即T l、T2、T3、T4。

在T1状态,CPU往地址/数据复用总线(AD7~0)和地址/状态复用总线(A19~16/S6~3)上发地址信息。

在T2状态, 从地址/数据总线和地址/状态总线上撤消地址信息,并使地址/数据总线成为高阻态,为传送数据信息作准备。

与此同时, 从地址/状态总线的输出4位状态信息。

在T3状态, 地址/状态总线继续输出状态信息, 地址/数据总线用于传送数据信息。

在存储器或外设不能及时地配合CPU传送数据时, 它们可以向CPU 请求, 在T3周期之后插入一个或多个等待状态Tw。

在T4状态, 一个总线周期结束。

在一个总线周期中,A15~8始终输出地址信息。

如果一个总线周期之后, 不立即执行下一个总线周期, 那么系统总线就会处于空闲状态Ti, 执行空闲周期。

3.1.2 8088的总线操作1.8088芯片引脚构成及在最大最小组态下的意义。

8088的芯片引脚可分为两种:与工作模式无关的和与工作模式有关的。

与工作模式相关的包括24~31、33、34脚。

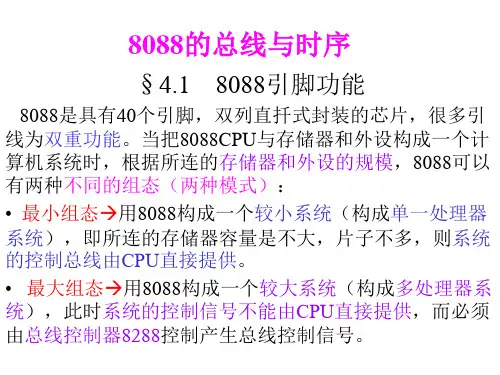

第五讲8086/8088微处理器引脚功能、总线结构和时序第一节、8086/8088引脚信号和功能第二节、8086/8088最小模式和最大模式第三节、8086/8088主要操作第四节、8086存储器的分体结构第一节8086/8088引脚信号和功能一、8086/8088的两种工作模式二、8086/8088引脚信号和功能一、8086/8088的两种工作模式8086/8088CPU有两种模式:最小模式和最大模式。

y最小模式系统中只有8086/8088一个微处理器(单处理器模式)。

所有的总线控制信号都直接由8086/8088产生。

总线控制逻辑电路被减少到最小。

适合于较小规模的系统。

y最大模式包含两个(以上)微处理器,其中一个主处理器是8086/8088,其他的处理器称为协处理器,协助主处理器工作。

适合于中等规模或大型的8086/8088系统中。

系统的控制总线由总线控制器8288来提供:¾8288增强了8088CPU总线的驱动能力;¾将8086的状态信号(S2~S0)进行译码,提供8086对存储器、I/O接口进行控制所需的信号。

最小模式与最大模式的主要区别8086/8088外部引脚图(括号内为最大模式时引脚名)8088地A14A13A12A11A10A9A8AD7AD6AD5AD4AD3AD2AD1AD0NMI INTR CLK 地Vcc(5V)A15A16/S3A17/S4A18/S5A19/S6SS0(HIGH)MN/MX RDHOLD(RQ/GT0)HLDA(RQ/GT1)WR(LOCK M/IO DT/R(S1)DEN(S0)ALE(QS0)INTA(QS1)TEST READY RESETVcc(5V)AD15A16/S3A17/S4A18/S5A19/S6BHE/S7MN/MX RDHOLD (RQ/GT0)HLDA (RQ/GT1)WR (LOCK)M/IO (S2)DT/R ( S1 )DEN (S0 )ALE (QS0)INTA (QS1)TEST READY RESET8086Vcc(5V)AD15A16/S3A17/S4A18/S5A19/S6BHE/S7MN/MX RDHOLD (RQ/GT0)HLDA (RQ/GT1)WR (LOCK)M/IO (S2)DT/R ( S1 )DEN (S0 )ALE (QS0)INTA (QS1)TEST READY RESET8086(1)地址/数据复用引脚(AD15~AD0 )是分时复用①在总线周期来输出要访问的存储器地址或口地址A15~A②在总线周期的其他时间内,作为双向数据总线:对8086就是(对8088地AD14AD13Vcc(5V)AD15A16/S3A17/S4A18/S5A19/S6BHE/S7MN/MXRDHOLD (RQ/GT0)HLDA (RQ/GT1)WR (LOCK)M/IO (S2)DT/R ( S1 )DEN (S0 )ALE (QS0)INTA (QS1)TESTREADYRESET8861.两种模式下公共引脚(2) 地址/状态复用引脚A19/S6~ A16/S3分时复用引脚,输出,三态。

8086CPU系统、总线操作和时序8086CPU系统、总线操作和时序第⼀节 8086的引脚信号与功能回顾:8086/8088微型计算机的组成、结构及微机系统的⼯作过程,微机系统的存储器组织及相关概念。

本讲重点:8086/8088CPU的两种⼯作模式,8086/8088CPU的外部结构,即引脚信号及其功能。

讲授内容:⼀、 8086/8088微处理器⼯作模式及外部结构1.8086/8088CPU的两种⼯作模式为了适应各种使⽤场合,在设计8088/8086CPU芯⽚时,就考虑了其应能够使它⼯作在两种模式下,即最⼩模式与最⼤模式。

所谓最⼩模式,就是系统中只有⼀个8088/8086微处理器,在这种情况下,所有的总线控制信号,都是直接由8088/8086CPU 产⽣的,系统中的总线控制逻辑电路被减到最少,该模式适⽤于规模较⼩的微机应⽤系统。

最⼤模式是相对于最⼩模式⽽⾔的,最⼤模式⽤在中、⼤规模的微机应⽤系统中,在最⼤模式下,系统中⾄少包含两个微处理器,其中⼀个为主处理器,即8086/8086CPU,其它的微处理器称之为协处理器,它们是协助主处理器⼯作的。

与8088/8086CPU配合⼯作的协处理器有两类,⼀类是数值协处理器8087 另⼀类是输⼊/输出协处理器8089。

8087是⼀种专⽤于数值运算的协处理器,它能实现多种类型的数值运算,如⾼精度的整型和浮点型数值运算,超越函数(三⾓函数、对数函数)的计算等,这些运算若⽤软件的⽅法来实现,将耗费⼤量的机器时间。

换句话说,引⼊了8087协处理器,就是把软件功能硬件化,可以⼤⼤提⾼主处理器的运⾏速度。

8089协处理器,在原理上有点像带有两个DMA通道的处理器,它有⼀套专门⽤于输⼊/输出操作的指令系统,但是8089⼜和DMA控制器不同,它可以直接为输⼊/输出设备服务,使主处理器不再承担这类⼯作。

所以,在系统中增加8089协处理器之后,会明显提⾼主处理器的效率,尤其是在输⼊/输出操作⽐较频繁的系统中。