第5节8086微处理器的时序

- 格式:ppt

- 大小:829.00 KB

- 文档页数:25

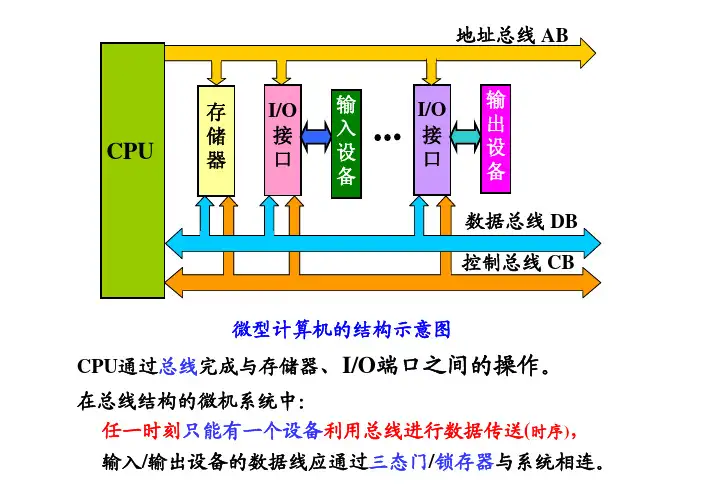

第五讲8086/8088微处理器引脚功能、总线结构和时序第一节、8086/8088引脚信号和功能第二节、8086/8088最小模式和最大模式第三节、8086/8088主要操作第四节、8086存储器的分体结构第一节8086/8088引脚信号和功能一、8086/8088的两种工作模式二、8086/8088引脚信号和功能一、8086/8088的两种工作模式8086/8088CPU有两种模式:最小模式和最大模式。

y最小模式系统中只有8086/8088一个微处理器(单处理器模式)。

所有的总线控制信号都直接由8086/8088产生。

总线控制逻辑电路被减少到最小。

适合于较小规模的系统。

y最大模式包含两个(以上)微处理器,其中一个主处理器是8086/8088,其他的处理器称为协处理器,协助主处理器工作。

适合于中等规模或大型的8086/8088系统中。

系统的控制总线由总线控制器8288来提供:¾8288增强了8088CPU总线的驱动能力;¾将8086的状态信号(S2~S0)进行译码,提供8086对存储器、I/O接口进行控制所需的信号。

最小模式与最大模式的主要区别8086/8088外部引脚图(括号内为最大模式时引脚名)8088地A14A13A12A11A10A9A8AD7AD6AD5AD4AD3AD2AD1AD0NMI INTR CLK 地Vcc(5V)A15A16/S3A17/S4A18/S5A19/S6SS0(HIGH)MN/MX RDHOLD(RQ/GT0)HLDA(RQ/GT1)WR(LOCK M/IO DT/R(S1)DEN(S0)ALE(QS0)INTA(QS1)TEST READY RESETVcc(5V)AD15A16/S3A17/S4A18/S5A19/S6BHE/S7MN/MX RDHOLD (RQ/GT0)HLDA (RQ/GT1)WR (LOCK)M/IO (S2)DT/R ( S1 )DEN (S0 )ALE (QS0)INTA (QS1)TEST READY RESET8086Vcc(5V)AD15A16/S3A17/S4A18/S5A19/S6BHE/S7MN/MX RDHOLD (RQ/GT0)HLDA (RQ/GT1)WR (LOCK)M/IO (S2)DT/R ( S1 )DEN (S0 )ALE (QS0)INTA (QS1)TEST READY RESET8086(1)地址/数据复用引脚(AD15~AD0 )是分时复用①在总线周期来输出要访问的存储器地址或口地址A15~A②在总线周期的其他时间内,作为双向数据总线:对8086就是(对8088地AD14AD13Vcc(5V)AD15A16/S3A17/S4A18/S5A19/S6BHE/S7MN/MXRDHOLD (RQ/GT0)HLDA (RQ/GT1)WR (LOCK)M/IO (S2)DT/R ( S1 )DEN (S0 )ALE (QS0)INTA (QS1)TESTREADYRESET8861.两种模式下公共引脚(2) 地址/状态复用引脚A19/S6~ A16/S3分时复用引脚,输出,三态。

第5章 8086的总线操作和时序一、内容简介:1 概述2 8086的两种工作模式3最小模式下8086的时序4 最大模式下8086的时序二、教学目标:了解8086/8088微处理器总线操作时序的分析方法。

三、重点内容:两种工作模式的时序分析。

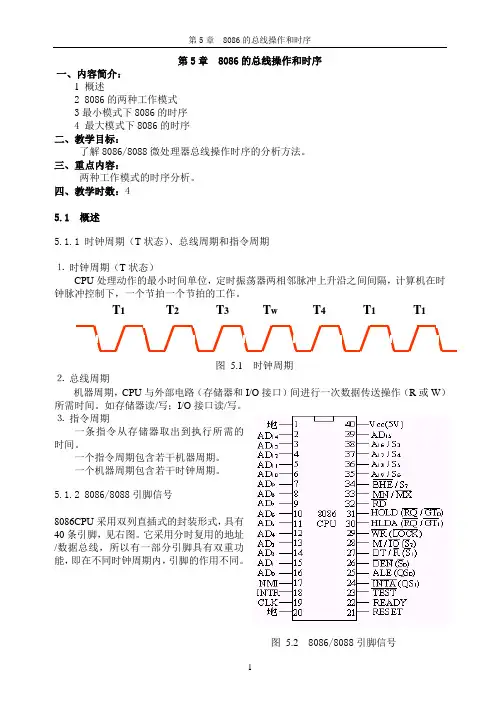

四、教学时数:45.1 概述5.1.1 时钟周期(T 状态)、总线周期和指令周期⒈ 时钟周期(T 状态)CPU 处理动作的最小时间单位,定时振荡器两相邻脉冲上升沿之间间隔,计算机在时钟脉冲控制下,一个节拍一个节拍的工作。

图 5.1 时钟周期⒉ 总线周期机器周期,CPU 与外部电路(存储器和I/O 接口)间进行一次数据传送操作(R 或W )所需时间。

如存储器读/写;I/O 接口读/写。

⒊ 指令周期一条指令从存储器取出到执行所需的时间。

一个指令周期包含若干机器周期。

一个机器周期包含若干时钟周期。

5.1.2 8086/8088引脚信号8086CPU 采用双列直插式的封装形式,具有40条引脚,见右图。

它采用分时复用的地址/数据总线,所以有一部分引脚具有双重功能,即在不同时钟周期内,引脚的作用不同。

图 5.2 8086/8088引脚信号T 1 T 2 T 3 T w T 4 T 1 T 15.2 8086的两种工作模式5.2.1 最小和最大工作模式1.最小工作模式由图5-3可知,在8086的最小模式中,硬件连接上有如下几个特点:(1)MN/MX端接+5V,决定了8086工作在最小模式。

(2)有一片8234A,作为时钟发生器。

(3)有三片8282或74LS373,用来作为地址锁存器。

(4)当系统中所连接的存储器和外设比较多时,需要增加系统数据总线的驱动能力,这时,可选用两片8286或74LS245作为总线收发器。

图5-3 8086的最小工作模式2.最大工作模式由图5-4可知,最大模式配置和最小模式配置有一个主要的差别:最大模式下多了8288总线控制器。

5.2.2 8086CPU引脚AD7~AD0(输入/输出,三态)这些地址/数据引线是多路开关的输出。

8086CPU系统总线操作和时序8086是一种16位的微处理器,由Intel公司于1978年推出。

8086CPU系统包括CPU、寄存器、输入输出模块、内存和总线等组成部分。

总线操作是指CPU与其他设备之间进行数据传输和通信的过程。

时序则是指这些操作所需要的时间和顺序。

一、8086CPU系统1.CPU:8086CPU是一种8MHz的16位微处理器。

它由一个运算器组件、一个控制器、一个时钟和一组寄存器组成。

运算器执行算术和逻辑操作,控制器控制这些操作的顺序和时机。

2.寄存器:8086CPU有14个寄存器,其中分为通用寄存器、段寄存器和指令寄存器。

-通用寄存器:8086有4个16位的通用寄存器,分别为AX、BX、CX和DX。

这些寄存器可以在运算和数据传输中使用。

-段寄存器:8086有4个16位的段寄存器,分别为CS、DS、SS和ES。

这些寄存器存储了内存中一些段的基地址。

-指令寄存器:8086有两个16位的指令寄存器IP和FLAGS。

IP存储下一个要执行的指令地址,FLAGS用于存储CPU运行时的状态标志。

3.输入输出模块:8086CPU通过输入输出模块与外部设备进行通信。

这些模块包括接口芯片、串行和并行接口等。

通过这些模块,CPU可以读取外部设备的数据,或者向外部设备发送数据。

4.内存:8086CPU可以访问1MB的内存空间。

内存被分为若干个64KB 的段,每个段都有一个唯一的段选择符和一个基地址。

8086使用分段的寻址方式来访问内存。

二、总线操作总线操作是指CPU与其他设备之间进行数据传输和通信的过程。

8086CPU有三个主要的总线:地址总线、数据总线和控制总线。

1.地址总线:8086有20根地址总线,可以寻址1MB的内存空间。

地址总线用于指示内存中读取或写入数据的地址。

2.数据总线:8086有16根数据总线,用于数据的传输。

数据总线可以同时传输一个16位的数据。

3.控制总线:8086有四根控制总线,分别为读(RD)、写(WR)、I/O(I/O)和时钟(CLK)。