引言

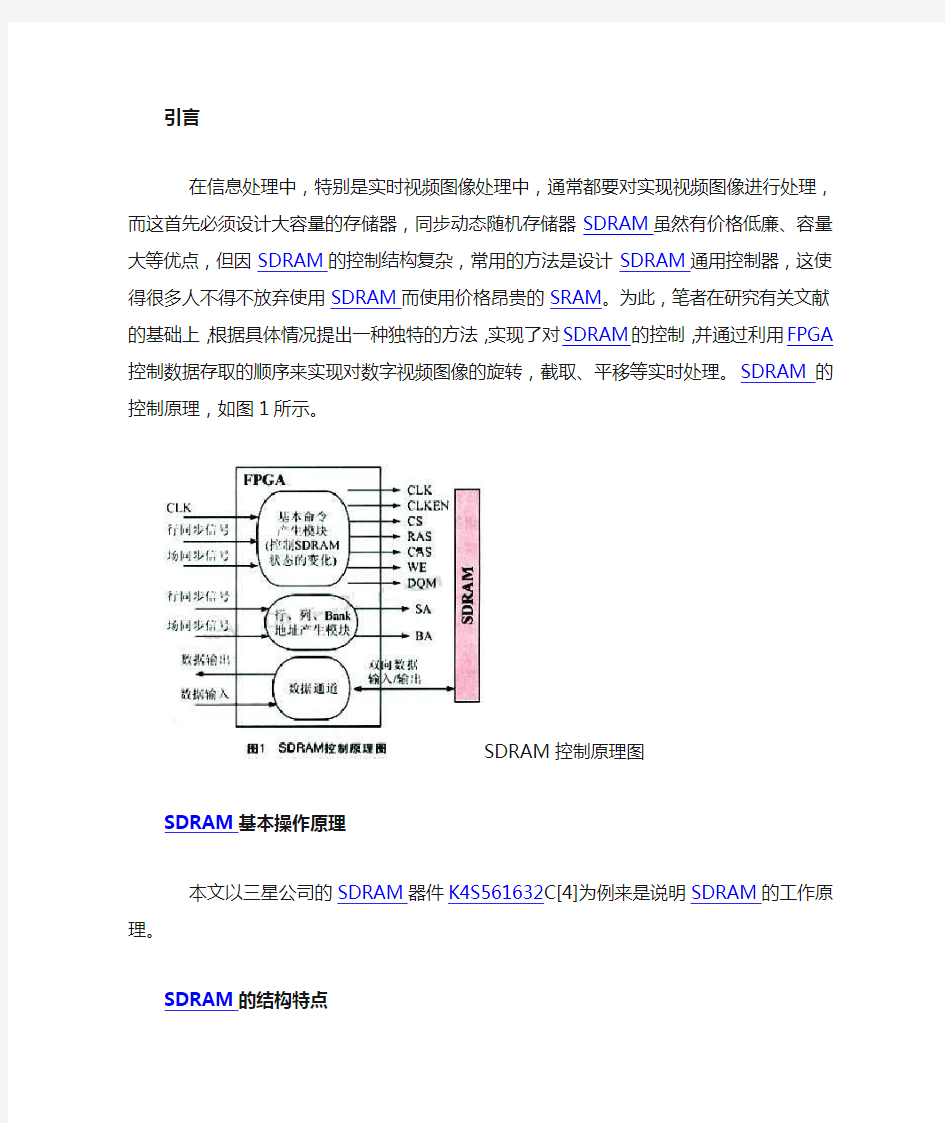

在信息处理中,特别是实时视频图像处理中,通常都要对实现视频图像进行处理,而这首先必须设计大容量的存储器,同步动态随机存储器SDRAM虽然有价格低廉、容量大等优点,但因SDRAM的控制结构复杂,常用的方法是设计SDRAM通用控制器,这使得很多人不得不放弃使用SDRAM而使用价格昂贵的SRAM。为此,笔者在研究有关文献的基础上,根据具体情况提出一种独特的方法,实现了对SDRAM的控制,并通过利用FPGA控制数据存取的顺序来实现对数字视频图像的旋转,截取、平移等实时处理。SDRAM的控制原理,如图1所示。

SDRAM控制原理图

SDRAM基本操作原理

本文以三星公司的SDRAM器件K4S561632C[4]为例来是说明SDRAM的工作原理。

SDRAM的结构特点

存储器的最初结构为线性,它在任何时刻,地址线中都只能有一位有效。设容量为N×M 的存储器有S0-Sn-1条地址线;当容量增大时,地址选择线的条数也要线性增多,利用地址译码虽然可有效地减少地址选择线的条数,但这种存储器的长宽比太大,显然,这在工业上是无法实现的。而且由于连线的延时与连线的长度成正比,这样的设计会使存储器的存取速度很慢。为了解决这个问题,现在常用的存储器都是将存储单元设计成阵列形状,使其长宽比接近1:1。这样,电路就必须增加一个列地址译码器,才能选出正确的存储单元。这样,整个存储器的地址线被分为行地址线和列地址线,行地址线要将要选择执行读或写操作的行,而列地址线则可从被选中的一行中再选出一个用于真正执行读或写操作的存储单元。

SDRAM的行地址线和列地址线是分时复用的,即地址线要分两次送出,先送行地址线,再送列地址线。这样可进一步减少地址线的数量、提高器件的性能,但寻址过程会由此变得复杂,新型的SDRAM的容量一般比较大,如果还采用简单的阵列结构,就会使存储器的字线和位线的长度、内部寄生电容及寄生电阻都变得很大,从而使整个存储器的存取速度严重下降,实际上,现在SDRAM一般都以Bank(存储体或存储块)为组织,来将SDRAM分为很多独立的小块,然而由Bank地址线BA控制Bank之间的选择;SDRAM的行、列地址线贯穿所有的Bank;每个Bank的数据位宽同整个存储器的相同。这样,Bank内的字线和位线的

长度就可被限制合适的范围内,从而加快存储器单元的存取速度,另外,BA也可以使被选中的Bank处于正常工作模式,而使没有被选中的Bank工作在低功耗模式下,这样还可以降低SDRAM的功耗。

为了减少MOS管的数量、降低功耗、提高集成度和存储容量,SDRAM都是利用其内部电容存储信息,由于电容的放电作用,必须每隔一段时间给电容充电才能使存储在电容里的数据信息不丢失,这就是刷新过程,这种机制使SDRAM的控制过程变的更加复杂,从而给应用带来难度。

三星公司的SDRAM(K4S561632C)的外部同步时钟速率可在一定的频率范围内连续变化,最高频率可达到133MHz,每块SDRAM内含四个独立的Bank;它的基本存储单元都是按照阵列排列的,它的数据位宽和整个存储器的位宽相同,同时支持多种读写模式;所有的输入信号均以时钟的上升沿为基准,这使得地址、控制和数据输入到缓冲器的时间可保持一致且建立和保持的时间很小;该器件使用完全流水线型内部结构;另外,它还具有突发长度可编程、延迟可编程等优点。这些优点使得K4S561632C能广泛的应用于宽频带、高性能存储器应用系统。

SDRAM的基本信号

SDRAM的基本信号可以分成以下几类:

(1)控制信号:包括片选(CS)、同步时钟(CLK)、时钟有效(CLKEN)、读写选择(WE)、数据有效(DQM)等;

(2)地址选择信号:包括行地址选择(RAS)、列地址选择(CAS)、行/列地址线(SA0-SA12)分时复用、Bank块地址线(BA0-BA1);

(3)数据信号:包括双向数据端口(DQ0-DQ15)、接收数据有效信号(DQM)控制等。DQM为低时,写入/读出有效。

对SDRAM的基本命令

要正确的对SDRAM进行操作,就需要输入多种命令:包括模式寄存器设置、预充电、突发停止、空操作等命令。SDRAM内部的状态会根据表1的命令进行转移,其中,命令COM ={CS#;RAS#;CAS#;WE#}。

模式寄存器的规定

利用模式寄存器(Mode Register)[5]可通过装载模式寄存器命令(LOADMODE REGISTER)进行编程,这组信息将会一直保存在模式寄存器中,直到它再次被编程或器件掉电为止;它规定了SDRAM的操作模式,包括突发长度、突发类型、CAS延迟时间、运行模式及写突发模式、具体格式如图2所示,模式寄存器M0-M2用于规定突发长度(Burst LENGTH)。M3用于规定突发类型BT(Burst TYPE),M3=0时,突发类型是连续的;M3=1时,突发类型是交错的,M4-M6用于规定CAS延迟的时钟周期数,M7-M8规定运行模式,M9规定写突发模式WB(Write Burst Mode),当M9=0时,按实际编程的突发长度存取,当M9=1时,则按单个存取单元写入,但可按实际编程的突发长度读出,M10和M11为保留位,可供未来使用。在模式寄存器装载期间,地址A12(M12)必须被驱动至低电平,本方案中,模式寄存器的值为ox220h。

初始化操作

SDRAM在上电以后必须先对其进行初始化操作,而后才能对其进行其他操作。出初始化操作具体步骤如下:

(1)SDRAM在上电以后需要等待100-200μs,在等待时间结束后还至少要执行一条空操作命令;

(2)SDRAM执行一条预充电命令后,要执行一条空操作命令,这两个操作会使所有的存储单元进行一次预充电,从而使所有阵列中的器件处于待机状态;

(3)SDRAM要执行两条自刷新命令,每一条刷新命令之后,都要执行一条空操作命令,这些操作可使SDRAM芯片内部的刷新及计数器进入正常运行状态,以便SDRAM为模式寄存器编程做好准备;

(4)执行加载模式寄存器(LOAD MODE REGISTER)命令,完成对SDRAM工作模式的设定。完成以上步骤后,SDRAM即可进入正常工作状态,以等待外部命令对其进行读、写、预充电和刷新等操作。

SDRAM的基本读写操作

SDRAM的基本读操作[3]需要控制线和地址线相配合并发出一系列命令来完成。SDRAM 的读操作只有突发模式(Burst Mode);而写操作则可以有突发写和非突发写两种模式,具体如下:

(1)带有预充电的突发读写模式,该模式一次能够访问的列地址的最大数为1、2、4、8;

(2)不带有机充电的全页读写、此模式可任意控制一次能够访问的列地址的最大数。根据实际情况,本设计只选取了与本方法相关的基本操作命令,并没有设计通用的控制器,图3是本方案的SDRAM内部状态转移图。

SDRAM内部状态转移图

Bank乒乓操作

由于Bank内的行与行之间具有关联性,因此,当其中一个Bank的读或写操作结束后,必须执行一次预充电命令以关闭正在操作的行、预充电命令执行后,会有一个tRP的延时,延时完成后才能向同一Bank行(或其他行)发出新的激活命令。由于Bank 之间是相互独立的,因此,在一个Bank进行正常的读或写操作时,可以对另外几个Bank进行预充电或空操作;当一个Bank的进行预充电期间也可以直接调用另一个已经进行预充电的Bank,而并不需要等待,具体的Bank控制过程要参考特定的器件数据手册。三星公司的K4S561632内的Bank控制状态如图2所列。

常用的三种寻址方式

K4S561632C器件的常用寻址方法有以下三种:

(1)页命令中PH(Page Hit):若寻址的行与所在的Bank的空闲的,即该Bank内所有的行是关闭的,那么此时便可直接发送行有效命令,这种情况下,数据读取前的总耗时为tRCD+CL;(tRCD为RAS到CAS的延时;CL为CAS latency)。

(2)页快速命中PFH(Page FAST Hit)或页直接命中PDH(Page Direct Hit):如果要寻址的行正好是在正常读或写,即要寻址的行正处于被选通的有效状态,那么此时可直接发送列寻址命令,这种情况下,数据读取前的总耗时仅为CL,这就是所谓的背靠背(BACK to BACK)寻址;

(3)页错失PM(Bage Miss):若要寻址的行所在的Bank中已经有一个行处于激活状态(未关闭),这种现象而称为寻址冲突,这样,就必须要进行预充电来关闭正在工作的行、然后再对其他的行发送行有效命令,其总耗时为:tRP+tRCD+CL。(tRP为Row precharge time)。

在以上三种寻址方式中,PFH是最理想的寻址方式,PM则是最糟糕的寻址方式,实际应用中要尽量采用PFH寻址方式而应避免采用PM寻址方式。

减少延迟的方法

自动预充电技术是一种有效的减少延迟的方法,它通过自动在每次行操作之后进行预充电操作来减少对同一Bank内的不同行寻址时发生冲突的可能性,但是,如果要在正在读或写的行完成操作后马上打开同一Bank的另一行时,仍然存在tRP的延迟。交错式控制是另一种更有效的减少延迟的方法,即在一个Bank工作时,对另一个Bank进行预充电或者寻址(此时要寻址的Bank是关闭的),预充电与数据的传输交错执行,当访问下一个Bank时,tRP已过,这样就可以直接进入行有效状态,如果配合得比较理想,那么就可以实现无间隔的Bank交错读或写,因此,Bank之间的切换可使存储效率成倍提高,并能够大大地提高多组SDRAM协同工作时的性能。

Bank乒乓操作写入

一个由行、场同步信号控制的计数器在预定的时刻会产生一个控制信号,先发出激活相应Bank的激活命令(ACTIVE),并锁存相应的Bank地址(由BA0、BA1给出)和行地址(由A0-A12给出)。一个周期后再给出列地址和写入命令;在CL个周期后,便可将所需写入的数据依次送到数据总线上,当计数器的计数周期到达时,系统会产生一个控制信号,并向SDRAM发送预充电(PRECHARGE)命令(如果使用了可编程长度,则在这前要使用突发终止命令),以关闭已经激活的页。在下一个视频行同步信号来临时,系统将重复以上操作,并如此循环下去,具体操作如图4所示,图中左边的一、二、三……为所对应的视频行同步信号,右边1至511……则代表对应的存储器中的列地址(即是屏幕上对应的像素的位置)。

Bank乒乓操作读出

由行、场同步信号控制的一个计数器可在预定的时刻产生一个控制信号,它首先发出相应的Bank激活命令(ACTIVE),并锁存相应的Bank地址(由BA0、BA1给出)和行地址(由A0-A12)给出,然后在一个周期后给出列地址和读命令,当计数器的计数周期到达时,系统会产生一个控制信号,并向SDRAM

发出预充电(PRECHARGE)命令,以关闭已经激活的页(如果使用了可编程长度,则在这之前要使用突发终止命令)。之后,再在下一个视频行同步信号来临时重复以上操作,如此循环(具体操作如图5),图中左边的一、二、三……为所对应的视频行同步信号,右边1至511……代表对应的存储器中的列地址(即是屏幕上对应的像素的位置。

场乒乓操作

为了SDRAM能正确进行读和写两个操作,本方案选用两场乒乓操作[6]来实现数据存取,实际上,就是在不同的时间对两场轮换进行读或写,一场读而另一场写,其原理如图6所示。当开关K1在1位置,K2在4位置是时,A写B读;反之,当开关K1在3位置,K2在2位位置时,A读B写。如此循环往复。

若以场同步信号的二分频计数器F/2为读写控制信号,假设SDRAM A在F/2时为1写、2读,则SDRAM B在F/2时为2写、1读,两场即为一个场乒乓操作周期,读写信号均在场同步信号为高电平时有效,由于存在消隐期,消音所以,将会有一段时间读写都无效(读写信号都是低电平,此时SDRAM进入预充电状态),其总体时序如图7所示。

结束语

SDRAM的控制过程虽然很复杂,但如果根据实际情况进行取舍以满足实际系统要求,那么,SDRAM的控制过程还是比较简单的,在实验中,使用ALTERA 公司的Cyclone FPGA器件进行设计时,程序设计可采用Verilog语句来实现对实时视频信号的采集,并通过改变计数器的周期及SDRAM的行、列地址线和时序就可以对任意位置的视频图像进行平移、旋转、截取等处理,此外,由于程序设计采用了化整为零和参数化设计思想,因而结构透明、简单;对于特定容量的SDRAM的特定工作模式而言,该方法只需根据器件重新设定参数而不要重新编写程序,因而具有较强的通用性。

全面教你认识内存参数 内存热点 Jany 2010-4-28

内存这样小小的一个硬件,却是PC系统中最必不可少的重要部件之一。而对于入门用户来说,可能从内存的类型、工作频率、接口类型这些简单的参数的印象都可能很模糊的,而对更深入的各项内存时序小参数就更摸不着头脑了。而对于进阶玩家来说,内存的一些具体的细小参数设置则足以影响到整套系统的超频效果和最终性能表现。如果不想当菜鸟的话,虽然不一定要把各种参数规格一一背熟,但起码有一个基本的认识,等真正需要用到的时候,查起来也不会毫无概念。 内存种类 目前,桌面平台所采用的内存主要为DDR 1、DDR 2和DDR 3三种,其中DDR1内存已经基本上被淘汰,而DDR2和DDR3是目前的主流。 DDR1内存 第一代DDR内存 DDR SDRAM 是 Double Data Rate SDRAM的缩写,是双倍速率同步动态随机存储器的意思。DDR内存是在SDRAM内存基础上发展而来的,仍然沿用SDRAM生产体系,因此对于内存厂商而言,只需对制造普通SDRAM 的设备稍加改进,即可实现DDR内存的生产,可有效的降低成本。 DDR2内存 第二代DDR内存

DDR2 是 DDR SDRAM 内存的第二代产品。它在 DDR 内存技术的基础上加以改进,从而其传输速度更快(可达800MHZ ),耗电量更低,散热性能更优良。 DDR3内存 第三代DDR内存 DDR3相比起DDR2有更低的工作电压,从DDR2的1.8V降落到1.5V,性能更好更为省电;DDR2的4bit 预读升级为8bit预读。DDR3目前最高能够1600Mhz的速度,由于目前最为快速的DDR2内存速度已经提升到800Mhz/1066Mhz的速度,因而首批DDR3内存模组将会从1333Mhz的起跳。 三种类型DDR内存之间,从内存控制器到内存插槽都互不兼容。即使是一些在同时支持两种类型内存的Combo主板上,两种规格的内存也不能同时工作,只能使用其中一种内存。 内存SPD芯片 内存SPD芯片

浅谈对项目领导副职工作的认识 当前,国内宏观经济形势回升向好,经济趋于平稳。但经济层面中一些深层次的矛盾和问题仍十分突出,施工企业面临的外部环境仍然充满了许多不确定因素,交通建筑市场,尤其是公路市场未来几年的发展方向主要是以加密、扩建等公路建设为主。加之,传统公路市场增速继续放缓,市场开发形势更为严峻,竞争将更加激烈。对此,如何做好现有项目生产管理工作,进一步巩固企业的市场地位,着力彰显企业品牌实力,深入实施“管理保现场,现场拓市场”的经营开发理念已成为各大施工企业的管理的重点。 作为建筑企业的窗口---项目经理部,在企业发展之中起着重要的支撑作用。做好项目管理工作的重要性与重要意义更是不言而喻。然而,如何做好项目管理工作,人是第一要素,在此本人就以项目管理中副职领导应如何做好自身定位,如何做好自己本职工作浅谈以下几点意见,以供大家借鉴。 一、项目副职工作应做到“到位而不越位” 首先要“到位”。对如何解决自己分管工作中的棘手问题,要有自己的主见,尽量自己处理,不能独立处理的,要积极主动地为项目一把手出主意、想办法、提方案,而不能唯唯诺诺,四平八稳,正职说什么是什么,叫咋干就咋干,这不是到位而是“空位”。同时,副职也注意不要“越位”,对未经项目正职授权的自己职权范围之外的工作,不能越权随意表态,以免造成被动。

二、项目副职工作应做到“辛苦不诉苦” 一个称职的项目副职要想做好分管的具体工作,做出突出的政绩,必须全身心地投入工作,是十分辛苦的。这个时候可以认真总结成功的经验和存在的败笔,并向正职汇报,但特别注意不要在正职面前诉苦,尤其在工作进行过程中,如果老是强调工作有难度,推进不容易,不但不会给项目正职留下你工作不遗余力的正面印象,反而会造成干工作力不从心的不良印象。 三、项目副职工作应做到“有功不争功” 工作有了成绩,切忌骄傲自满,忘乎所以。项目副职在功劳面前应该淡泊名利,保持低调,要注意把正职往前台推。如果在取得成绩的同时,又存在失误,要敢于承担责任,多做自我批评,做到在成绩面前荣辱不惊、物我两忘,而绝不能自视过高,搞喧宾夺主、功高盖主那一套,引起项目正职的反感和同事们的非议,那损失就太大了。 四、项目副职工作应做到“补台不拆台” 项目领导班子是一个整体,实际上是一荣俱荣,一损俱损的关系。因此,要注意自觉维护领导班子的形象,强化领导集体的权威,作为副职特别要注意树立一把手的威信。当一把手决策失误时,要敢于如实反映职工的意见、要求和呼声,帮一把手出主意、想办法纠正,关键时刻甚至要挺身而出,替一把手遮风挡雨,既不能站在旁边看笑话,也不能一味投一把手所好,歪曲事实,曲意逢承。

SDRAM内存详解(经典) 我们从内存颗粒、内存槽位接口、主板和内存之间的信号、接口几个方面来详细阐述SDRAM内存条和主板内存系统的设计思路... 虽然目前SDRAM内存条价格已经接底线,内存开始向DDR和Rambus内存过渡。但是由于DDR内存是在SDRAM基础上发展起来的,所以详细了解SDRAM内存的接口和主板设计方法对于设计基于DDR内存的主板不无裨益。下面我们就从内存颗粒、内存槽位接口、主板和内存之间的信号接口几个方面来详细阐述SDRAM内存条和主板内存系统的设计思路。 内存颗粒介绍 对于DRAM(Dynamic Random Access Memory)内存我想凡是对于计算机有所了解的读者都不会陌生。这种类型的内存都是以一个电容是否充有电荷来作为存储状态的标志,电容冲有电荷为状态1,电容没有电荷为状态0。其最大优点是集成度高,容量大,但是其速度相对于SRAM (Static Random Access Memory) 内存来说慢了许多。目前的内存颗粒封装方式有许多种,本文仅仅以大家常见的TSSOP封装的内存颗粒为例子。 其各个管脚的信号定义和我们所使用的DIMM插槽的定义是相同的,对于不同容量的内存,地址信号的位数有所不同。另外一个需要注意的地方就是其供电电路。Vcc和Vss是为内存颗粒中的存储队列供电,而VccQ和VssQ是为内存颗粒中的地址和数据缓冲区供电。两者的作用不同。 我们对内存颗粒关心的问题主要是其颗粒的数据宽度(数据位数)和容量(寻址空间大小)。而对于颗粒自检、颗粒自刷新等等逻辑并不需要特别深入的研究,所以对此我仅仅是一笔带过,如果读者有兴趣的读者可以详细研究内存颗粒的数据手册。虽然内存颗粒有这么多的逻辑命令方式,但是由于目前北桥芯片和内存颗粒的集成度非常高,只要在布线和元器件的选择上严格按照内存规范来设计和制造,需要使用逻辑分析仪来调试电路上的差错的情况比较少,并且在设计过程中尽量避免出现这种情况。 168线DIMM内存插槽的信号定义 我们目前PC和Server使用的内存大都是168 Pins的SDRAM,区别只是其工作频率有的可能是100MHz频率,有的可能是133MHz频率的。但是只要是SDRAM,其DIMM插槽的信号定义是一样的。而这些引脚得定义就是设计内存条和主板所必须遵从的规范。 内存引脚主要分为如下几类:地址引脚、数据引脚(包含校验位引脚)、片选等控制信号、时钟信号。整个内存时序系统就是这些引脚上的信号配合产生。下面的表中就是内存插槽的引脚数量和引脚定义,对于一些没有定义或者是保留以后使用的信号就没有列出来。 符号功能详细描述 DQ [0-63] I/O 数据输入/输出 CB [0-7] I/O ECC内存的ECC校验输入/输出 A [0-13] I/O 地址选择 BA [0-1] Control Bank选择 CS [0-3] Control 片选信号 RAS Control 行地址选择信号 CAS Control 列地址选择信号 DQMB [0-7] Control 数据掩码控制(DQ Mask)高有效* WE Control 写允许信号 CK [0-3] Clock 时钟信号 CKE [0-1] Clock 时钟允许信号** REGE Control 寄存器 (Registered) 允许信号

《浅谈领导者应该具备的气质》 ——领导科学与艺术论文摘要:从我自己简单有限的阅读一些领导学方面的书籍来谈谈我对于领导应该具备怎样的几点主要的气质。采用论述与实例并存的方法来简单的论述,这其中难免会有片面的理解,望老师改正。 关键词:领导者气质自信大度细心果断 作为一个领导者,虽然同样都是人,同样都在一个工作楼里面办公,虽然现在强调的是众生平等,但是领导者,毕竟还是不一样的人。领导者具有作出决策的作用,如果起不了决策引导众人的作用,那么领导只能说是“平庸”。而在人力资源管理中,有一句名言,没有“平庸的人”,只有“平庸的管理”。如果一个团队被管理得很平庸,领导者也很平庸,那么在如今这个竞争激烈的社会中,难免就会出现弱肉强食、垄断兼并倒闭的现象。那么,在我看来,领导者最起码需要具备几点基本的气质,才可以保障在这个团队中他不是“平庸的管理”。 1.自信。领导者的决策作用至关重要,如果你不自信,做事情唯唯诺诺,将会使你的团队对你自己本身的决策以及你的能力产生怀疑,不利于团队核心的建设以及未来的长远发展。我记得之前看过一期《职来职往》,其中某家企业的执行总裁问一个到访应聘者:“我们现在的公司是一家上市了的酸奶公司。如果有一天我对你说给你率领的部门一种研发的沐浴露让你进行推广和销售,你和你的团队会怎么办?”那个人很紧张,更是被这种问题问的不知所措,我当时想的也

是,你们公司既然是做食品方面的,为什么跨行改去生产沐浴露了呢。那个人支支吾吾说可以让他一边洗澡一边喝酸奶,全场哄堂大笑,那个总裁也笑了,然后笑着说:“何必呢,如果我是你,那么我们部门何必要选择推销公司的沐浴露呢,我宁可把它直接转手卖给卖浴缸的啊!你记住,你作为领导者,一定要时刻保持清醒的头脑清楚你们要的是什么不要的是什么,你是领导者,你有自己的权利决定。虽然我知道你现在一定很紧张,大脑没办法运转也没办法决定~(笑)。” 我想这个小例子就告诉我们领导者的决策权不是白给的,我们要利用它,同时要大胆的有自信的利用它,当然,也不能毫无根据,凭借自己的喜好,领导者的自信要来源于他自己的知识与理性。自信并不等于盲目、骄傲、唯我独尊。 2.大度。尽管在课堂上,老师告诉过我们领导者是有很多种类型的,其中不乏一些大的成功的公司他们的领导者是居高临下、不容侵犯,在团队的面前感觉是很不好接触的人,但是我个人认为,领导者固然要有一些威严存在,然而更多时间应该还是微笑大度的吧。人力资源管理的老师讲“多笑一笑又有什么损失呢,你走在大街上没事的时候冲那些陌生人笑一笑,也许就能够拯救一个人曾经想要自杀的想法。”既然领导者嬉皮笑脸做不到,那么我们就多对我们的员工微笑吧!大度就以为着为整个团队默默的营造了一个和谐宽松的环境。俗话说的好:你愿意别人怎样对待你,你也应该那样去对待别人。你作为领导者,既然把他带进了这个团队就意味着你很相信他,所以你必须相信每个人都有专长,必须使别人感到他自己很重要。当然,每个人都会

举例9-9-9-27,一般1600的条子spd出厂就这么设置的 前面2个9对性能很重要,第2个9又比第1个9重要,比如说 我要超1866或者2133,设置成9-10-X-X基本没有问题,但是 设置成10-9-X-X就开不了机了,很多条子都这样子的,比如说 现在很火的3星金条。 第3位9基本上是打酱油的了,设置成9,10,11都对性能木有太大影响。 第4位数字基本就无视好了,设置21-36对测试都没变化,原来稳定的 还是稳定,原来开不了机的还是开不了。 以前的ddr2时代对内存的小参数很有影响,现在ddr3了,频率才是王道哦。 2133的-11-11-11-30都要比1866的-9-9-9-27测试跑分的多。当然平时用是感觉不出来的。 最后我再鄙视下金士顿的XX神条马甲套装,当年不懂事大价钱买的,就是YY用的, 1.65v上个1866都吃力,还要参数放的烂。 对性能影响最大的是CL 第一个9对性能影响最大。l第二个9对超频稳定性影响最大 最普通的ddr3 1333内存都可以1.5V运行在7-8-6-1666 CR1,77 Z博士: 一般来说,体现内存延迟的就是我们通常说的时序,如DDR2-800内存的标准时序:5-5-5-18,但DDR3-800内存的标准时序则达到了6-6-6-

15、DDR3-1066为7-7-7- 20、而DDR3-1333更是达到了9-9-9-25! 土老冒: 俺想知道博士所说的5-5-5- 18、6-6-6-15等数字每一个都代表什么。 Z博士: 这4个数字的含义依次为: CAS Latency(简称CL值)内存CAS延迟时间,这也是内存最重要的参数之一,一般来说内存厂商都会将CL值印在产品标签上。 第二个数字是RAS-to-CAS Delay(tRCD),代表内存行地址传输到列地址的延迟时间。 第三个则是Row-precharge Delay(tRP),代表内存行地址选通脉冲预充电时间。 第四个数字则是Row-active Delay(tRAS),代表内存行地址选通延迟。 除了这四个以外,在AMD K8处理器平台和部分非Intel设计的对应Intel芯片组上,如NVIDIA nForce 680i SLI芯片组上,还支持内存的CMD 1T/2T Timing 调节,CMD调节对内存的性能影响也很大,其重要性可以和CL相比。 其实这些参数,你记得太清楚也没有太大用处,你就只需要了解,这几个参数越低,从你点菜到上菜的时间就越快。 土老冒: 好吧,俺自己也听得一头雾水,只需要记得它越低越好就行了。那么俺想问,为什么DDR3内存延迟提高了那么多,Intel和众多的内存模组厂商还要大力推广呢?

8086CPU系统、总线操作和时序 第一节 8086的引脚信号与功能 回顾:8086/8088微型计算机的组成、结构及微机系统的工作过程,微机系统的存储器组织及相关概念。 本讲重点:8086/8088CPU的两种工作模式,8086/8088CPU的外部结构,即引脚信号及其功能。 讲授内容: 一、 8086/8088微处理器工作模式及外部结构 1.8086/8088CPU的两种工作模式 为了适应各种使用场合,在设计8088/8086CPU芯片时,就考虑了其应能够使它工作在两种模式下,即最小模式与最大模式。 所谓最小模式,就是系统中只有一个8088/8086微处理器,在这种情况下,所有的总线控制信号,都是直接由8088/8086CPU产生的,系统中的总线控制逻辑电路被减到最少,该模式适用于规模较小的微机应用系统。 最大模式是相对于最小模式而言的,最大模式用在中、大规模的微机应用系统中,在最大模式下,系统中至少包含两个微处理器,其中一个为主处理器,即8086/8086CPU,其它的微处理器称之为协处理器,它们是协助主处理器工作的。 与8088/8086CPU配合工作的协处理器有两类,一类是数值协处理器8087 另一类是输入/输出协处理器8089。 8087是一种专用于数值运算的协处理器,它能实现多种类型的数值运算,如高精度的整型和浮点型数值运算,超越函数(三角函数、对数函数)的计算等,这些运算若用软件的方法来实现,将耗费大量的机器时间。换句话说,引入了8087协处理器,就是把软件功能硬件化,可以大大提高主处理器的运行速度。 8089协处理器,在原理上有点像带有两个DMA通道的处理器,它有一套专门用于输入/输出操作的指令系统,但是8089又和DMA控制器不同,它可以直接为输入/输出设备服务,使主处理器不再承担这类工作。所以,在系统中增加8089协处理器之后,会明显提高主处理器的效率,尤其是在输入/输出操作比较频繁

4.1 OpenCV主要函数介绍 1) cvLoadImage 从文件中读取图像 IplImage* cvLoadImage(const char* filename,int flags=CV_LOAD_IMAGE_COLOR ); 函数cvLoadImage从指定文件读入图像,返回读入图像的指针。其中filename是要被读入的文件的文件名;flags指定读入图像的颜色和深度。 2)cvSaveImage 保存图像到文件 int cvSaveImage( const char* filename, const CvArr* image ); 函数cvSaveImage保存图像到指定文件。其中filename保存文件名。image 要保存的图像。图像格式的的选择依赖于filename的扩展名,只有8位单通道或者3通道(通道顺序为'BGR' )可以使用这个函数保存。 3)cvQueryFrame从摄像头或者文件中抓取并返回一帧 IplImage* cvQueryFrame( CvCapture* capture ); 函数cvQueryFrame从摄像头或者文件中抓取一帧,然后解压并返回这一帧。这个函数仅仅是函数cvGrabFrame和函数cvRetrieveFrame在一起调用的组合。返回的图像不可以被用户释放或者修改。其中capture视频获取结构。。 4)cvCaptureFromCAM 初始化摄像头 CvCapture* cvCaptureFromCAM( int index ); 函数cvCaptureFromCAM给从摄像头的视频流分配和初始化CvCapture结构。 其中index要使用的摄像头索引。如果只有一个摄像头或者用哪个摄像头也无所谓,那使用参数-1应该便可以。 5)cvHaarDetectObjects 用来检测图像中的人脸区域 CV API(CvSeq*) cvHaarDetectObjects( const CvArr* image, CvHaarClassifierCascade* cascade, CvMemStorage* storage, double scale_factor CV_DEFAULT(1.1), int min_neighbors CV_DEFAULT(3), int flags CV_DEFAULT(0), CvSize min_size CV_DEFAULT(cvSize(0,0)), CvSize max_size CV_DEFAULT(cvSize(0,0))); 用于快速检测人脸区域,便于提取得到人脸数据。其中image 为被检图像,cascade为 haar分类器级联的内部标识形式,storage 为用来存储检测到的一

浅谈领导者用人之道 领导,就是在社会共同活动中,具有影响力的个人或集体,在特定的结构中通过有效的途径,动员下属实现群体目标的过程。 领导活动存在于群体之中。组织领导工作的顺利开展要求领导者必须知人善任。《韩非子·八经》中讲“下君尽己之能,中君尽人之力,上君尽人之智”,对一名领导者来说,在他为实现政治路线而进行的组织领导工作中,首要的就是人才问题。因为不论是科学决策的执行,还是组织管理的实施和各项领导工作的进行,都离不开人才这个决定因素。作为一名领导者,他不可能掌握现代化生产的一切科学技术知识,不可能面对复杂多变的情况,包揽各种巨细事物,不可能事事亲自动手干。毛泽东同志曾明确指出,领导者的责任除了“出主意”之外,就是“用干部”。任何一项组织领导活动的顺利开展,都离不开领导者能否有效地调动每个人的积极性,充分发挥他们的主观能动性。 一、领导者要人尽其才,整合组织中各成员的长处共同实现群体目标 汉高祖刘邦曾说:“夫运筹策帷帐之中,决胜于千里之外,吾不如子房。镇国家,抚百姓,给馈饷,不绝粮道,吾不如萧何。连百万之军,战必胜,攻必取,吾不如韩信。此三者,皆人杰也,吾能用之,此吾所以取天下也。”刘邦之所以能够战胜项羽,汉高祖刘邦能胜楚霸王项羽,主要依靠萧何、韩信、陈平等贤人智士的辅佐;蜀主刘备能与东吴孙权、魏国曹操成三国鼎立之势,因为他有诸葛亮出谋划策,有结拜兄弟关、张二将力战沙场;唐太宗李世民能御敌寇于境外,兴华夏于乱世,因为他虚怀若谷,“房谋

杜断”、魏征为镜,功臣个个出类拔萃。以上这些任人惟贤、人尽其才、不避亲仇的做法,对领导干部来说很有借鉴意义。 正所谓天生我才必有用。因此,我们要坚持任人唯贤、德才兼备、群众公认、注重实绩等原则,选拔那些政治上靠得住、工作上有本事、作风上过得硬、人民群众信得过的领导人才,为地区经济社会发展提供坚强的组织保证和人才支持。此外,干部选任原则和标准是一个有机整体,必须全面、准确地理解每项原则的深刻内涵,并从整体上去把握,真正做到智者用其谋、愚者用其力、勇者用其威、怯者用其慎,使干部的专长得到最大限度的发挥。比如,在班子的配备上,我们既要注重班子成员年龄、知识、专业等方面的科学统筹,也要注重成员气质、性格和潜能的优势互补,形成专业上互补、性格上默契、个性上相容,实现最佳组合。 “为政之要,惟在得人”。我们应在借鉴古人智慧的基础上,科学地解决人尽其才的问题。金无足赤,人无完人;良匠无弃木,明主无弃士。在坚持德才兼备、以德为先选人用人标准的前提下,对某一方面有突出才能的干部,只要其缺点不是原则性的,就要果断地用到合适的岗位上,切勿因求全责备而错失良机。这需要我们综合比较、量化分析、整合盘活现有干部队伍,以科学的方式选对人、用好人,最大限度地实现“人岗相适、用当其时、人尽其才”,不断提高干部工作的科学化水平。 由于人是有自己的意志、思想和愿望的,这就要求领导者要根据自己的职责“运筹帷幄”、“调兵遣将”。要能够根据需要,人事相宜,选用得当,真正把每个人选用到合适的岗位上,使每个人都明确自己的职责,以及自己的工作与全局的关系和意义,才能使每个人积极主动、放心大胆地工作,真正做到各司其职,各尽其责,充分发挥每个人

D D R 系列系列内存内存内存详解及硬件详解及硬件 设计规范 By: Michael Oct 12, 2010 haolei@https://www.doczj.com/doc/e31953733.html,

目录 1.概述 (3) 2.DDR的基本原理 (3) 3.DDR SDRAM与SDRAM的不同 (5) 3.1差分时钟 (6) 3.2数据选取脉冲(DQS) (7) 3.3写入延迟 (9) 3.4突发长度与写入掩码 (10) 3.5延迟锁定回路(DLL) (10) 4.DDR-Ⅱ (12) 4.1DDR-Ⅱ内存结构 (13) 4.2DDR-Ⅱ的操作与时序设计 (15) 4.3DDR-Ⅱ封装技术 (19) 5.DDR-Ⅲ (21) 5.1DDR-Ⅲ技术概论 (21) 5.2DDR-Ⅲ内存的技术改进 (23) 6.内存模组 (26) 6.1内存模组的分类 (26) 6.2内存模组的技术分析 (28) 7.DDR 硬件设计规范 (34) 7.1电源设计 (34) 7.2时钟 (37) 7.3数据和DQS (38) 7.4地址和控制 (39) 7.5PCB布局注意事项 (40) 7.6PCB布线注意事项 (41) 7.7EMI问题 (42) 7.8测试方法 (42)

摘要: 本文介绍了DDR 系列SDRAM 的一些概念和难点,并分别对DDR-I/Ⅱ/Ⅲ的技术特点进行了论述,最后结合硬件设计提出一些参考设计规范。 关键字关键字::DDR, DDR, SDRAM SDRAM SDRAM, , , 内存模组内存模组内存模组, , , DQS DQS DQS, DLL, MRS, ODT , DLL, MRS, ODT , DLL, MRS, ODT Notes : Aug 30, 2010 – Added DDR III and the PCB layout specification - by Michael.Hao

管理学之领导职能的 认识

浅谈领导职能 摘要:纵向地分析组织管理的基本职能包括了计划职能、组织职能、领导职能、控制职能、创新职能。而领导职能是整个管理活动得以展开的手段,当今社会是人力资源竞争的社会,管理的各项活动不仅需要人来制定,更需要广大被管理者的执行。如何执行;如何有效地、更好地执行,都需要管理者发挥领导艺术,只有这样才能发挥组织的作用,才能将计划贯彻,才有可能实现既定的计划和组织目标。而如何去学会提升自身对领导能力的认识和运用也是当今社会我们必须要学会的,这有助于我们对管理更深的认识和体会。 关键词:含义相互关系领导与权力 一、领导职能的含义 领导,是指管理当局同别人一起或者通过别人去完成组织目标,也是一种影响力,是对人们施加影响的过程,从而使得人们为组织或者群体完成目标而努力。在当今拥有优秀的人才并不代表这些人才能各尽其力,如何设计合理的组织,让其各司其职,并使得每个成员以高昂的士气、饱满的热情投身到组织的活动中去,将其能力最大化的发挥,为组织创造更多的效益,这需要管理者运用一切可能的手段去与其沟通,对其进行有效激励,只有这样才能合理配置、使用人力资源,使其优点能为组织所用,缺点又不至于影响组织运作。再者要求管理人员在合理的制度环境中,利用优秀的素质,才用适当的方式,针对组织成员的需要和特点,采取一系列措施来提高和维持组织成员的工作积极性,这种能力便可以称为领导能力。 二、领导职能与其他职能的相互关系

总的来说管理的五个职能是相辅相成、相互影响、相互作用、相互交叉渗透的,缺一不可。每一个职能都有其重要的作用及价值,缺了任何一个要素,管理活动都是无法顺利进行、有序展开的。领导的职能是决策和控制;激励的功能离不开协调,否则激励的功能会失衡;组织的活动需要计划和控制,否则组织将没有效能。在管理过程中,前四个职能,即计划、组织、领导和控制是呈现出一个循环的状态,每一项管理活动都是从计划开始,经组织贯彻,领导沟通协调展开,最后对偏差及其成果进行控制结束的。而上一轮控制活动结束之后又引发新一轮的计划、组织……如此反复循环,生生不息。 三、领导与权力 领导是管理工作的一个重要职能。无论在任何社会中,一个国家也好、一个企业也,其兴衰成败都与领导水平的关系极为密切。权力对于领导是极为重要的,它是领导工作的基础,是领导者实现目标的手段。权力是组织中的一种无形的力量。虽然看不见它的存在,但它的影响却让你时时那人能够感觉得到。当自己感到某人可以为难他人,你总会避免惹他生气;当某人能够给你特殊的利益和奖赏时,你知道与他关系密切是大有益处的;当某人掌握着支配你的职位和责任的权力,你不得不服从规章制度,包括他自己定下的非正式制度。因此,管理者要有能力的和技巧在实践中运用权力,就必须认识到权力的本质。 对于领导的定义有三个要素:第一,权力在领导者和其他成员之间的分配是不对等的。领导者具有影响追随者的能力或者力量。正是靠着权力的影响力,领导者获取人们的信任,把人们吸引到他的身边,使得别人心甘情愿地追随领导者制定的目标;第二,领导是一种艺术创造过程。领导者面对千差万别

领导与管理的关系 到领导也管理的关系,我们首先必须要了解什么是领导,什么又是管理。在这个基础上,才能进一步分析它们两者之间的关系。 所谓领导,就是一种说服别人热诚地追求已经确定目标的能力,是影响和支持他人为了达到目标而富有热情工作的过程。在帮助个体或群体确认目标以及激励和协助他们达到一定目标的过程中,领导是一个重要的因素。 领导者的角色是确立方向,以为领导人是企业、单位、团体当中最先展望未来,最先传播蓝图的人。领导就是将潜力变为现实的催化剂。在所有情况下,领导的根本任务是发现、发展、发挥和丰富组织和组织成员中存在的潜力。领导注重领导者对人的影响和引导,重视人的需要、情感、兴趣、人际关系的社会属性,强调柔性。领导是一种必须依靠下属才能将决策方案转化为现实成果的社会活动。 那么什么是管理呢?管理师靠组织和人员配置来完成已经制定的计划,建立一个组织机构和一系列工作程序来达到计划要求,为每一份工作配上合适的人选,并把计划传达给他们,确立各自的职责,以及建立相互制约的结构来监督实施情况。管理师通过调控和解决问题来保证计划的完成,把运行结果和计划进行详细的对比,最后总结。 从传统理论上讲,管理者的职责无非是计划、组织、协调、人事、控制,管理者的工作就是通过"管理"所属员工实现组织目标。但更多的实践证明,管理者的成功关键在于"领导"。以人为本,激励士气,营造氛围,以有效实现组织和员工双赢的目标,这才是管理者应担当的角色。

举个简单的例子,讲的是《财富人生》节目采访万科集团董事长—王石的一个视频,当时里面就涉及到了许多关于一个领导者,管理者所作出的各种决定。其中,我影响非常深刻的是里面讲到,当年万科集团改造扩股的时候,作为当时总经理的王石完全有机会拿到万科百分之六十以上的公司股份,成为毫无疑问的最大股东,但最后他没有这样做。他说他爱钱,但他这样做的决定是为了万科将来的发展,是从长远角度来考虑这个问题,他最后把他本来可以拥有的股份变成了公司员工控股,使企业有了更好的发展。这样的企业管理者,才是一个优秀的领导,可以引导企业走向成功的领导。 再比如,另一个事例,讲的是当时任微软中国总裁的唐骏,同样是《财富人生》节目,里面讲述了唐骏怎样一步步的走向成功。而在这个过程中,他说,在他被任命为微软公司中国总裁之前的三年多时间里他曾有四次机会到当时微软美国总部的高层任职,而且都比中国总裁的职务要高,但他没有答应,这是一个领带者在他成功道路上对自我成长做出的决定,毫无疑问,这样的决定是正确的。这使他在离开微软之后,在中国打下了自己的一片天地。而另一方面,也提到了他作为一个管理者,领导者,对公司基层员工也是关怀备至,这一点,是一般的管理领导者无法做到的,更何况,微软是这么大一个企业。 由此可见,要作为一个成功的管理者,领导企业或团体走向成功,领导和管理是分不开的,可以说,领导是高层次的管理,管理师低层次的领导,领导中有管理,管理中有领导,领导是柔性的管理,管理师刚性的领导。随着社会化生产,领导是从管理中分化出来,领导活动和管理活动在现实生活中,有着较强的复合性相容性。只有有理的管理与有力的领导结合起来,才能带来满意的效果。

内存时序 一种参数,一般存储在内存条的SPD上。2-2-2-8 4个数字的含义依次为:CAS Latency(简称CL值)内存CAS延迟时间,他是内存的重要参数之一,某些牌子的内存会把CL值印在内存条的标签上。RAS-to-CAS Delay(tRCD),内存行地址传输到列地址的延迟时间。Row-precharge Delay(tRP),内存行地址选通脉冲预充电时间。Row-active Delay(tRAS),内存行地址选通延迟。这是玩家最关注的4项时序调节,在大部分主板的BIOS中可以设定,内存模组厂商也有计划的推出了低于JEDEC认证标准的低延迟型超频内存模组,在同样频率设定下,最低“2-2-2-5”这种序列时序的内存模组确实能够带来比“3-4-4-8”更高的内存性能,幅度在3至5个百分点。 在一些技术文章里介绍内存设置时序参数时,一般数字“A-B-C-D”分别对应的参数是 “CL-tRCD-tRP-tRAS”,现在你该明白“2-3-3-6”是什么意思了吧?!^_^下面就这几个参数及BIOS设置中影响内存性能的其它参数逐一给大家作一介绍: 一、内存延迟时序“CL-tRCD-tRP-tRAS”的设置 首先,需要在BIOS中打开手动设置,在BIOS设置中找到“DRAM Timing Selectable”,BIOS设置中可能出现的其他描述有:Automatic Configuration、DRAM Auto、Timing Selectable、Timing Configuring By SPD等,将其值设为“Menual”(视BIOS的不同可能的选项有:On/Off或Enable/Disable),如果要调整内存时序,应该先打开手动设置,之后会自动出现详细的时序参数列表: Command Per Clock(CPC) 可选的设置:Auto,Enable(1T),Disable(2T)。 Command Per Clock(CPC:指令比率,也有翻译为:首命令延迟),一般还被描述为DRAM Command Rate、CMD Rate等。由于目前的DDR内存的寻址,先要进行P-Bank的选择(通过DIMM上CS片选信号进行),然后才是L-Bank/行激活与列地址的选择。这个参数的含义就是指在P-Bank选择完之后多少时间可以发出具体的寻址的L-Bank/行激活命令,单位是时钟周期。 显然,也是越短越好。但当随着主板上内存模组的增多,控制芯片组的负载也随之增加,过短的命令间隔可能会影响稳定性。因此当你的内存插得很多而出现不太稳定的时间,才需要将此参数调长。目前的大部分主板都会自动设置这个参数。 该参数的默认值为Disable(2T),如果玩家的内存质量很好,则可以将其设置为Enable(1T)。CAS Latency Control(tCL) 可选的设置:Auto,1,1.5,2,2.5,3,3.5,4,4.5。 一般我们在查阅内存的时序参数时,如“3-4-4-8”这一类的数字序列,上述数字序列分别对应的参数是“CL-tRCD-tRP-tRAS”。这个3就是第1个参数,即CL参数。 CAS Latency Control(也被描述为tCL、CL、CAS Latency Time、CAS Timing Delay),CAS latency是“内存读写操作前列地址控制器的潜伏时间”。CAS控制从接受一个指令到执行指令之间的时间。因为CAS主要控制十六进制的地址,或者说是内存矩阵中的列地址,所以它是最为重要的参数,在稳定的前提下应该尽可能设低。 内存是根据行和列寻址的,当请求触发后,最初是tRAS(Activeto Precharge Delay),预充电后,内存才真正开始初始化RAS。一旦tRAS激活后,RAS(Row Address Strobe )开始进行需要数据的寻址。首先是行地址,然后初始化tRCD,周期结束,接着通过CAS访问所需数据的精确十六进制地址。期间从CAS开始到CAS结束就是CAS延迟。所以CAS是找到数据的最后一个步骤,也是内存参数中最重要的。 这个参数控制内存接收到一条数据读取指令后要等待多少个时钟周期才实际执行该指令。同时该参数也决定了在一次内存突发传送过程中完成第一部分传送所需要的时钟周期数。这个参数越小,则内存的速度越快。必须注意部分内存不能运行在较低的延迟,可能会丢失数据,因此在提醒大家把CAS延迟设为2或2.5的同时,如果不稳定就只有进一步提高它了。而且提高延迟能使内存运行在更高的频率,所以需要对内存超频时,应该试着提高CAS延迟。

学习领导理论的体会和认识 21世纪的我们处在一个需要新型领导,也需要培养和研究新型领导的时代。在现代社会中,领导是一个非常宽泛的范畴,我们总是时时刻刻处在领导活动的网络之中,无论是作为领导者还是被领导者,或者是非领导者和未来领导者,学习领导学都是非常必要的,也是时代发展的需要。经过这段时间对领导学的学习,我对领导学有了大概的较全面的了解,包括领导与管理的区别联系、领导学概述、领导者角色分析及领导特质、行为、权变三大理论等。毫无疑问,领导学的学习对我们将来的职业发展有着非常现实的作用,而对于即将踏上社会的我们来说是给了我们努力的方向和指引,这门课让我了解了领导的角色,让我知道我需要培养自己哪些特质,如何去成为被领导赏识的人,又如何在一个团队中去提升和发展自己等等,总之收获颇丰。以下就是我在学习过程中体会最深刻的几点。 一、领导者具备的特质。领导者的特质是影响领导有效性的一个重要因素,专家学者也用了很长一段时间从各个角度来研究领导特质理论,产生了不同的流派,也取得了不少的研究成果。总括关于领导者特质的已有研究结果,与有效领导相关的领导者特质大致可以概括为6个方面:1、生理特征和背景2、智力3、情感和情绪4、驱动力 5、价值与道德 6、领导技能。而余世维《领导商数》中认为领导者有五种特质,1、智力2、监督力 ---- 做一个领导不是要把自己搞得很好,是把下面的人搞好。3、自信 --- 没有人是完美的。要沉得住气。强大的自信使你沉稳。4、主动(积极) ---主动的发现,主动的思考问题,主动的解决问题。5、果决 --- 果决是一种魄力。 从课堂上所接触的案例来看,从杰克·韦尔奇到江南春、唐骏、马云、李开复等,他们虽然都有自己独特的领导风格,但是他们的身上基本涵盖这些领导者的特质。拿唐骏来说,他拥有计算机博士学位,在日美接受了良好的教育,有几项风靡全球的发明;他很多年以来都坚持打篮球,既是爱好也是锻炼,无论如何这使他总保持充沛的精力和饱满的激情;他也曾面对许多生活壁垒,突然失去出国资格、贱卖发明创造、面临被几千人起诉、当有辆“五手车”要卖、不懂法律却开了律所、几次跳槽的非议等;他提倡生活简单,对自己要求“财务零瑕疵”;

浅谈对领导的理解 领导(leadership)是组织行为学(organizational behavior)研究领域中一个非常重要的概念,不同的研究者从不同角度和侧面对其进行了不同的界定。可是,这个在日常工作、生活中经常出现的概念,至今没有统一、权威的定义。有人认为领导是一个过程,有人认为领导是一种关系,有人认为领导就是权力,有人定义领导为影响力。在具有代表性的观点中,Robbins认为,领导是领导者的一种能够影响一个群体实现目标的能力; Northouse则认为,领导就是某一个体影响并带动一组个体实现某一个目标的过程。由此可以看出,二者共同点是:(1)领导具有影响力;(2)领导发生于一定的组织结构中;(3)领导与目标的追求相关联。但不同的是: Robbins认为领导是一种能力,而Northouse则认为领导是一个过程。本文并非试图对领导给出一个“最优”定义,而是从三种不同视角对领导进行分析与评价。 一、权力视角 领导是管理中的高层次活动,是管理的职能之一,它以一定的权力决定和影响社会、组织及其成员的行为,因此,权力是领导的核心要素。具体来说,权力由职权与非职权组成:职权是指领导所处的法律地位和担当的职务使其享有的法定权力,这是领导履行职责、产生影响的重要依据和前提条件,是“制度化的权力”,单向支配,具有强制性,包括

合法权、奖惩权等;非职权是一种与组织的职位无关但与领导领导者个人素质息息相关的权力,主要有专长权、个人魅力、感情权等,这种权力可因领导者的思想、素质与行为的改变而改变,是通过领导者自身努力创造的权力,也可以理解为“权威”,在某种层面上讲它对于领导更加重要。 基于权力视角分析领导,可知领导具有两种类型的权力,那么有权力就一定是领导吗?答案是否定的。组织中有些人虽然依靠上级任命而拥有某种权力,但这仅仅是职权,如果他循规蹈矩,客观地讲,这种人根本不能称之为领导,充其量处作一位强权者;相反,在任何组织中都会存在一些松散不一的圈子,这些圈子中都会有核心人物,与组织中的官员相比,他们无职无权。能够起领导作用更需要一些个人才能和魅力,也就是“权威”。由此可见,某些环境下非职权比职权更加重要,领导要重视非职权的发展,从本质上提高自身的权力。 二、情感视角 从情感上看,领导是一种人际关系,是影响力,是以思想和行为影响他人、使其追随自己完成目标的过程。这个视角着重关注领导的人际技能在处理具体事务中的应用。基于情感视角的领导定义是从领导现象的实际效果来看的,较准确地抓住了领导的本质,但深入考究,或许存在某些问题。 世间万事万物均处于联系之中,你影响我,我影响你,

内存时序设置详解 内容概要 关键词:内存时序参数设置 导言:是否正确地设置了内存时序参数,在很大程度上决定了系统的基本性能。本文详细介绍了内存时序相关参数的基本涵义及设置要点。 与传统的SDRAM相比,DDR(Dual date rate SDRSM:双倍速率SDRAM),最重要的改变是在界面数据传输上,其在时钟信号上升缘与下降缘时各传输一次数据,这使得DDR 的数据传输速率为传统SDRAM的两倍。同样地,对于其标称的如DDR400,DDR333,DDR266数值,代表其工作频率其实仅为那些数值的一半,也就是说DDR400 工作频率为200MHz。 FSB与内存频率的关系 首先请大家看看FSB(Front Side Bus:前端总线)和内存比率与内存实际运行频率的关系。 FSB/MEM比率实际运行频率 1/1 200MHz 1/2 100MHz 2/3 133MHz 3/4 150MHz 3/05 120MHz 5/6 166MHz 7/10 140MHz 9/10 180MHz 对于大多数玩家来说,FSB和内存同步,即1:1是使性能最佳的选择。而其他的设置都是异步的。同步后,内存的实际运行频率是FSBx2,所以,DDR400的内存和200MHz的FSB正好同步。如果你的FSB为240MHz,则同步后,内存的实际运行频率为240MHz x 2 = 480MHz。

FSB与不同速度的DDR内存之间正确的设置关系 强烈建议采用1:1的FSB与内存同步的设置,这样可以完全发挥内存带宽的优势。内存时序设置 内存参数的设置正确与否,将极大地影响系统的整体性能。下面我们将针对内存关于时序设置参数逐一解释,以求能让大家在内存参数设置中能有清晰的思路,提高电脑系统的性能。 涉及到的参数分别为: ?CPC : Command Per Clock ?tCL : CAS Latency Control ?tRCD : RAS to CAS Delay ?tRAS : Min RAS Active Timing ?tRP : Row Precharge Timing ?tRC : Row Cycle Time ?tRFC : Row Refresh Cycle Time ?tRRD : Row to Row Delay(RAS to RAS delay) ?tWR : Write Recovery Time ?……及其他参数的设置 CPC : Command Per Clock 可选的设置:Auto,Enable(1T),Disable(2T)。 Command Per Clock(CPC:指令比率,也有翻译为:首命令延迟),一般还被描述为DRAM Command Rate、CMD Rate等。由于目前的DDR内存的寻址,先要进行P-Bank的选择(通过DIMM上CS片选信号进行),然后才是L-Bank/行激活与列地址的选择。这个参数的含义就是指在P-Bank选择完之后多少时间可以发出具体的寻址的L-Bank/行激活命令,单位是时钟周期。

?什么是OpenCV ?开源C/C++计算机视觉库. ?面向实时应用进行优化. ?跨操作系统/硬件/窗口管理器. ?通用图像/视频载入、存储和获取. ?由中、高层API构成. ?为Intel?公司的Integrated Performance Primitives (IPP) 提供了透明接口. ?特性: ?图像数据操作(分配,释放, 复制, 设定, 转换). ?图像与视频I/O (基于文件/摄像头输入, 图像/视频文件输出). ?矩阵与向量操作与线性代数计算(相乘, 求解, 特征值, 奇异值分解SVD). ?各种动态数据结构(列表, 队列, 集, 树, 图). ?基本图像处理(滤波, 边缘检测, 角点检测, 采样与插值, 色彩转换, 形态操作, 直方图, 图像金字塔). ?结构分析(连接成分, 轮廓处理, 距离转换, 模板匹配, Hough转换, 多边形近似, 线性拟合, 椭圆拟合, Delaunay三角化). ?摄像头标定 (寻找并跟踪标定模板, 标定, 基础矩阵估计, homography估计, 立体匹配). ?动作分析(光流, 动作分割, 跟踪). ?对象辨识 (特征方法, 隐马可夫链模型HMM). ?基本GUI(显示图像/视频, 键盘鼠标操作, 滚动条). ?图像标识 (直线, 圆锥, 多边形, 文本绘图) ?OpenCV 模块: ?cv - OpenCV 主要函数. ?cvaux - 辅助(实验性) OpenCV 函数. ?cxcore - 数据结构与线性代数算法. ?highgui - GUI函数. 资料链接 ?参考手册: ?