第4章-组合逻辑电路(1)

- 格式:doc

- 大小:4.24 MB

- 文档页数:33

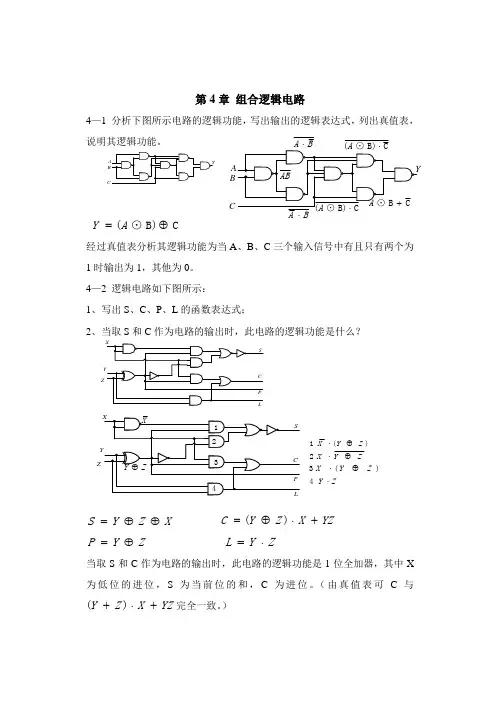

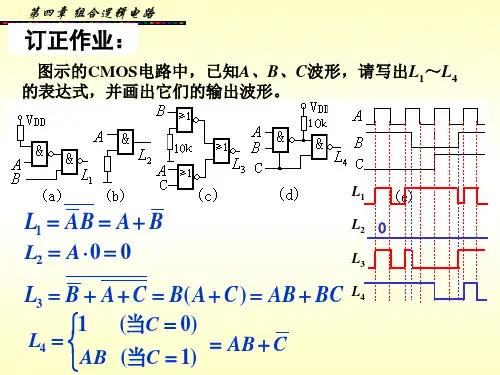

第4章 组合逻辑电路4—1 分析下图所示电路的逻辑功能,写出输出的逻辑表达式,列出真值表,说明其逻辑功能。

C B)⊙(⊕=A Y经过真值表分析其逻辑功能为当A 、B 、C 三个输入信号中有且只有两个为1时输出为1,其他为0。

4—2 逻辑电路如下图所示: 1、写出S 、C 、P 、L 的函数表达式;2、当取S 和C 作为电路的输出时,此电路的逻辑功能是什么?X Z Y S ⊕⊕= YZ X Z Y C +⋅⊕=)(Z Y P ⊕= Z Y L ⋅=当取S 和C 作为电路的输出时,此电路的逻辑功能是1位全加器,其中X 为低位的进位,S 为当前位的和,C 为进位。

(由真值表可C 与YZ X Z Y +⋅+)(完全一致。

)ZB CBA ⋅CB)⊙(⋅A Z)(Z Y X ⊕⋅ZY X ⊕⋅)(Z Y X ⊕⋅ZY ⋅12344—3 下图是由三个全加器构成的电路,试写出其输出1F ,2F ,3F ,4F 的表达式。

Z Y X F ⊕⊕=1 Z Y X F ⋅⊕=)(2Z XY Z XY F +⋅=3 XYZ F =44—4 下图是由3线/8线译码器74LS138和与非门构成的电路,试写出1P 和2P 的表达式,列出真值表,说明其逻辑功能。

ABC C B A m m m m Y Y P +⋅⋅=+=⋅=⋅=70707016543216543212m m m m m m Y Y Y Y Y Y P +++++=⋅⋅+⋅⋅=C B C A B A ++=P1的逻辑功能为当三个输入信号完全一致时输出为1。

P2的逻辑功能为当上输入信号不完全一致时输出为1。

4—5使用74LS138 译码器及少量门电路对三台设备状态进行监控,由不同指示灯进行指示。

当设备正常工作时,指示灯绿灯亮;当有一台设备出故障时,指示灯红灯亮;当有两台设备出故障时,指示灯黄灯亮;当有三台设备出故障时,指示灯红灯和黄灯都亮。

1234解:设输入变量A 、B 、C 分别对应三台设备的状态,0表示故障,1表示正常;输出变量X 、Y 、Z 表示绿、黄、红三个灯的亮灭,0表示灭,1表示亮,根据题意可得真值表如下:设ABC 分别连入74LS138的A 2A 1A 0 由真值表得 42104210Y Y Y Y m m m m Y ⋅⋅⋅=+++=6530Y Y Y Y Z ⋅⋅⋅=4—6 下图3.6是由八选一数据选择器构成的电路,试写出当1G 0G 为各种不同的取值时的输出Y 的表达式。

《数字逻辑电路》笔记(1-10章)第一章:引言1.1 数字系统的基本概念数字信号与模拟信号的区别在电子系统中,信号主要分为数字信号和模拟信号两大类。

数字信号是离散的,只取有限个数值,通常表示为二进制形式( 0和1);而模拟信号则是连续的,可以取任意值,如电压、电流等连续变化的物理量。

数字信号因其抗干扰能力强、易于存储和处理等特点,在现代电子系统中占据主导地位。

数字系统的优势数字系统相较于模拟系统具有显著优势:•准确性:数字信号不易受噪声干扰,能够保持较高的准确性。

•可靠性:数字电路中的元件具有明确的开关状态,减少了因元件老化或环境变化引起的故障。

•灵活性:数字系统易于通过编程或重新配置来改变功能,适应性强。

•集成度高:随着半导体技术的发展,数字电路可以高度集成,减小体积和功耗。

1.2 数制与编码二进制、八进制、十六进制及其转换在计算机科学中,常用的数制有二进制 Base(2)、八进制 Base(8)、十六进制 Base(16)。

二进制是计算机内部信息处理的基础,每位只能表示0或1;八进制和十六进制则用于简化二进制数的表示和计算。

•二进制到十进制的转换:通过将二进制数中的每一位乘以对应的权值 2的幂次方),然后求和得到十进制数。

•十进制到二进制的转换:通过不断除以2,取余数,从下往上排列余数得到二进制数。

•二进制与八进制、十六进制的转换:每三位二进制数对应一位八进制数,每四位二进制数对应一位十六进制数。

BCD码、格雷码等常用编码•BCD码 Binary-Coded(Decimal):一种将十进制数的每一位用四位二进制数表示的编码方式,便于数字显示和计算。

•格雷码( Gray(Code):一种相邻两个数之间只有一位不同的二进制编码方式,常用于减少数字变化时的误差。

1.3 数字逻辑电路的应用领域计算机硬件数字逻辑电路是计算机硬件的基础,包括CPU、内存、I/O接口等部件。

通过逻辑门电路的组合,实现数据的存储、处理和传输。

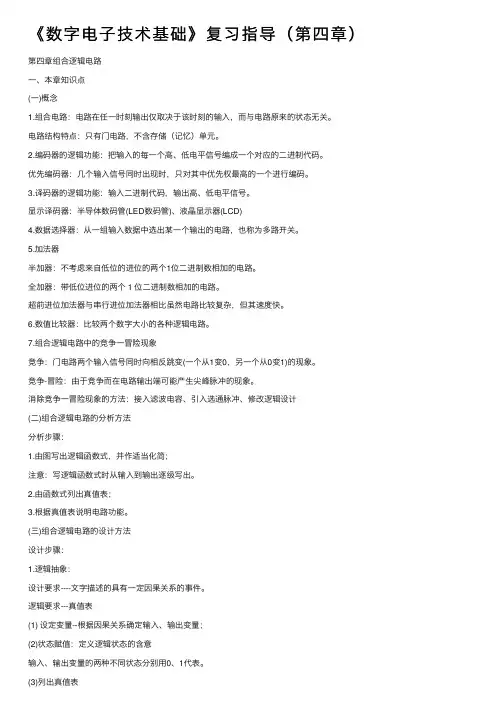

《数字电⼦技术基础》复习指导(第四章)第四章组合逻辑电路⼀、本章知识点(⼀)概念1.组合电路:电路在任⼀时刻输出仅取决于该时刻的输⼊,⽽与电路原来的状态⽆关。

电路结构特点:只有门电路,不含存储(记忆)单元。

2.编码器的逻辑功能:把输⼊的每⼀个⾼、低电平信号编成⼀个对应的⼆进制代码。

优先编码器:⼏个输⼊信号同时出现时,只对其中优先权最⾼的⼀个进⾏编码。

3.译码器的逻辑功能:输⼊⼆进制代码,输出⾼、低电平信号。

显⽰译码器:半导体数码管(LED数码管)、液晶显⽰器(LCD)4.数据选择器:从⼀组输⼊数据中选出某⼀个输出的电路,也称为多路开关。

5.加法器半加器:不考虑来⾃低位的进位的两个1位⼆进制数相加的电路。

全加器:带低位进位的两个 1 位⼆进制数相加的电路。

超前进位加法器与串⾏进位加法器相⽐虽然电路⽐较复杂,但其速度快。

6.数值⽐较器:⽐较两个数字⼤⼩的各种逻辑电路。

7.组合逻辑电路中的竞争⼀冒险现象竞争:门电路两个输⼊信号同时向相反跳变(⼀个从1变0,另⼀个从0变1)的现象。

竞争-冒险:由于竞争⽽在电路输出端可能产⽣尖峰脉冲的现象。

消除竞争⼀冒险现象的⽅法:接⼊滤波电容、引⼊选通脉冲、修改逻辑设计(⼆)组合逻辑电路的分析⽅法分析步骤:1.由图写出逻辑函数式,并作适当化简;注意:写逻辑函数式时从输⼊到输出逐级写出。

2.由函数式列出真值表;3.根据真值表说明电路功能。

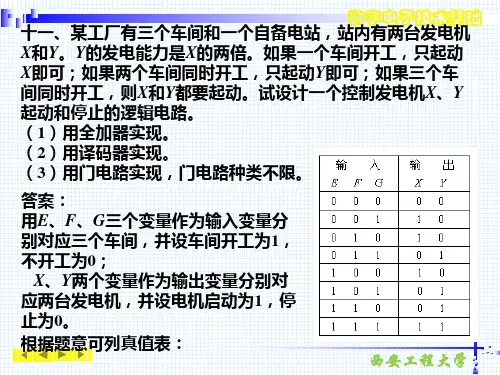

(三)组合逻辑电路的设计⽅法设计步骤:1.逻辑抽象:设计要求----⽂字描述的具有⼀定因果关系的事件。

逻辑要求---真值表(1) 设定变量--根据因果关系确定输⼊、输出变量;(2)状态赋值:定义逻辑状态的含意输⼊、输出变量的两种不同状态分别⽤0、1代表。

(3)列出真值表2.由真值表写出逻辑函数式真值表→函数式,有时可省略。

3.选定器件的类型可选⽤⼩规模门电路,中规模常⽤组合逻辑器件或可编程逻辑器件。

4.函数化简或变换式(1)⽤门电路进⾏设计:从真值表----卡诺图/公式法化简。

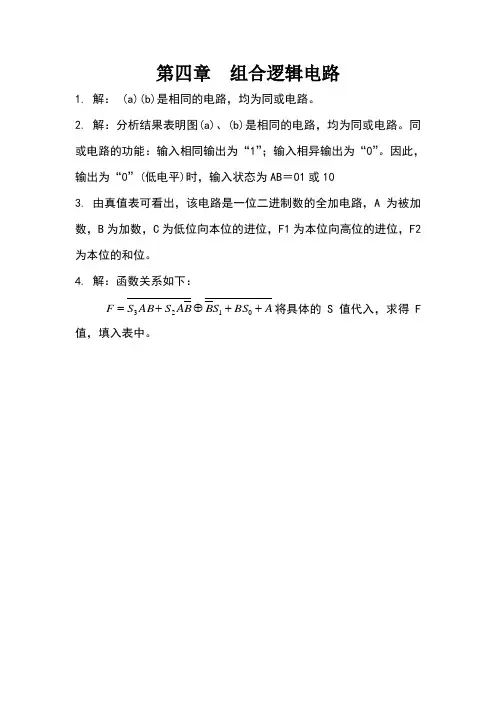

第四章组合逻辑电路1. 解: (a)(b)是相同的电路,均为同或电路。

2. 解:分析结果表明图(a)、(b)是相同的电路,均为同或电路。

同或电路的功能:输入相同输出为“1”;输入相异输出为“0”。

因此,输出为“0”(低电平)时,输入状态为AB=01或103. 由真值表可看出,该电路是一位二进制数的全加电路,A为被加数,B为加数,C为低位向本位的进位,F1为本位向高位的进位,F2为本位的和位。

4. 解:函数关系如下:ABSF+⊕=++ABSSSABB将具体的S值代入,求得F 312值,填入表中。

A A FB A B A B A A F B A B A A F A A F AB AB F B B A AB F AB B A B A B A AB F B A A AB F B A B A B A F B A AB AB B A B A F B B A B A B A B A B A B A F AB BA A A B A A B A F F B A B A F B A B A F A A F S S S S =⊕==+==+⊕===+⊕===⊕===⊕===+⊕===+=+⊕===⊕==+==⊕==Θ=+=+⊕===+++=+⊕===+=⊕===⊕==+=+⊕==+=+⊕===⊕==01111111011010110001011101010011000001110110)(01010100101001110010100011000001235. (1)用异或门实现,电路图如图(a)所示。

(2) 用与或门实现,电路图如图(b)所示。

6. 解因为一天24小时,所以需要5个变量。

P变量表示上午或下午,P=0为上午,P=1为下午;ABCD表示时间数值。

真值表如表所示。

利用卡诺图化简如图(a)所示。

化简后的函数表达式为D C A P D B A P C B A P A P DC A PD B A P C B A P A P F =+++=用与非门实现的逻辑图如图(b)所示。

矿产资源开发利用方案编写内容要求及审查大纲

矿产资源开发利用方案编写内容要求及《矿产资源开发利用方案》审查大纲一、概述

㈠矿区位置、隶属关系和企业性质。

如为改扩建矿山, 应说明矿山现状、

特点及存在的主要问题。

㈡编制依据

(1简述项目前期工作进展情况及与有关方面对项目的意向性协议情况。

(2 列出开发利用方案编制所依据的主要基础性资料的名称。

如经储量管理部门认定的矿区地质勘探报告、选矿试验报告、加工利用试验报告、工程地质初评资料、矿区水文资料和供水资料等。

对改、扩建矿山应有生产实际资料, 如矿山总平面现状图、矿床开拓系统图、采场现状图和主要采选设备清单等。

二、矿产品需求现状和预测

㈠该矿产在国内需求情况和市场供应情况

1、矿产品现状及加工利用趋向。

2、国内近、远期的需求量及主要销向预测。

㈡产品价格分析

1、国内矿产品价格现状。

2、矿产品价格稳定性及变化趋势。

三、矿产资源概况

㈠矿区总体概况

1、矿区总体规划情况。

2、矿区矿产资源概况。

3、该设计与矿区总体开发的关系。

㈡该设计项目的资源概况

1、矿床地质及构造特征。

2、矿床开采技术条件及水文地质条件。