第四章 组合逻辑电路

- 格式:docx

- 大小:249.05 KB

- 文档页数:7

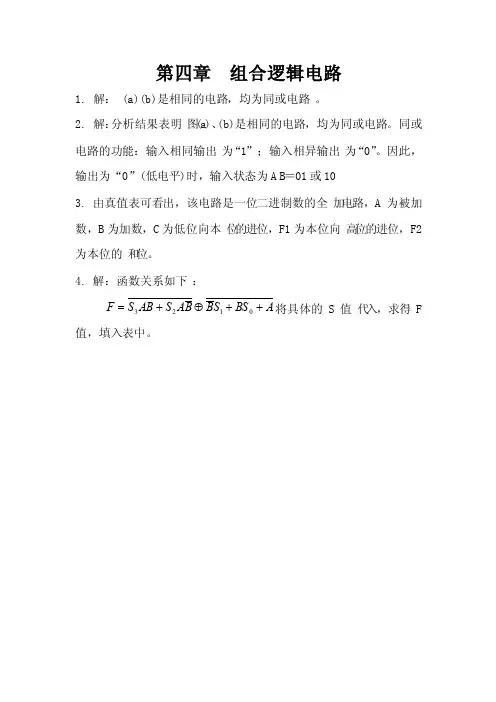

第四章组合逻辑电路1. 解: (a)(b)是相同的电路,均为同或电路。

2. 解:分析结果表明图(a)、(b)是相同的电路,均为同或电路。

同或电路的功能:输入相同输出为“1”;输入相异输出为“0”。

因此,输出为“0”(低电平)时,输入状态为AB=01或103. 由真值表可看出,该电路是一位二进制数的全加电路,A为被加数,B为加数,C为低位向本位的进位,F1为本位向高位的进位,F2为本位的和位。

4. 解:函数关系如下:SF++⊕=+ABSABS BABS将具体的S值代入,求得F 312值,填入表中。

A A FB A B A B A A F B A B A A F A A F AB AB F B B A AB F AB B A B A B A AB F B A A AB F B A B A B A F B A AB AB B A B A F B B A B A B A B A B A B A F AB BA A A B A A B A F F B A B A F B A B A F A A F S S S S =⊕==+==+⊕===+⊕===⊕===⊕===+⊕===+=+⊕===⊕==+==⊕==Θ=+=+⊕===+++=+⊕===+=⊕===⊕==+=+⊕==+=+⊕===⊕==01111111011010110001011101010011000001110110)(01010100101001110010100011000001235. (1)用异或门实现,电路图如图(a)所示。

(2) 用与或门实现,电路图如图(b)所示。

6. 解因为一天24小时,所以需要5个变量。

P变量表示上午或下午,P=0为上午,P=1为下午;ABCD表示时间数值。

真值表如表所示。

利用卡诺图化简如图(a)所示。

化简后的函数表达式为D C A P D B A P C B A P A P DC A PD B A P C B A P A P F =+++=用与非门实现的逻辑图如图(b )所示。

第四章组合逻辑电路一、填空题1、根据逻辑功能的不同特点,可将数字电路分成两大类:一类称为组合逻辑电路,另一类称为电路。

2、分析组合逻辑电路时,一般根据图写出逻辑函数表达式。

3、用门电路设计组合逻辑电路时,通常根据设计要求列出,再写出输出逻辑函数表达式。

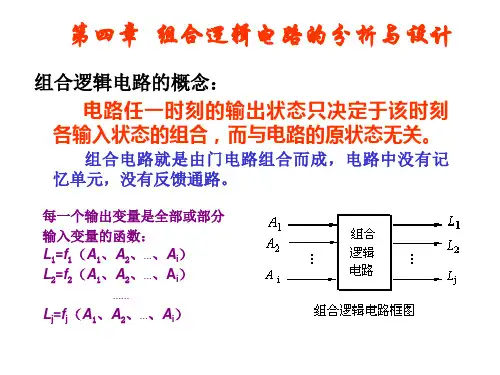

4、组合逻辑电路的特点是输出状态只与,与电路原来的状态,其基本单元电路是。

5、译码器按功能的不同分为三种,,。

6、是编码的逆过程。

7、数据选择器是在的作用下,从中选择作为输出的组合逻辑电路。

8、2n选1数据选择器有位地址码。

9、8选1数据选择器在所有输入数据都为1时,其输出标准与-或表达式共有个最小项。

如所有输入数据都为0时,则输出为。

10、全加器有3个输入端,它们分别为,,和;输出端有2个,分别为、。

11、半导体数码显示器的内部接法有两种形式:共接法和共接法。

12、BCD-七段译码器/驱动器输出高电平有效时,用来驱动极数码管;如输出低电平有效时,用来驱动极数码管。

13、数据选择器只能用来实现输出逻辑函数,而二进制译码器不但可用来实现输出逻辑函数,而且还可用来实现输出逻辑函数。

14、在组合逻辑电路中,消除竞争冒险现象的主要方法有,,,。

二、判断题()1、模拟量是连续的,数字量是离散的,所以模拟电路的精度要高于数字电路。

()2、数据选择器是将一个输入数据分配到多个指定输出端的电路。

()3、数值比较器是用于比较两组二进制数大小或相等的电路。

()4、优先编码器只对多个输入编码信号中优先权最高的信号进行编码。

()5、加法器是用于对两组二进制数进行比较的电路。

()6、具有记忆功能的电路不是组合逻辑电路。

()7、译码器的作用就是将输入的二进制代码译成特定的信号输出。

()8、全加器只用于对两个一位二进制数相加。

()9、数据选择器根据地址码的不同从多路输入数据中选择其中一路输出。

()10、在任何时刻,电路的输出状态只取决于该时刻的输入,而与该时刻之前的电路状态无关的逻辑电路,称为组合逻辑电路。

《数字电⼦技术基础》复习指导(第四章)第四章组合逻辑电路⼀、本章知识点(⼀)概念1.组合电路:电路在任⼀时刻输出仅取决于该时刻的输⼊,⽽与电路原来的状态⽆关。

电路结构特点:只有门电路,不含存储(记忆)单元。

2.编码器的逻辑功能:把输⼊的每⼀个⾼、低电平信号编成⼀个对应的⼆进制代码。

优先编码器:⼏个输⼊信号同时出现时,只对其中优先权最⾼的⼀个进⾏编码。

3.译码器的逻辑功能:输⼊⼆进制代码,输出⾼、低电平信号。

显⽰译码器:半导体数码管(LED数码管)、液晶显⽰器(LCD)4.数据选择器:从⼀组输⼊数据中选出某⼀个输出的电路,也称为多路开关。

5.加法器半加器:不考虑来⾃低位的进位的两个1位⼆进制数相加的电路。

全加器:带低位进位的两个 1 位⼆进制数相加的电路。

超前进位加法器与串⾏进位加法器相⽐虽然电路⽐较复杂,但其速度快。

6.数值⽐较器:⽐较两个数字⼤⼩的各种逻辑电路。

7.组合逻辑电路中的竞争⼀冒险现象竞争:门电路两个输⼊信号同时向相反跳变(⼀个从1变0,另⼀个从0变1)的现象。

竞争-冒险:由于竞争⽽在电路输出端可能产⽣尖峰脉冲的现象。

消除竞争⼀冒险现象的⽅法:接⼊滤波电容、引⼊选通脉冲、修改逻辑设计(⼆)组合逻辑电路的分析⽅法分析步骤:1.由图写出逻辑函数式,并作适当化简;注意:写逻辑函数式时从输⼊到输出逐级写出。

2.由函数式列出真值表;3.根据真值表说明电路功能。

(三)组合逻辑电路的设计⽅法设计步骤:1.逻辑抽象:设计要求----⽂字描述的具有⼀定因果关系的事件。

逻辑要求---真值表(1) 设定变量--根据因果关系确定输⼊、输出变量;(2)状态赋值:定义逻辑状态的含意输⼊、输出变量的两种不同状态分别⽤0、1代表。

(3)列出真值表2.由真值表写出逻辑函数式真值表→函数式,有时可省略。

3.选定器件的类型可选⽤⼩规模门电路,中规模常⽤组合逻辑器件或可编程逻辑器件。

4.函数化简或变换式(1)⽤门电路进⾏设计:从真值表----卡诺图/公式法化简。

第四章组合逻辑电路1. 解: (a)(b)是相同的电路,均为同或电路。

2. 解:分析结果表明图(a)、(b)是相同的电路,均为同或电路。

同或电路的功能:输入相同输出为“1”;输入相异输出为“0”。

因此,输出为“0”(低电平)时,输入状态为AB=01或103. 由真值表可看出,该电路是一位二进制数的全加电路,A为被加数,B为加数,C为低位向本位的进位,F1为本位向高位的进位,F2为本位的和位。

4. 解:函数关系如下:ABSF+⊕=++ABSSSABB将具体的S值代入,求得F 312值,填入表中。

A A FB A B A B A A F B A B A A F A A F AB AB F B B A AB F AB B A B A B A AB F B A A AB F B A B A B A F B A AB AB B A B A F B B A B A B A B A B A B A F AB BA A A B A A B A F F B A B A F B A B A F A A F S S S S =⊕==+==+⊕===+⊕===⊕===⊕===+⊕===+=+⊕===⊕==+==⊕==Θ=+=+⊕===+++=+⊕===+=⊕===⊕==+=+⊕==+=+⊕===⊕==01111111011010110001011101010011000001110110)(01010100101001110010100011000001235. (1)用异或门实现,电路图如图(a)所示。

(2) 用与或门实现,电路图如图(b)所示。

6. 解因为一天24小时,所以需要5个变量。

P变量表示上午或下午,P=0为上午,P=1为下午;ABCD表示时间数值。

真值表如表所示。

利用卡诺图化简如图(a)所示。

化简后的函数表达式为D C A P D B A P C B A P A P DC A PD B A P C B A P A P F =+++=用与非门实现的逻辑图如图(b)所示。

第三章 组合逻辑电路

一. 填空题

1. 74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=100时,输出 01234567Y Y Y Y Y Y Y Y 应为 11101111 。

2. 74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=101时,输出 01234567Y Y Y Y Y Y Y Y 应为 1101111 。

3. 数字电路按照是否有记忆功能通常可分为两类: 组合逻辑电路 和 时序逻辑电路。

。

4. 16选一数据选择器,其地址输入端有 16 个

5. 8选一数据选择器有___8______条地址控制线。

二.选择题

1. 在下列逻辑电路中,不是组合逻辑电路的是 D

A.译码器

B.编码器

C.全加器

D.寄存器 2. 三十二路数据选择器,其地址输入端有 C 个 A .16 B .2 C .5 D . 8 3. 数据选择器是具有 A 通道的器件 A.多输入单输出 B.多输入多输出 C.单输入单输出 D.单输入多输出

4. 欲对全班54个同学以二进制代码编码表示,最少需要二进制的位数是(B )

A. 5

B.6

C. 10 D . 53

5. 已知A 、B 为逻辑门的输入端,F 为输出端,其输入、输出波形如图1所示。

试判断这是哪种逻辑门的波形 D 。

A

B

F

图1

A.与非门

B. 与门

C. 或非门 D . 或门

三.简答和计算题

1. 将逻辑函数F AB AC ABC

=++转化为与非-与非表达式,并画出只由

与非门实现的逻辑电路图。

2. 将逻辑函数Y=AB+BC+CA化为与非-与非形式,并画出只由与非门实现的逻辑电路图。

3. 用8选1数据选择器74HC151实现函数F AC ABC ABC ABC

=+++。

4. 用8选1数据选择器74HC151实现逻辑函数F AC AB ABC

=++。

5. 用8选1数据选择器实现函数F=AC+ABC+ABC。

6. 用译码器74HC138实现函数F AC ABC ABC =++。

要求写出设计过程。

7. 译码器74HC138的逻辑符号如图8所示。

用译码器74HC138实现逻辑函数F AC ABC AB =++。

要求写出设计过程。

8. 某生产线有3部车床A、B、C,其中A和B的功率相等,C的功率是A的2倍。

这些车床由2台发电机X和Y供电,发电机X的最大功率等于车床A的功率,发电机Y 的功率是X的3倍。

要求设计一个逻辑电路,能够根据车床的起动和关闭信号,以最节约的方式起、停发电机。

要求:写出详细的设计过程和用与非门、非门实现的电路图。

9.设计电路完成以下功能:设有一个主裁判和两个边裁对足球赛的判罚进行表决,即三人中有两个或两个以上同意时,则判罚有效,否则判罚无效。

要求写出详细的设计过程并用与非门实现电路图。

10.写出如图所示电路中12Y Y 、的逻辑表达式,并画出真值表,说明电路的逻辑功能。

图T3.2

11、设计一个组合逻辑电路,它的输入与输出之间的逻辑关系如下表给出。

表中

没有给出的输入变量组合,在工作中不会出现。

要求全部电路用与非门组成。

12、设计一个组合逻辑电路,它的输入与输出之间的逻辑关系如下表给出。

表中

没有给出的输入变量组合,在工作中不会出现。

要求全部电路用与非门组成。

13、画出用3线—8线译码器74HC138(如图所示)和门电路产生如下多输出逻辑函数的逻辑图。

1Y AC =

2Y A BC AB C BC =⋅+⋅+ 3Y B C ABC =⋅+

14、用8选1数据选择器74HC151(如图所示)实现逻辑函数:

=+⋅++⋅

Y A C D A B C D B C B C D

四、画图题

2、在图示门电路中,已知输入端A、B的电压波形,试画出各输出端的电压波形。

Y1

Y2。