Verilog项目六

- 格式:ppt

- 大小:808.50 KB

- 文档页数:8

复旦微fpga开发流程复旦微FPGA开发流程引言本文将详细阐述复旦微FPGA开发流程,帮助创作者了解并掌握该流程,以促进创作效率和成果质量的提高。

准备工作在开始复旦微FPGA开发流程之前,需要进行一些准备工作: - 下载并安装FPGA开发工具 - 确定项目需求和目标 - 了解复旦微FPGA 的基本原理和特点开发流程概述复旦微FPGA开发流程可以大致划分为以下几个阶段:阶段一:项目规划和设计1.确定项目需求和目标2.设计FPGA逻辑电路结构3.编写时序约束阶段二:编码和仿真1.使用Verilog或VHDL编写逻辑电路代码2.进行功能仿真和时序分析3.优化电路结构和性能阶段三:综合和布局布线1.将逻辑电路代码进行综合2.进行布局布线,生成网表文件3.进行时序和功耗分析,优化设计阶段四:生成比特流文件1.生成比特流文件2.烧录比特流文件到FPGA中3.进行验证和完善阶段五:调试和优化1.进行功能调试和性能优化2.可选:进行封装和集成设计3.进行仿真、验证和测试结论复旦微FPGA开发流程是一个系统而严谨的过程,通过遵循该流程,创作者能够更高效地开发自己的项目,并取得优秀的成果。

希望本文能对创作者在复旦微FPGA开发过程中提供有益的指导和帮助。

以上就是复旦微FPGA开发流程的详细说明,希望对您有所帮助!复旦微FPGA开发流程(续)开发流程详述在前文的基础上,我们将详细介绍每个阶段的流程和步骤。

阶段一:项目规划和设计1.确定项目需求和目标–确定项目的功能要求、性能指标等。

–确定项目的时间和资源限制。

2.设计FPGA逻辑电路结构–根据项目需求,构思和设计逻辑电路的结构。

–使用Verilog或VHDL等硬件描述语言来描述电路。

3.编写时序约束–根据项目的时序要求,编写时序约束文件。

–时序约束可指定输入输出延迟、时钟频率等信息。

阶段二:编码和仿真1.使用Verilog或VHDL编写逻辑电路代码–根据设计的逻辑电路结构,编写Verilog或VHDL代码。

Verilog Task语法什么是Verilog Task在Verilog中,Task是一种用于执行特定功能的可重用代码块。

它类似于函数,但有一些区别。

Task允许对信号进行并行操作,并且可以在任何地方调用。

它是一种组织代码和模块化设计的好方法。

Task的语法Task使用task关键字定义,并使用endtask关键字结束。

以下是Task的基本语法:task task_name;// 变量声明// 任务体endtask其中,task_name是任务的名称,可以根据需要自定义。

任务体是任务执行的实际代码部分。

Task的参数Task可以有零个或多个参数。

参数允许将数据传递给任务,并在任务内部使用。

参数在任务定义时声明,并在调用时传递。

以下是一个带有参数的Task示例:task add_numbers(input [7:0] a, input [7:0] b, output [15:0] sum);sum = a + b;endtask在上面的示例中,我们定义了一个名为add_numbers的Task,它接受两个8位输入参数a和b,并返回一个16位输出sum。

任务体中计算了a和b的和,并将结果存储到sum中。

Task的调用要调用Task,只需提供所需的参数即可。

以下是调用上述add_numbers Task的示例:reg [7:0] num1 = 8'h12;reg [7:0] num2 = 8'h34;wire [15:0] result;// 调用add_numbers Taskadd_numbers(num1, num2, result);在上面的示例中,我们声明了两个8位的寄存器num1和num2,并将其初始化为十六进制数12和34。

然后,我们声明了一个16位的wire result,用于接收Task 返回的结果。

最后,我们调用了add_numbers Task,并将num1、num2和result 作为参数传递。

verilog条件编译# Verilog条件编译指南Verilog,作为一种硬件描述语言,广泛应用于数字电路设计、系统建模以及ASIC/FPGA开发中。

在实际项目开发过程中,我们经常需要根据不同的设计需求或目标平台进行代码的条件编译。

Verilog提供了预处理指令(Preprocessing Directives)来支持这一特性,使得开发者能够灵活地控制代码片段的编译行为。

## 1. 条件编译的基本概念条件编译是指在源代码编译阶段,根据特定条件判断是否包含某段代码进行编译。

在Verilog中,主要通过`ifdef`,`ifndef`,`else`和`endif`等预处理指令实现这一功能。

- `ifdef`:如果定义了某个宏,则包含其后的代码块。

- `ifndef`:如果未定义某个宏,则包含其后的代码块。

- `else`:与前面的`ifdef`或`ifndef`配合使用,当条件不满足时,包含其后的代码块。

- `endif`:结束一个条件编译块。

例如:```verilog`ifdef DEBUG_MODE// 在DEBUG_MODE被定义的情况下,以下代码会被编译initial begin$display("Entering debug mode...");end`else// 在DEBUG_MODE未被定义的情况下,以下代码会被编译initial begin$display("Debug mode is not enabled.");end`endif```## 2. 定义宏在Verilog中,我们可以通过`define指令来定义宏,如:```verilog`define DEBUG_MODE```一旦定义了这个宏,在后续的代码中就可以根据`DEBUG_MODE`是否存在来进行条件编译。

## 3. 应用场景条件编译在Verilog中的应用场景十分广泛,例如:- 根据不同的设计模式(如仿真模式、综合模式)选择性地编译部分代码;- 根据目标FPGA或ASIC器件的特点选择不同的模块实现;- 控制日志输出级别,如在调试模式下输出详细信息,在产品模式下仅输出关键信息。

对于fpga 核心板设计项目的理解-回复[对于FPGA核心板设计项目的理解]在当今科技快速发展的时代,硬件设计领域的需求也越来越多。

在这个领域中,FPGA(Field Programmable Gate Array)核心板设计项目变得非常重要。

FPGA核心板设计项目具有很高的技术含量,需要经历一系列步骤,包括需求分析、架构设计、电路设计、FPGA编程以及测试验证等。

本文将一步一步回答关于FPGA核心板设计项目的一些常见问题。

1. 什么是FPGA核心板?FPGA核心板是一种集成电路板,上面搭载了一个或多个FPGA芯片,以及其他必要的电路和接口。

FPGA是一种可编程逻辑设备,可以通过配置来实现不同的电路功能。

2. FPGA核心板设计项目的需求分析在开始设计FPGA核心板之前,首先需要进行需求分析。

这包括确定项目的目标和功能,并与客户进行沟通,详细了解他们的需求和期望。

在这一阶段,还需要考虑到可行性、性能、资源需求、成本以及可能的扩展性等因素。

3. FPGA核心板设计项目的架构设计在需求分析完成后,下一步是进行架构设计。

架构设计是指确定FPGA核心板上各个模块之间的连接和通信方式。

这包括选择适当的总线协议、外设接口和存储器等。

同时,还需要考虑到时序要求、功耗、电磁兼容等方面的设计考虑。

4. FPGA核心板设计项目的电路设计在确定了架构设计之后,需要进行电路设计。

这包括选择合适的电路元件,如时钟、存储器、转换器等,并进行电路原理图和布局设计。

此外,还需要进行信号完整性分析,以确保电路设计满足时序、噪声和干扰等需求。

5. FPGA核心板设计项目的FPGA编程在完成电路设计后,接下来是对FPGA芯片进行编程。

FPGA编程是指使用HDL(硬件描述语言)来描述和实现FPGA的逻辑功能。

常见的HDL 包括VHDL和Verilog。

在这一阶段,需要根据架构设计和电路设计来编写逻辑代码,并进行功能仿真和时序分析等验证工作。

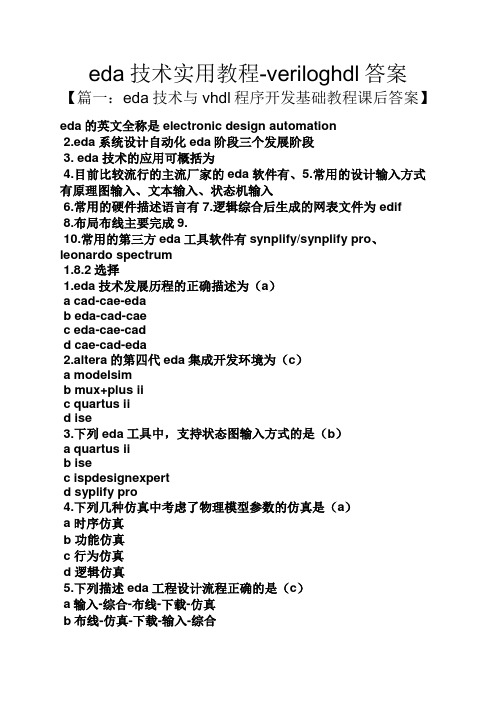

eda技术实用教程-veriloghdl答案【篇一:eda技术与vhdl程序开发基础教程课后答案】eda的英文全称是electronic design automation2.eda系统设计自动化eda阶段三个发展阶段3. eda技术的应用可概括为4.目前比较流行的主流厂家的eda软件有、5.常用的设计输入方式有原理图输入、文本输入、状态机输入6.常用的硬件描述语言有7.逻辑综合后生成的网表文件为 edif8.布局布线主要完成9.10.常用的第三方eda工具软件有synplify/synplify pro、leonardo spectrum1.8.2选择1.eda技术发展历程的正确描述为(a)a cad-cae-edab eda-cad-caec eda-cae-cadd cae-cad-eda2.altera的第四代eda集成开发环境为(c)a modelsimb mux+plus iic quartus iid ise3.下列eda工具中,支持状态图输入方式的是(b)a quartus iib isec ispdesignexpertd syplify pro4.下列几种仿真中考虑了物理模型参数的仿真是(a)a 时序仿真b 功能仿真c 行为仿真d 逻辑仿真5.下列描述eda工程设计流程正确的是(c)a输入-综合-布线-下载-仿真b布线-仿真-下载-输入-综合c输入-综合-布线-仿真-下载d输入-仿真-综合-布线-下载6.下列编程语言中不属于硬件描述语言的是(d)a vhdlb verilogc abeld php1.8.3问答1.结合本章学习的知识,简述什么是eda技术?谈谈自己对eda技术的认识?答:eda(electronic design automation)工程是现代电子信息工程领域中一门发展迅速的新技术。

2.简要介绍eda技术的发展历程?答:现代eda技术是20世纪90年代初从计算机辅助设计、辅助制造和辅助测试等工程概念发展而来的。

第1篇1. FPGA是什么?FPGA(现场可编程门阵列)是一种可编程逻辑器件,它可以根据用户的需求进行编程,实现各种数字电路功能。

FPGA具有高灵活性、高集成度、低功耗等优点,广泛应用于通信、工业控制、消费电子等领域。

答案:FPGA是一种可编程逻辑器件,可以根据用户需求进行编程,实现各种数字电路功能。

2. VHDL和Verilog的区别是什么?VHDL和Verilog都是硬件描述语言,用于描述数字电路和系统。

两者在语法和功能上存在一些差异:- VHDL是一种强类型语言,具有丰富的数据类型和操作符,易于编写复杂的数字电路描述。

- Verilog是一种弱类型语言,数据类型较为简单,但具有简洁的语法,便于快速编写代码。

答案:VHDL和Verilog的区别在于数据类型和语法,VHDL是强类型语言,Verilog 是弱类型语言。

3. 什么是FPGA的时钟域交叉问题?FPGA的时钟域交叉问题是指当多个时钟域的信号进行交互时,可能会出现信号竞争、数据丢失等现象,导致系统性能下降或功能失效。

答案:FPGA的时钟域交叉问题是指当多个时钟域的信号进行交互时,可能会出现信号竞争、数据丢失等现象。

4. 如何处理FPGA的时序问题?处理FPGA的时序问题主要包括以下几个方面:- 设计合理的时钟树,确保时钟信号在各个模块之间稳定传播。

- 合理设置时钟分频、倍频等参数,避免时钟抖动。

- 优化模块设计,减少信号路径长度,降低信号传播延迟。

- 进行时序仿真,确保满足设计要求。

答案:处理FPGA的时序问题主要包括设计合理的时钟树、设置时钟参数、优化模块设计和进行时序仿真。

5. FPGA的配置过程是怎样的?FPGA的配置过程主要包括以下几个步骤:- 编写配置文件:使用VHDL或Verilog等硬件描述语言编写配置文件,描述FPGA 内部电路的结构和功能。

- 编译配置文件:使用FPGA厂商提供的编译工具对配置文件进行编译,生成门级网表。

Testbench⽂件编写纪要(Verilog)之前在使⽤Verilog做FPGA项⽬中、以及其他⼀些不同的场合下,零散的写过⼀些练⼿性质的testbench⽂件,开始⼏次写的时候,每次都会因为⼀些基本的东西没记住、写的很不熟练,后⾯写的时候稍微熟练了⼀点、但是整体编写下来⽐较零碎不成体系,所以在这⾥简要记录⼀下⼀般情况下、针对⼩型的verilog模块进⾏测试时所需要使⽤到的testbench⽂件的编写要点。

本⽂主要参考了在⽹上找到的Lattice公司的“A Verilog HDL Test Bench Primer”⼿册中的有关内容。

谢谢!模块实例化、reg&wire声明、initial和always块的使⽤需要测试的模块(Verilog-module)被称为DUT(Design Under Test),在testbench中需要对⼀个或者多个DUT进⾏实例化。

Testbench中的顶层module不需要定义输⼊和输出。

Testbench中连接到DUT instance的输⼊的为reg类型、连接到DUT instance的输出的为wire类型。

对于DUT的inout类型变量,在testbench中需要分别使⽤reg、wire类型的变量进⾏调⽤。

例如,对于下⾯这样⼀个待测试module:module bidir_infer (DATA, READ_WRITE);input READ_WRITE ;inout [1:0] DATA ;reg [1:0] LATCH_OUT ;always @ (READ_WRITE or DATA) beginif (READ_WRITE == 1)LATCH_OUT <= DATA;endassign DATA = (READ_WRITE == 1) ? 2'bZ : LATCH_OUT;endmodule为其设计的testbench⽂件可以是:module test_bidir_ver;reg read_writet;reg [1:0] data_in;wire [1:0] datat, data_out;bidir_infer uut (datat, read_writet);assign datat = (read_writet == 1) ? data_in : 2'bZ;assign data_out = (read_writet == 0) ? datat : 2'bZ;initial beginread_writet = 1;data_in = 11;#50 read_writet = 0;endendmodule和普通的Verilog模块中⼀样、使⽤assign对wire类型的变量进⾏赋值。

FPGA verilog课程设计报告一、教学目标本课程旨在通过FPGA Verilog的学习,让学生掌握数字电路设计的基本原理和方法,学会使用Verilog硬件描述语言进行数字电路设计和仿真。

具体目标如下:1.理解FPGA的基本原理和结构。

2.掌握Verilog语言的基本语法和编程技巧。

3.熟悉数字电路的设计方法和流程。

4.能够使用Verilog语言编写简单的数字电路模块。

5.能够进行FPGA的配置和编程。

6.能够使用FPGA开发工具进行数字电路的仿真和测试。

情感态度价值观目标:1.培养学生的创新意识和团队合作精神。

2.增强学生对新技术的敏感性和学习兴趣。

3.培养学生对工程实践的热爱和责任感。

二、教学内容本课程的教学内容主要包括FPGA的基本原理和结构、Verilog语言的基本语法和编程技巧、数字电路的设计方法和流程。

具体安排如下:第1-2课时:FPGA的基本原理和结构1.FPGA的定义和发展历程。

2.FPGA的内部结构和组成。

3.FPGA的配置和编程方法。

第3-4课时:Verilog语言的基本语法和编程技巧1.Verilog语言的基本数据类型和操作符。

2.Verilog语言的逻辑表达式和语句。

3.Verilog语言的模块结构和参数传递。

第5-6课时:数字电路的设计方法和流程1.数字电路的设计原则和技巧。

2.数字电路的设计流程和步骤。

3.数字电路的仿真和测试方法。

三、教学方法本课程采用讲授法、案例分析法和实验法相结合的教学方法。

1.讲授法:通过讲解和演示,让学生掌握FPGA和Verilog的基本知识和技巧。

2.案例分析法:通过分析具体的数字电路设计案例,让学生熟悉设计方法和流程。

3.实验法:通过动手实验,让学生亲手配置FPGA、编写Verilog代码并进行仿真测试,提高学生的实际操作能力。

四、教学资源1.教材:《FPGA Verilog设计与实践》。

2.参考书:《数字电路与FPGA设计入门》、《Verilog HDL入门与提高》。

vivado中systemverilog混合编译在Vivado中,SystemVerilog混合编译是指将SystemVerilog代码与Verilog代码一起编译和仿真。

Vivado支持这种混合编译,以便您可以在同一个项目中使用两种语言。

以下是混合编译的一般步骤:1. 创建项目:首先,创建一个新的Vivado项目。

这可以通过打开Vivado软件并创建一个新的项目文件来实现。

2. 添加文件:在项目中添加所需的Verilog和SystemVerilog文件。

您可以将文件直接拖放到项目浏览器中,或者通过菜单栏中的“File”>“Add”>“File”来添加。

3. 编写代码:在Verilog和SystemVerilog文件中编写代码。

请注意,混合编译的代码应该遵循一定的规范,以便Vivado可以正确地识别和处理两种语言。

4. 编译和仿真:在Vivado中编译项目。

可以通过菜单栏中的“Run”>“Compile”来执行编译操作。

编译完成后,您可以使用Vivado提供的仿真工具进行仿真。

5. 分析结果:在仿真过程中,您可以查看波形、报告和其它输出文件,以分析设计的性能和正确性。

以下是一些建议,以确保混合编译的顺利进行:-避免在同一个模块中混合使用Verilog和SystemVerilog代码。

尽量将Verilog代码和SystemVerilog代码分别放在不同的模块中。

-使用Vivado提供的预处理器指令来区分Verilog和SystemVerilog代码。

例如,使用``来声明一个模块为SystemVerilog模块。

-确保SystemVerilog模块中的异常处理和监控功能正确实现,以避免编译错误。

-熟悉Vivado的编译器和仿真器,以便在混合编译环境中正确地使用它们。

总之,在Vivado中进行SystemVerilog混合编译需要遵循一定的规范和技巧。

通过遵循这些规范和技巧,您可以充分利用Verilog和SystemVerilog的优势,提高设计开发效率。